Матричные вычислительные системы.

Основой матричных систем является матричный процессор.

Матричный процессор представляет собой «матрицу», связанных элементарных идентичных процессоров, управляемых одним потоком команд (рисунок 12.39).

Рисунок 12.39.

Элементарный процессор (ЭП) включает в себя арифметико-логическое устройство (АЛУ) и память. Сеть связи между ЭП позволяет осуществлять обмен информацией между любыми ЭП. Поток команд поступает на матрицу ЭП от единого устройства управления. Структура связей между процессорами может иметь самую разную топологию: двумерная решетка, тор, n-мерная решетка и т.п.

Существует широкий спектр научных, технических и административно- хозяйственных задач, которые эффективно решаются на матричном процессоре. При решении задач фактически один и тот же алгоритм параллельно (одновременно) реализуется для многих массивов данных. Каждый из массивов данных размещается и обрабатывается в своем элементарном процессоре. Предварительно данные организуются в векторы. Параллелизм в работе ЭП принципиально позволяет достичь любого уровня быстродействия матричного процессора.

Примеры матричных систем.

Система ILLIAC-IV.

Система ILLIAC-IV создана Иллинойским университетом и фирмой Burroughs. Работы по созданию системы начались в 1966 г., монтаж системы закончен в мае 1972 г. Быстродействие системы 109 оп/сек, полезное время 80-85% общего времени работы ILLIAC-IV, стоимость 30-40 млн долларов, вес 57 т, площадь 930 м2.

Структура ILLIAC-IV показана на рисунке 12.40.

Система ILLIAC-IV состоит из четырех квадрантов, подсистемы ввода/вывода, ЭВМ В-6700, дисковой памяти (ДП) и архивной памяти (АП).

Рисунок 12.40.

Квадрант – матричный процессор, включающий устройство управления и 64 элементарных процессоров. Устройство управления представляет собой специализированную ЭВМ, которая используется для выполнения операций над скалярными и формирует поток команд на матрицу ОП. Элементарные процессоры матрицы регулярным образом связаны друг с другом. Матрица из 64 ЭП предназначается для выполнения операций над векторами. Все 64 ЭП работают синхронно и единообразно.

Допустимо одновременное выполнение скалярных и векторных операций. В системе ILLIAC-IV заложена возможность параллельной работы не только ЭП в матрице, но и устройства управления и матрицы в целом.

В системе ILLIAC-IV используется слово длиной 64 бит. Форматы могут быть 64 или 32 разряда с плавающей запятой и 48 или 24 или 8 разрядов с фиксированной запятой. Матрица из 64 ЭП способна обрабатывать векторы операндов, состоящие из 64, 128, и 512 компонент.

Элементарный процессор может находиться в одном из двух состояний – активном или пассивном. В первом состоянии ему разрешается, а во втором запрещается выполнять команды устройства управления. Состояние ЭП задается при помощи специальных команд, среди них, например, есть команда, установления в пассивное состояние всех ЭП, у которых передаваемая информация больше содержимого накапливающего сумматора. Сумматор и все регистры ЭП программно адресуемы. К памяти каждого ЭП непосредственный доступ имеет только собственный ЭП. Обмен информацией между памятями различных ЭП осуществляется по сети связи при помощи специальных команд пересылок.

Подсистема ввода/вывода состоит из устройства управления, буферного ЗУ и коммутатора. Комплекс этих устройств обеспечивает обмен информацией между квадрантами ILLIAC-IV и средствами ввода/вывода: ЭВМ В-6700, дисковой и архивной памятью, периферийными устройствами, сетью ARPA.

Управляющая ЭВМ В-6700 используется для реализации функций операционной системы (включая ввод/вывод, операции по компиляции и компоновки программ, распределение аппаратных ресурсов, использование служебных программ и т.п.). По сути ЭВМ В-6700 является быстродействующим периферийным устройством ILLIAC-IV.

Система ILLIAC-IV входила в состав вычислительной сети ARPA. Система ILLIAC-IV – средство решения сложных задач, таких как, матричная арифметика, системы линейных алгебраических уравнений, линейное программирование, исчисление конечных разностей, квадратуры (включая БП Фурье), обработка сигналов, задачи на собственные значения, нелинейные уравнения, отыскание корней полиномов и т.п.

Сферой применения ILLIAC-IV являются: наука, экономика, анатомия, энергетика, проектирование, предсказание погоды, радиолокация, оборона, космические исследования и т.д.

Ассоциативные ВС.

Ассоциативные процессоры (АП) предназначены для групповой (параллельной) обработки массивов информации. На макроуровне структура АП и матричные процессоры подобны (см. рис. 52): единое устройство управления и множество связанных ЭП. Однако, на микроуровне наблюдается существенное различие в реализации ЭП и связей между ними. АП в общем случае обеспечивает параллельную обработку слов и разрядов слова.

Множество связанных ЭП представляет собой ассоциативное запоминающее устройство (АЗУ). Множество ЭП способно хранить массивы информации, позволяет выбирать информацию по содержанию (по ассоциативному признаку), допускает одновременное выполнение над словами массива операций: логических, арифметических и поисковых (сортировки, отыскание числа по неравенству и т.д.)

Каждый ЭП представляет собой часть АЗУ, которая используется для хранения и обработки слов большой длины. Для каждого разряда слов предназначен свой физический элемент. Элемент АЗУ содержит логические схемы, обеспечивающие запись внешней информации, считывание данных без разрушения и сравнения содержимого с входной информацией.

Ассоциативный способ обработки данных позволяет преодолеть многие ограничения, присущие адресному доступу к памяти, за счет задания некоторого критерия отбора и проведения необходимых преобразований, только над теми данными, которые удовлетворяют этому критерию. Критерием отбора может быть совпадение с любым элементом данных, достаточным для выделения искомых данных из всех имеющихся. Поиск данных может происходить по фрагменту, имеющему большую или меньшую корреляцию с заданным элементом данных.

Исследованы и в разной степени применяются несколько подходов, различающихся полнотой реализации модели ассоциативной обработки. Если реализуется только ассоциативная выборка данных с последующим поочередным использованием найденных данных, то говорят об ассоциативной памяти или памяти, адресуемой по содержимому. При достаточно полной реализации всех свойств ассоциативной обработки используется термин "ассоциативный процессор".

Ассоциативные системы относятся к классу: один поток команд – множество потоков данных (SIMD = Single Instruction Multiple Data). Эти системы включают большое число операционных устройств, способных одновременно по командам управляющего устройства вести обработку нескольких потоков данных. В ассоциативных вычислительных системах информация на обработку поступает от ассоциативных запоминающих устройств (АЗУ), характеризующихся тем, что информация в них выбирается не по определенному адресу, а по ее содержанию.

Ассоциативная система Staran.

Ассоциативная ВС Staran (рисунок 12.41) являлась частью многомашинной ВС, управляющей воздушным движением в аэропорту. Модифицированный вариант Staran IV имел быстродействие 5-10  оп/с и стоил 15 млн. долларов. Основу системы Staran составляет ассоциативный процессор. Под ассоциативным процессором понимается ассоциативная память с возможным выполнением логических и арифметических операций при ассоциативном поиске.

оп/с и стоил 15 млн. долларов. Основу системы Staran составляет ассоциативный процессор. Под ассоциативным процессором понимается ассоциативная память с возможным выполнением логических и арифметических операций при ассоциативном поиске.

Ассоциативная память включает 32 блока, рассматриваемых как 32 элементарных ассоциативных процессора (ЭП). Любой ЭП способен выполнить набор логических, арифметически и поисковых операций. Суммарное быстродействие 32-х ЭП, или быстродействие АП в целом составляет 5*10  оп/с.

оп/с.

Рисунок 12.41.

Ассоциативная память системы Staranсостоит из матриц, любая из которых обладает возможностью одновременной (параллельной) выборки 256 бит (в направлении слов или направлении разрядов).

В ВС Staranимеется управляющее ЗУ, которое работает с ассоциативной памятью в режиме перекрытия. Управляющее ЗУ служит для хранения данных и микрокоманд и включает быстродействующее, буферное и вспомогательное запоминающие устройства.

Структура АП такова, что она обеспечивает ассоциативный поиск в пределах всей ассоциативной памяти и доступ к любым ЭП. Связь оборудования пользователя с АП осуществляется через интерфейс. Для связи используется канал прямого доступа к памяти (1), буферный канал ввода/вывода (2) внешний функциональный канал (3), канал параллельного ввода/вывода информации(4). Каналы имеют широкую полосу пропускания (свыше 3000 мегабит/с).

Функционирование системы Staran и ILLIAC-IV во многом аналогично. Однако, параллелизм Staran достигается на более низкомлогическом уровне: допустима одновременная обработка 256×32 операндов на 32 элементарных ассоциативных процессорах.

Система Staran ориентирована для работы в системах управления воздушным движением (включая обработку р/л сигналов, распознавание образов, предсказание погоды и управление данными). Она может функционировать как автономная проблемно- ориентированная ВС или работать в составе универсальной системы.

Ассоциативно-матричная система PEPE.

Максимальная производительность системы PEPE 3×10  оп/с. Это ансамбль параллельных ЭП. Система PEPE разработана фирмами Bell Telephone и System Development. Разработанный 36-ти процессорный экспериментальный вариант PEPE использовался в системе ПРО. Конечный вариант PEPE-288 ЭП работает под управлением ЭВМ СDС-7600.

оп/с. Это ансамбль параллельных ЭП. Система PEPE разработана фирмами Bell Telephone и System Development. Разработанный 36-ти процессорный экспериментальный вариант PEPE использовался в системе ПРО. Конечный вариант PEPE-288 ЭП работает под управлением ЭВМ СDС-7600.

Структуры PEPE и ILLIAC-IV при достаточной близости имеют свои особенности. Например, система PEPE способна обработать два независимых потока команд, но любой ЭП (в отличии от ILLIAC-IV) не имеет непосредственно связи с ближайшими соседними ЭП. Это сужает класс решаемых задач. На системе PEPE эффективно решаются такие сложные задачи, в которых нет непосредственно обмена информации между ЭП ансамбля. Например, задача слежения за многими объектами в большом аэропорту. Для этой задачи характерно большое количество данных для траектории любого объекта и один и тот же алгоритм обработки информации для любой из траекторий.

Ассоциативная ВС является значительным этапом по развитию архитектуры и достижения высокой эффективности средств вычислительной техники. Магистральные, матричные и ассоциативные ВС проблемно ориентированы.

ПС-2000(параллельные системы 2000).

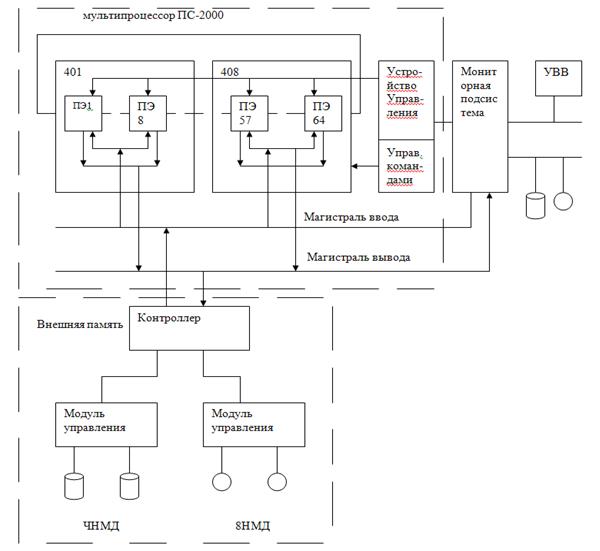

Отечественная система ПС-2000 (рисунок 12.42) создана в начале 80-х годов. Ее можно отнести к матричным системам. Она ориентирована на решение задач, характеризующихся параллелизмом данных, независимостью ветвей и объектов.

Рисунок 12.42.

Центральная часть системы – мультипроцессор ПС-200 , состоящий из решающего поля и устройство управления. Решающее поле строится из 1,2,4 или 8 устройств обработки (УО), в каждом из которых из 8 процессорных элементов. Таким образом, мультипроцессор может содержать 8,16,32 или 64 процессорных элементов. Ёмкость оперативной памяти (ОП) процессорного элемента - 4096 или 16384 слова. Быстродействие ПС-2000 примерно 30-60 млн. флоп/с. Устройство управления содержит микропрограммное управление, ОП и АЛУ. В блок микропрограммного управления загружаются микропрограммы обработки данных, ввода вывода и управления. В комплект программного обеспечения входит набор микропрограмм базовой системы операций, ориентированный на обработку матриц, реализацию быстрого преобразования Фурье (БПФ), решение задач математической статистики, спектрального анализа, линейного и динамического программирования. Возможна реализация на микропрограммном уровне любой необходимой системы операций. В ОП загружается программа обработки. Команды программы выполняются в обычном порядке.

Ввод/вывод данных в память решающего поля, то есть в ОП процессорных элементов, производится через канал прямого доступа, состоящий из магистралей ввода и вывода. Операции ввода/вывода инициализируются мониторной подсистемой, и выполняется под управлением устройства управлением мультипроцессора. Обработка ввода и вывода может выполняться одновременно. Процессорные элементы решающего поля связаны регулярным каналом, по которому передаются данные. Конфигурация регулярного канала перестраивается под управлением программы, образуя одно кольцо из 64 процессорных элементов или несколько одинаковых полей: 8 колец по 8 процессорных элементов, 4 по 16 или 2 по 32.

В целом, система управления мониторной подсистемой реализуется из одной или двух мини-ЭВМ СМ-2 и подключенных к ним периферийных устройств. На ЭВМ реализуется подготовка микропрограмм и программ для мультипроцессора с использованием языков программирования и соответствующих трансляторов. Мониторная подсистема управляет загрузкой микропрограмм в мультипроцессор, контролирует работу мультипроцессоров и обеспечивает обмен между системой и пользователями.

Дата добавления: 2015-08-14; просмотров: 3688;