Триггеры. Триггер – ИС, имеющая два состояния устойчивого равновесия, способная скачком переходить из одного устойчивого состояния в другое под действием внешнего

Триггер – ИС, имеющая два состояния устойчивого равновесия, способная скачком переходить из одного устойчивого состояния в другое под действием внешнего управляющего сигнала.

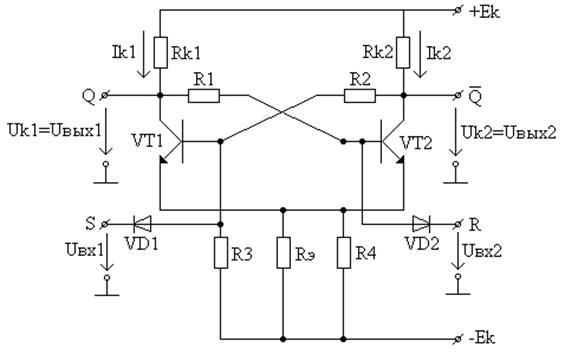

Схемное решение триггеров.

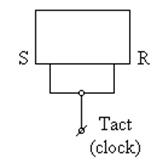

УГО:

Принцип действия:

В основе лежит уравнение Кирхгофа: Uвых=Ек-IкRк. В силу невзаимозаменяемости биполярных транзисторов всегда оказывается, что один из транзисторов открыт чуть больше другого.

Если VT1 открыт больше VT2, то Iк1> Iк2, т.е.  .

.

Процесс идет скачком, пока VT1 полностью открыт, а VT2 полностью закрыт. Это первое условие равновесия триггера. Его внутренняя схема представляет собой 2ух-каскадный УПТ с перекрестными 100%-ными положительными обратными связями R1 и R2. Описанное состояние триггер способен сохранять сколь угодно долгое время, пока на его входы не поступит управляющий сигнал (отрицательный внешний импульс). При поступлении отрицательного импульса на вход SET-установка VT1 скачком закроется, а VT2 откроется, в результате,  . Если подать отрицательный сигнал на вход закрытого транзистора, то его состояние не изменится (на вход RESET-сброс).

. Если подать отрицательный сигнал на вход закрытого транзистора, то его состояние не изменится (на вход RESET-сброс).

Постулат триггера состоит в следующем: на одном выходе триггера должна быть единица, на другом – 0, и наоборот.

Если объединить входы SET и RESET, и подавать входные импульсы сразу на оба входа, то триггер будет изменять свое выходное состояние при поступлении каждого входного импульса. Такой триггер назвали Т-триггером или счетным триггером.

Классификация триггеров.

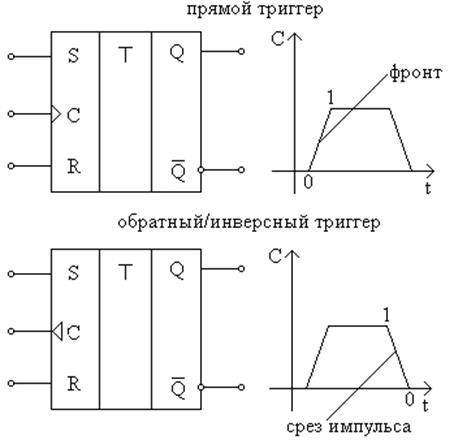

1. По времени срабатывания:

1.1. Асинхронные триггеры, которые срабатывают в любой момент времени при появлении информации одновременно на обоих информационных входах S и R.

1.2. Синхронные триггеры, которые срабатывают при поступлении строб-сигналов.

1.2.1. Статические триггеры, которые срабатывают при определенном уровне строб-сигнала.

1.2.1.1. Однотактные триггеры.

1.2.1.2. 2ух-тактные триггеры.

1.2.2. Динамические триггеры, которые срабатывают на фронте или на срезе строб-сигнала.

2. По функциональному назначению:

2.1. RS-триггеры;

2.2. D-триггеры;

2.3. счетные Т-триггеры;

2.4. JK-триггеры или универсальные триггеры.

Асинхронные RS-триггеры.

Асинхронные RS-триггеры выполняются или на элементах «ИЛИ-НЕ» или на элементах «И-НЕ», причем во внутренней логической схеме триггера должны присутствовать по 2 логических элемента, охваченных 100%-ми перекрестными обратными связями.

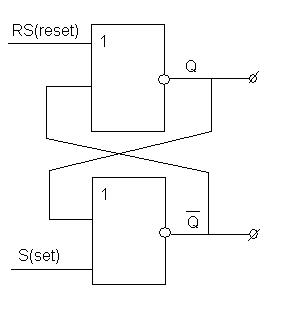

1. ИЛИ-НЕ.

Структурно-логическая схема:

УГО:

Срабатывает при сигналах высокого уровня. Асинхронный RS-триггер имеет 2 информационных входа (set, reset), и 2 выхода (Q,  ).

).

Таблица истинности:

| R | S |

|

|

|

| СОСТОЯНИЕ |

| Исходное состояние | ||||||

| Активизация (установка единицы) | ||||||

| Сброс (установка нуля) | ||||||

| Память (предыдущее состояние) | ||||||

| Неустойчивое состояние |

Триггер фактически двухтактный, т.к. в момент времени t – информация записывается в триггер, а в момент времени t+1 – переносится на выходы.

Наличие еа выходе триггера активных сигналов для схемы ИЛИ-НЕ, триггер находится в неустойчивом состоянии, поэтому такая комбинация входных сигналов называется запрещенной.

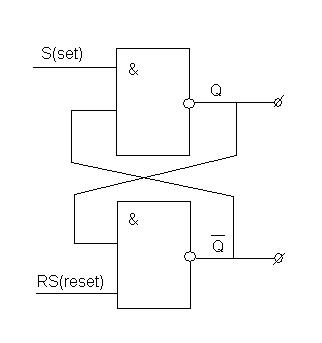

2. И-НЕ.

Структурно-логическая схема:

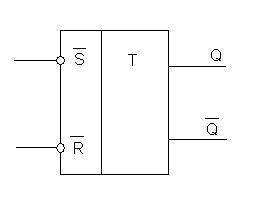

УГО:

Срабатывает при сигналах низкого уровня.

Таблица истинности:

|

|

|

|

|

| CОСТОЯНИЕ |

| Исходное состояние | ||||||

| Активизация | ||||||

| Сброс | ||||||

| Память | ||||||

| Неустойчивое состояние |

0,0 – недопустимая комбинация входных сигналов, для триггеров на элементах ИЛИ-НЕ.

Синхронные RS-триггеры.

1. ИЛИ-НЕ.

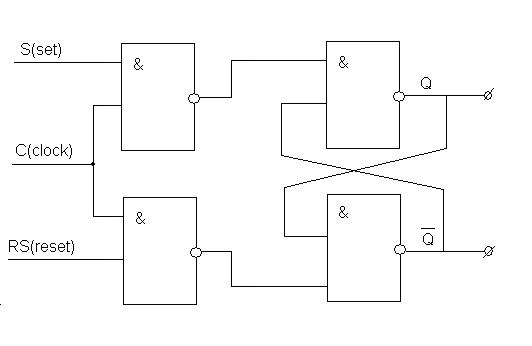

Структурно-логическая схема:

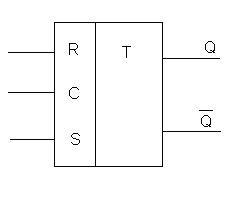

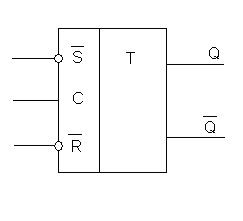

УГО:

Таблица состояний:

| C | R | S |

|

|

|

| СОСТОЯНИЕ |

| Исходное состояние | |||||||

| Память | |||||||

| Активизация | |||||||

| Сброс | |||||||

| Неустойчивое состояние |

2. И-НЕ.

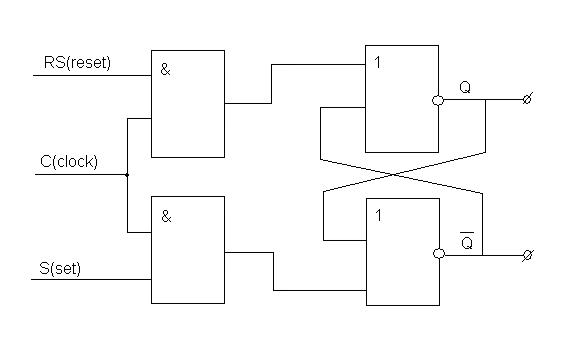

Структурно-логическая схема:

УГО:

Таблица состояний:

К недостаткам асинхронных и синхронных RS-триггеров относят:

1) наличие запрещенных комбинаций входных сигналов;

2) необходимость подачи сразу двух сигналов: на вход set и на вход reset.

Область применения: только в качестве элементов в ячейках памяти.

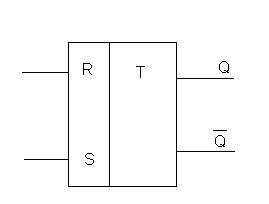

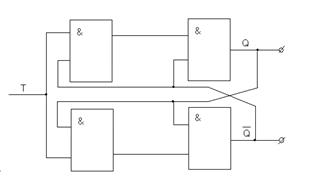

Счетные триггеры или Т-триггеры {T - такт}.

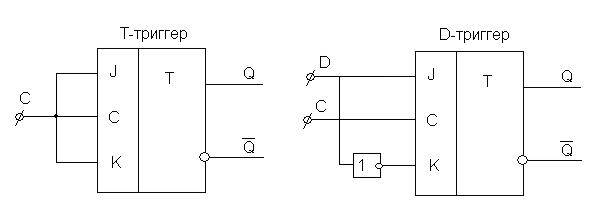

Структурно-логическая схема:

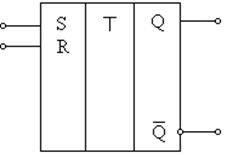

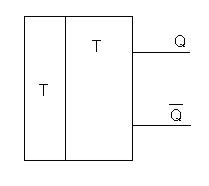

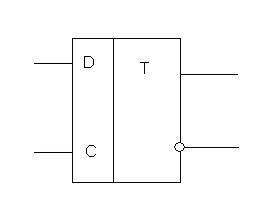

УГО:

Таблица состояний:

| T |

|

|

|

| СОСТОЯНИЕ |

| Исходное состояние | |||||

| Память | |||||

| Первый импульс | |||||

| Второй импульс |

Счетный триггер меняет состояние своих выходов, при поступлении каждого нового сигнала на вход.

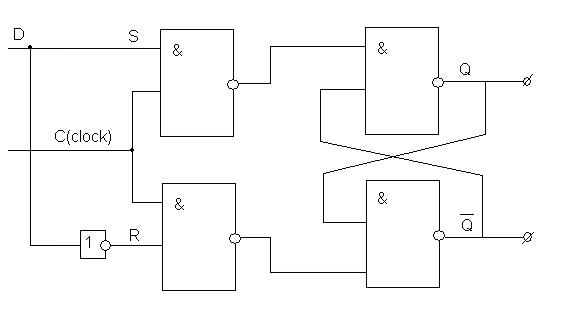

D-триггеры {D – delay – защелка, задержка}.

Структурно-логическая схема:

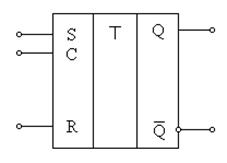

УГО:

В D-триггере имеется один информационный вход и 1 вход синхронизации (разрешения, стробирования). Одновременная подача на вход S и R противоположных по знаку сигнала, за счет внутреннего инвертирования сигнала D, с помощбю элемента НЕ.

Таблица истинности:

Универсальный JK-триггер{JK – jump keep}.

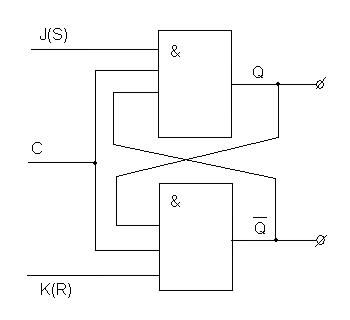

Структурно-логическая схема:

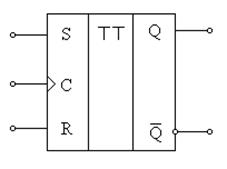

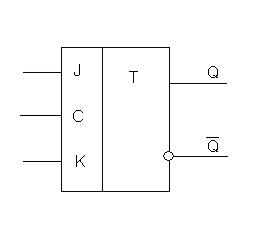

УГО:

Таблица состояний:

| С | J | R | Q |

| СОСТОЯНИЕ |

| Исходное состояние | |||||

| Режим счета (1 импульс) | |||||

| Режим счета |

Для организации режима счета, на входы J и K подаются одинаковые сигналы логической единицы.

Если на С единица, а на J – 1, K – 0, или J – 0, K – 1, то режим данных, причем, если на выходе:

Q – 1,  - 0 – активизация;

- 0 – активизация;

Q – 0,  -1 – сброс.

-1 – сброс.

Триггер называется универсальным, потому что, если все 3 входа соединить, то получаем режим счетчика; если на J подать сигнал от D, а на К, через инвертор, то получаем D-триггер.

Область применения: счетные триггеры применяются для счета команд в МП-системах, для счета адресов, для счета циклов выполняемых команд; D-триггеры применяют в различных регистрах, схемах памяти, при записи и считывании информации.

Дата добавления: 2015-08-08; просмотров: 1172;