Шифраторы и дешифраторы.

Представляют собой частный случай преобразователей кода. В особую группу их выделяют потому, что входной сигнал в шифраторе и выходной сигнал в дешифраторе на одном из входов или выходов равен единице.

Шифратором называется комбинационная ИС, в которой единичный сигнал на одном из входов преобразуется в ДДК на выходе. Говорят, что шифратор преобразует десятичное входное число МП-системы в ДДК внутренней системы.

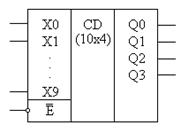

УГО:

Таблица истинности:

| Входы | Выходы | |||||||||||||

| X0 | X1 | X2 | X3 | X4 | X5 | X6 | X7 | X8 | X9 | Q0 | Q1 | Q2 | Q3 | ||

| - | - | - | - | ||||||||||||

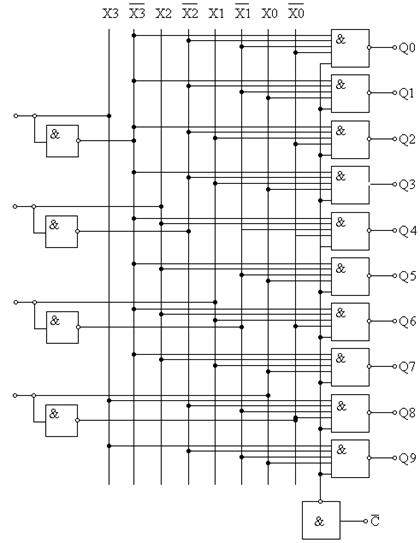

ФАЛ: Q0=X1+X3+X5+X7+X9

Q1=X2+X3+X6+X7

Q2=X4+X5+X6+X7

Q3=X7+X9

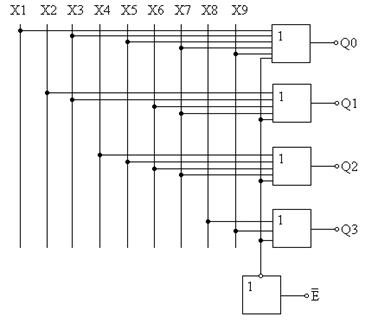

Структурно-логическая схема:

Область применения – для ввода информации с клавиатуры в МП-систему.

Примечание: если количество выходов равно n, то количество входов m равно  , такой шифратор является полным. Если m<

, такой шифратор является полным. Если m<  , то шифратор называется неполным.

, то шифратор называется неполным.

Дешифратором называется комбинационная ИС, в которой ДДК преобразуется единицу на одном из выходов схемы, т.е. в слово команды.

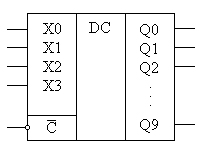

УГО:

Таблица истинности:

| С | Входы | Выходы | ||||||||||||

| Х3 | Х2 | Х1 | Х0 | Q9 | Q8 | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | |

ФАЛ:

ФАЛ:

Структурно-логическая схема:

Область применения:

l для организации шин адреса требуемой разрядности;

l для включения на выходе МП-системы печатающих и светосигнальных устройств;

l для селекции одного из используемых устройств на выходе МП-системы.

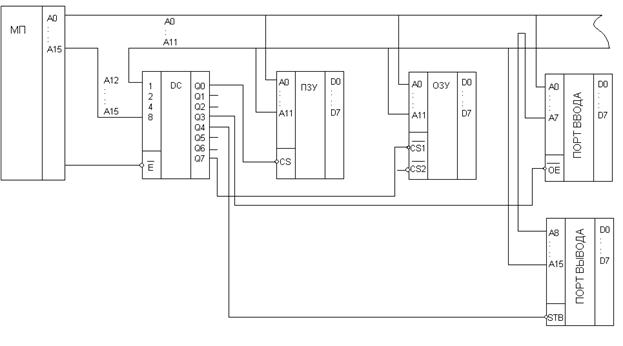

Использование цифровых дешифраторов для выбора адреса устройства МП-системы.

В зависимости от кода сигнала на выходе, напряжение высокого уровня (логическая единица) появляется только на одном выходе. Номер выхода должен соответствовать номеру входа.

Карта памяти:

0000 – 7FFFF – ПЗУ, область монитора;

8000 – 83С6 – ОЗУ, область пользователя.

Выводы декодера Q0-Q7 подключены к выводам ChipSelect(CS)-выбор модуля ВМ, схем памяти.

На вход декодера поступают старшие разряды шины адреса, которые определяют область памяти, с которой собирается общаться МП.

Сигнал высокого уровня на выходе дешифратора соответствует тому номеру, который поступил на его входы. Если в старшем разряде 0, то 1 на Q0, если в старшем разряде 1000, то 1 на Q8.

Соответствующее включение обеспечивает: в первом случае – схема ПЗУ, во втором случае – схема Номер ячейки памяти, из которой считывается информация, определяется уровнем сигналов на остальных проводниках шины адреса.

Таким образом, декодер (дешифратор адреса) осуществляет адресацию памяти.

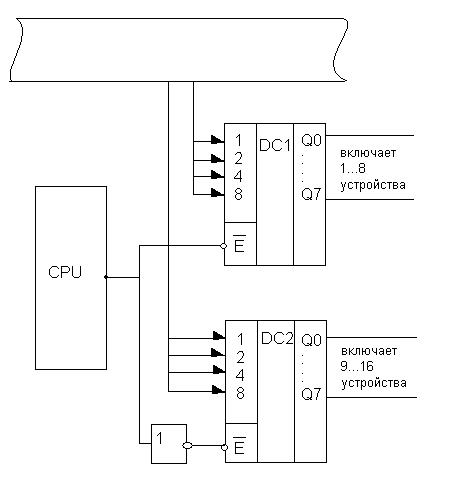

Для увеличения разрядности выходного сигнала декодера, т.е. для подключения большего количества ИС, можно применить 2 декодера (4/10), включенных в так называемую дерево-схему.

Используя дерево-схему декодеров(4/10) можно увеличить количество адресуемых устройств (выбираемых) до 16.

Дата добавления: 2015-08-08; просмотров: 1216;