Логические элементы.

Логический элемент – интегральная схема, в которой выходной сигнал связан со входным по законам алгебры логики.

В цифровой электронике в качестве основных логических элементов приняты следующие 7:

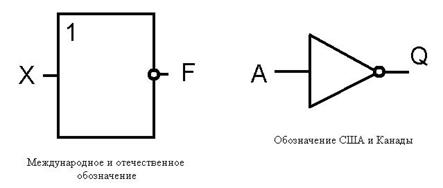

1) НЕ, NOT реализует логическую логическое отрицание (инверсия);

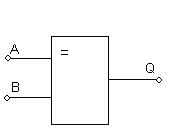

УГО - условное графическое обозначение:

Таблица истинности – сочетание всех возможных выходных сигналов и соответствующих им комбинаций входных сигналов.

ФАЛ - функция алгебры логики:

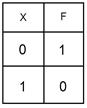

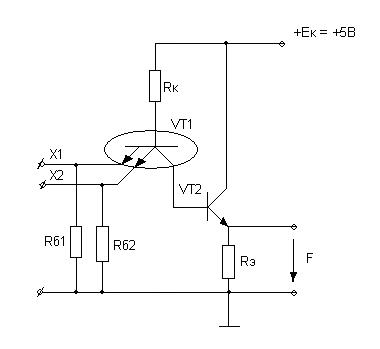

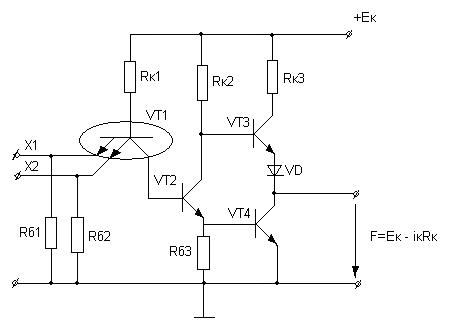

ТТЛ – транзисторно-транзисторная логика:

Транзисторный ключ на биполярном транзисторе может находится в двух состояниях: при наличии входного сигнала транзистор открыт, работает в режиме насыщения, внутреннее сопротивление стремится к 0, а выходное напряжение пропорционально сопротивлению, и ФАЛ равна нулю; а если входной сигнал отсутствует, то транзистор работает в режиме отсечки (закрыт), внутреннее сопротивление стремится к бесконечности, выходной сигнал – напряжение высокого уровня, что соответствует логической единице.

Достоинством этой схемы является быстродействие; недостатком – малая нагрузочная способность.

Под нагрузочной способностью понимают количество устройств, которыми может быть нагружена интегральная схема. Коэффициент разветвления по выходу не более 15.

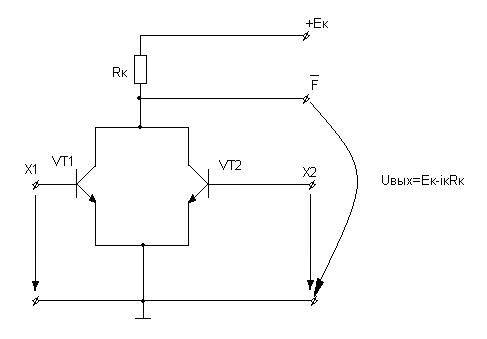

«НЕ» на МОБ-транзисторе.

VT1 выполняет роль коллекторной нагрузки, VT2 – ключа. На затвор VT1 все время подан положительный потенциал, т.е. он всегда открыт; VT2 открыт только в том случае, если на входе есть положительный сигнал, т.е.  =1, внутренне сопротивление равно 0, выходное напряжение равно 0.

=1, внутренне сопротивление равно 0, выходное напряжение равно 0.

К достоинствам относят:

1) на той же площади кристалла, что и у биполярного ключа, располагается в 10 раз больше транзисторов, т.е. стоимость меньше;

2) нагрузочная способность в 10 раз больше, чем на биполярном транзисторе;

3) в 1000 раз меньше потребление мощности от источника питания, поэтому схема распространена. Но быстродействие в 10 раз меньше, это объясняется большими сопротивлениями во входной и выходной цепи и большими входными емкостями конденсатора между затвором и истоком.

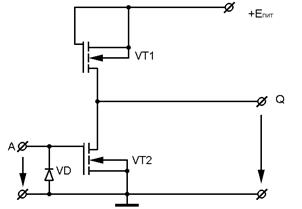

2) ИЛИ, OR реализует логическую функцию – логическое сложение (дизъюнкция);

УГО:

ФАЛ: F = X1 + X2 = X1 V X2.

| X1 | X2 | F |

Таблица истинности:

В логике ТТЛ:

Биполярные транзисторы VT1 и VT2 соединены параллельно, входные сигналы подаются на базы транзисторов, выходной – снимается с сопротивления эммитера.

Если хотя бы один транзистор открыт (т.е. сигнал на базе имеет напряжение высокого уровня Х1=Uн=1), то через Rэ проходит ток, который создает падение напряжения на Rэ не равное нулю: F=1=Uн.

Если сигналы на обоих входах отсутствуют, то оба транзистора заперты, токи через них не протекают, напряжение на Rэ равно нулю.

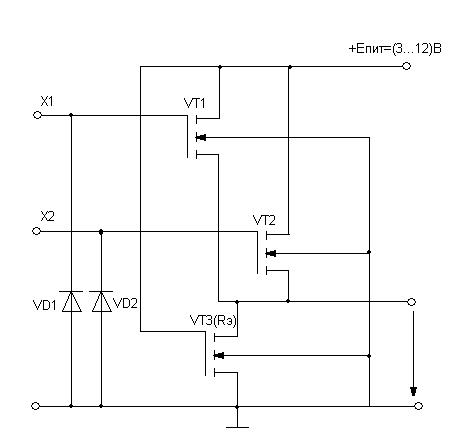

В МДП-логике:

Входные сигналы Х1 и Х2 подаются на затворы VT1 и VT2, в схеме использованы транзисторы с индуцированными каналами. Роль сопротивления нагрузки в этих транзисторах выполняет VT3.

Если на одном из транзисторов VT1/VT2 на затворе положительный потенциал (т.е. 1), то транзистор пропускает ток от +Э, на VT3, который всегда открыт, с VT3 снимаем напряжение.

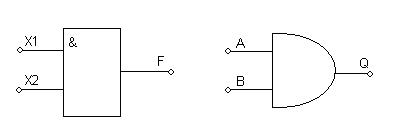

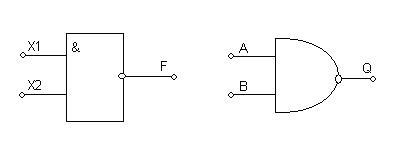

3) И, AND – выполняет функцию логического умножения (конъюнкция).

УГО:

ФАЛ: F = X1*X2 = X1 Λ X2.

| X1 | X2 | F |

Таблица истинности:

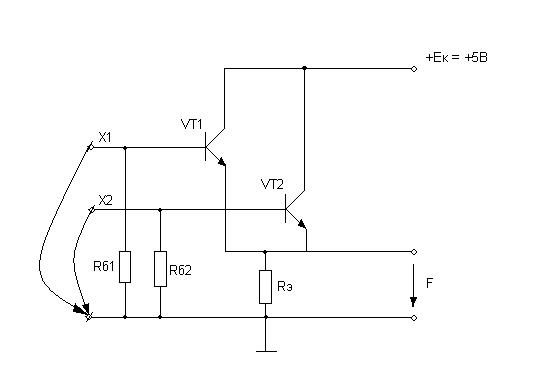

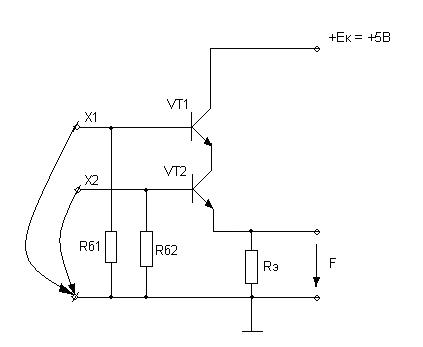

В логике ТТЛ:

В ТТЛ логике биполярные транзисторы VT1 и VT2 теперь соединены последовательно. Напряжение на Rэ появится только в том случае, если будут открыты оба транзистора и VT1 и VT2. Если хоть один из транзисторов закрыт, то сигнал на выходе отсутствует.

Схема И на многоэммитерном транзисторе (с МЭТ VT1):

Отличительной особенностью схемы является использование многоэммитерного транзистора, в котором количествоэммитеров равно количетву входов логического элемента.

Если входные сигналы Х1 и Х2 – напряжение высокого уровня (1), то ток через переходы база-эммитер транзистора VT1 не протекает и вынужден идти через переход база-коллектор, при этом на базе транзистора VT2 появляется отпирающее напряжение, транзистор VT2 открывается, через него протекает ток, который создает на Rэ падение напряжения F=1.

Если хотя бы на 1 из выходов Х1/Х2 сигнал отсутствует, то пойдет ток через переход эммитер-база транзистора VT1 и для включения транзистора VT2, оставшегося тока база-коллектор VT1 будет недостаточно, следовательно, ток через VT2 не протекает F=0.

4) ИЛИ-НЕ, NOR выполняет операцию логического сложения с инверсией.

УГО:

ФАЛ: F =

| X1 | X2 | F |

Таблица истинности:

В логике ТТЛ:

Если на обоих входах транзисторов VT1 и VT2 имеются сигналы, то оба транзистора открыты, протекает ток iк и F  0=0.2

0=0.2  0.3 В.

0.3 В.

5) И-НЕ, NAND выполняет операцию логического умножения с инверсией.

УГО:

ФАЛ: F=  .

.

| X1 | X2 | F |

Таблица истинности:

В логике ТТЛ (базовый элемент ТТЛ логики):

Если на входах Х1 и Х2 МЭТ VT1 имеется входное напряжение высокого уровня, то ток через переходы база-эммитер транзистора VT1 не проходит. Весь ток пойдет через переход (VT1) база-коллектор и откроет транзистор VT2, следовательно, потечет ток  , в результате на входе транзистора VT2 низкий потенциал не откроет этот транзистор. С другой стороны появится напряжение на базе транзистора VT4, транзистор VT4 откроется, и тогда на его выходе появится сигнал F=0.

, в результате на входе транзистора VT2 низкий потенциал не откроет этот транзистор. С другой стороны появится напряжение на базе транзистора VT4, транзистор VT4 откроется, и тогда на его выходе появится сигнал F=0.

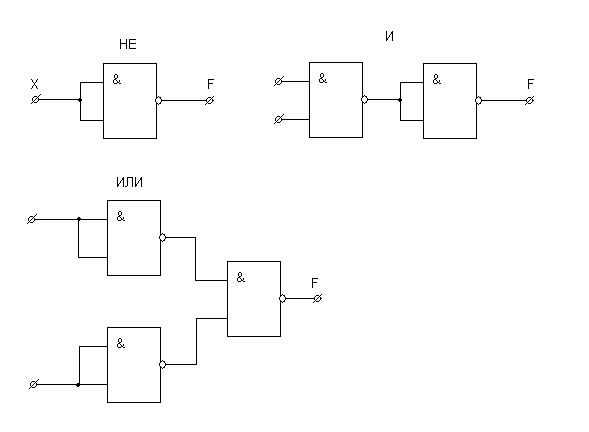

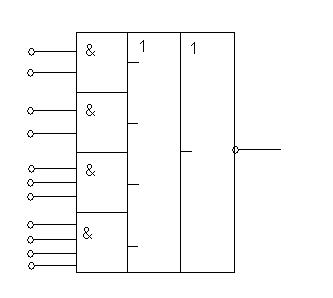

Базовый элемент И-НЕ считается универсальным, т.к. с его помощью можно получить любой логический элемент, в том числе описываемый основными логическими функциями И, ИЛИ, НЕ.

Универсальность базового элемента И-НЕ состоит в том, что, используя только этот элемент, можно создать логическую интегральную схему любой степени сложности.

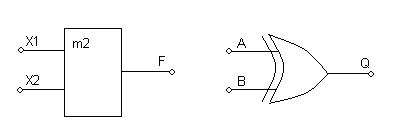

6) ИСКЛЮЧАЮЩЕЕ ИЛИ, XOR – сумматор по модулю 2 или логическая неравнозначность.

УГО:

ФАЛ: F=

| X1 | X2 | F |

Таблица истинности:

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ может быть получен с использованием:

1) разных логических элементов (НЕ, И-НЕ);

2) в базисе И, НЕ;

3) в базисе ИЛИ, НЕ.

7) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, XNOR – логическая равнозначность.

УГО:

ФАЛ: (А=В)=А*В+

Таблица истинности:

| А | В | А=В | А<В | А>В |

Сложные логические элементы.

Часто при выполнении функций алгебры логики приходится выполнять последовательность операций И, ИЛИ, НЕ, поэтому промышленность выпускает такие интегральные схемы массовым тиражом.

ИС 555 ЛР 2

2-2-3-4-4И-4ИЛИ-НЕ

Условные обозначения логических элементов:

| К | Л | А | ||

1) К – широкое применение ИС;

2) 1 – полупроводниковая ИС (технология изготовления ИС);

3) № серии;

4) функциональное назначение (логический элемент)

5) тип логического элемента:

ЛИ – И

ЛН – НЕ

ЛА – И-НЕ

ЛЕ – ИЛИ-НЕ

ЛЛ – ИЛИ

ЛР – И, ИЛИ, НЕ.

Дата добавления: 2015-08-08; просмотров: 3561;