Триггеры.

Многие схемы памяти при необходимости выбирают значение на определенной линии в заданный момент времени и запоминают его.

В такой схеме, которая называется триггером(flip-flop) смена состояния происходит не тогда, когда синхронизирующий сигнал равен 1, при переходе синхронизирующего сигнала с 0 на 1 (по фронту) или с 1 на 0 (по спаду).

Следовательно, длина синхронизирующего импульса не имеет значения, поскольку переходы происходят быстро.

Различие между триггером и защелкой заключается в том, что триггер запускается перепадом сигнала,а защелка запускается уровнем сигнала.

В литературе эти термины часто путают. Многие авторы используют термин «триггера, когда речь идет о защелке, и наоборот. В отечественной литературе термин "защелка" (latch) вообще не используется, говорят о триггерах. Однако при этом вводится понятие Т- триггера, который и является «настоящим» триггером

Существуют несколько подходов к разработке триггеров. Например, путем генерирования очень короткого импульса на фронте синхронизирующего сигнала, который подается в D-защелку,

|

При стробирущем сигнале равном 0, комбинация сигналов на входе 3 – го вентиля НЕ-И - 10, а на его выходе значение сигнала равное 0.

При появления положительного импульса на стробирующем входе (строб =1), за счет небольшой (не более 5 нс) задержки прохождения сигнала через инвертор 2, комбинация сигналов на входе 3 – го вентиля НЕ-И - 11, а на его выходе устанавливается значение сигнала равное 1.

После срабатывания инвертора 2, комбинация сигналов на входе 3 – го вентиля НЕ-И - 01, а на его выходе опять устанавливается значение сигнала равное 0. При этом длительность синхронизирующего сигнала ни как не влияет на работу триггера.

Такая схема триггера проста для понимания, но на практике обычно используются более сложные триггеры.

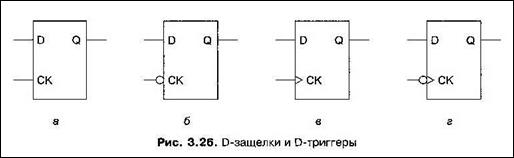

Стандартные обозначения защелок и триггеров показаны на рис. 3.26.

|

На рис. 3.26 а изображена защелка, состояние которой загружается тогда, когда синхронизирующий сигнал СК (от слова clock) равен 1, в противоположность защелке, изображенной на рис. 3.26, б, у которой синхронизирующий сигнал обычно равен 1, но переходит на 0, чтобы загрузить состояние из линии D.

На рис. 3.26, в и г изображены триггеры. О том, что это триггеры, а не защелки, говорит уголок на синхронизирующем входе.

Триггер на рис, 3.26, в изменяет состояние на фронте синхронизирующего импульса (переход от 0 к 1)т тогда как триггер на рис, 3.26, г изменяет состояние на спаде (переход от 0 к 1).

Многие (хотя не все) защелки и триггеры также имеют выход  , а у некоторых есть два дополнительных входа: Set (установка) или Preset (предварительная установка) и Reset (сброс) или Clear (очистка). Первый вход (Set или Preset) устанавливает Q = 1, а второй (Reset или Clear) устанавливает Q=0.

, а у некоторых есть два дополнительных входа: Set (установка) или Preset (предварительная установка) и Reset (сброс) или Clear (очистка). Первый вход (Set или Preset) устанавливает Q = 1, а второй (Reset или Clear) устанавливает Q=0.

Дата добавления: 2015-07-24; просмотров: 1651;