Пример построения мажоритарного элемента в пакете Multisim

Мажоритарными элементами (МЭ) называются ПС, имеющие нечетное число М логически равноправных входов Хр и выполняющие функцию

где v = (Xn,...., X1), Xp = 0 и 1, p = 1, 2, ..., M,

L = (M + 1) / 2 - пороговый уровень (арифметическая сумма входных сигналов).

Трехвходовой МЭ выполняет функцию f = X3X2 V X3X1 V X2X1. Действительно, f = 1 только при равенстве двух или трех сигналов из Хр, р = 1, 2, 3. Если Х2Х1 = 0, то f = (X2 V X1)X3, а при X3 = 1 функция f = X2 V X1.

Алгоритм построения МЭ такой же, как и для ПС.

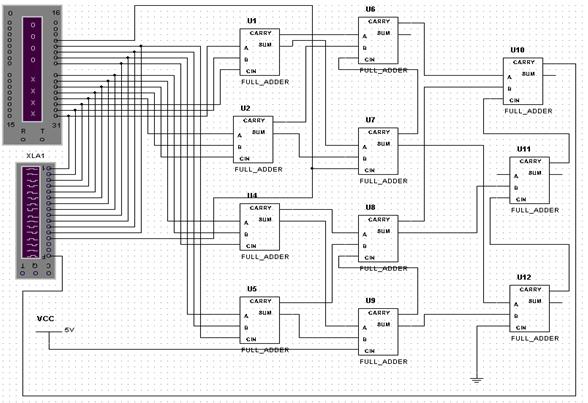

Например, построим МЭ с M = 13. За основу примем одноразрядный двоичный сумматор и построим схему МЭ, следуя правилам арифметического сложения значений входных переменных X13,...X1. Весь ход рассуждений аналогичен предыдущему примеру, однако есть и некоторая особенность (рис. 6.6). В частности, по условию L = 7, следовательно, КС должна быть построена для дешифрирования именно этого числа. Но возможно найти решение и без специальной КС, если в конечный результат добавить искусственно «1». Тогда при L = 7 единица будет на выходе переноса старшего разряда выходного сумматора. Этот разряд и будет выходом всей схемы МЭ в целом. Таким же способом можно синтезировать любой мажоритарный элемент.

Рис. 6.9 Мажоритарный элемент с М = 13

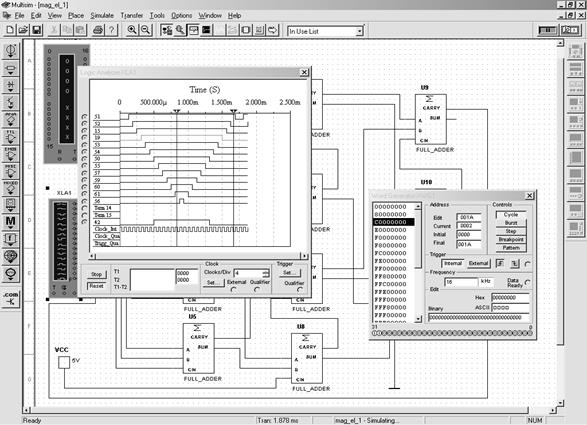

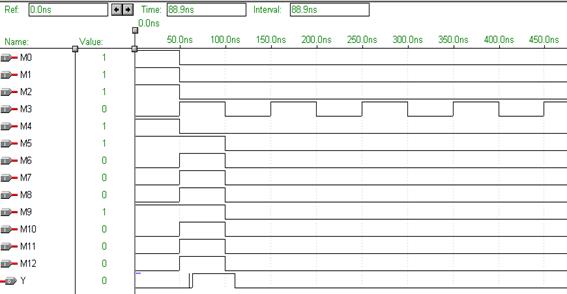

Рис. 6.10 Временные диаграммы для мажоритарного элемента

(см. рис. 6.6)

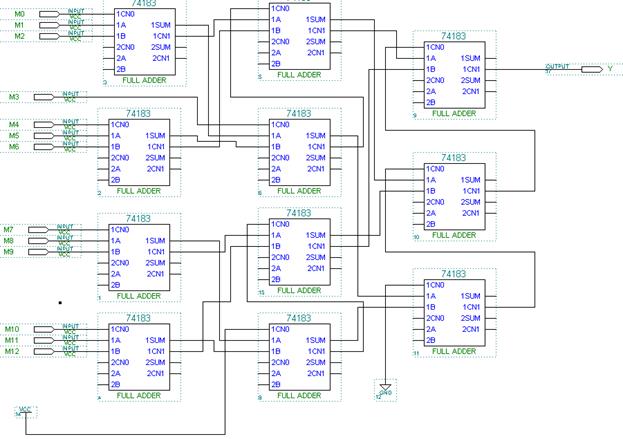

Рис. 6.11 Мажоритарный элемент с М = 13 в пакете MAX+Plus II

Рис. 6.12 Временные диаграммы для мажоритарного элемента

Рис 6.13 Матрица временных задержек

Программа:

SUBDESIGN mazoritarny_element

(M[0..12] : INPUT;

Y : OUTPUT;)

VARIABLE A, L;

BEGIN

A = M0+M1+M2+M3+M4+M5+M6+M7+M8+M9+M10+M11+M12;

IF A>= L;

THEN Y = VCC;

ELSE Y = GND;

ENDIF;

END;

В интегральном исполнении выпускаются мажоритарные элементы (Majority Logic Gate), имеющие 3 (533ЛПЗ и 561ЛП13) и 5 (МС14530В) входов. Функция, выполняемая 3-входовым. МЭ, совпадает с функцией переноса одноразрядного сумматора: f=X1X2VX1X3VX2X3, где Xp— входные сигналы функционирование 5-входового МЭ МС14530B описывается выражением:

F=(I1I2I3VI1I2I4VI1I2I5VI1I3I4VI1I3I5VI1I4I5VI2I3I4VI2I3I5VI2I4I5VI3I4I5)ÅP, (6.1)

где P (Polarity) — сигнал инвертирования функции выхода МЭ.

Из соотношения (1) при подстановке определенных значений некоторых сигналов следует, что 5-входовой МЭ может использоваться для выполнения различных переключательных функций:

I5=1, I4=0 =>F=(I1I2 V I2I3 V I2I3) Å Р – 3-входовой МЭ, с возможностью инвертирования функции выхода F,

I5=I4=0 => F=I1I2I3ÅР– 3-входовой ЛЭ И/И-НЕ,

I5=I4=1 => F=(I1 V I2 V I3)ÅP – 3-входовой ЛЭ ИЛИ/ИЛИ-НЕ,

I5=I4 => F=(IlI2IЗ V I1I4 V I2I4 V I3I4)ÅР – 4-входовая пороговая схема с порогом L = 3 и неравными весами входов (вход I4 имеет вес вдвое больший, чем остальные входы) с возможностью инвертирования функции выхода.

Дата добавления: 2015-04-25; просмотров: 2069;