Преобразователь прямого кода в дополнительный код

При построении взаимных преобразователей кодов следует исходить из определений для этих кодов и правил взаимного преобразования (перевода).

Правила взаимного преобразования кодов вытекают из определений кодов и правил двоичной арифметики. В частности, х Å 0 = х, х Å 1 = х.

Общие правила взаимного преобразования кодов n-разрядных двоичных чисел можно выразить следующими соотношениями:

а) если необходимо [Х]п/ [Х]0, то [X]0=(Xn+1, xпnÅxn+1, xпn-1Åxn+1 ,…, xп1Åxn+1);

б) если необходимо [Х]0/ [Х]п, то [X]п=(Xn+1, x0nÅxn+1, x0n-1Åxn+1 ,…, x01Åxn+1);

в) если необходимо [Х]п/ [Х]д, то [X]д=[(Xn+1, xпnÅxn+1 ,…, xп1Åxn+1) Å xn+1];

г) если необходимо [Х]д/ [Х]п, то [X]п=[(Xn+1, xдnÅxn+1 ,…, xд1Åxn+1) Å xn+1];

д) если необходимо [Х]0/ [Х]д, то [X]д = [Х]0 Å xn+1 ,

где [X]п – прямой код числа,

[X]о – обратный код числа,

[X]д – дополнительный код числа.

При использовании сумматора в качестве преобразователя кода необходимо иметь (n+1)-разрядный сумматор, причем на неиспользованные входы подают нуль, т.к. хÅ0=х, а для формирования сигнала переноса (знакового разряда) используют (n+1)-й вход сумматора.

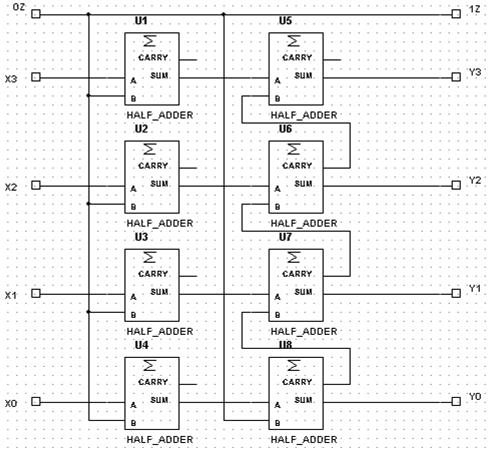

Например, построим преобразователь трехразрядных чисел прямого кода в дополнительный, т.е. осуществим [Х]п/[Х]д

При построении преобразователя будем руководствоваться алгоритмами в) и г). Из их анализа следует, что при преобразовании кодов необходимо вначале произвести поразрядно суммирование по модулю два входной информации (х3, x2, x1) и знакового разряда x4, а затем к полученному результату прибавить значение x4. Первую операцию выполним с помощью n сумматоров по модулю 2 (схем "Исключающее ИЛИ"), а вторую - с помощью четырехразрядного сумматора. При этом результат суммирования по модулю 2 подадим поразрядно на один из входов сумматора, а на вторые (неиспользованные) входы подадим нуль. Знаковую информацию подадим на входы 4-го разряда сумматора и на вход переноса. Результат получим на выходах сумм, причем вход 4-го разряда будет знаковым.

Если на вход схемы преобразователя четырехразрядного прямого кода в дополнительный код (см. рис. 6.15) подать дополнительный код, то на выходе получим прямой код.

Подведём итог:

Правило кодирования: если число A>0, то [A]доп=[A]пр, если число А<0, то в знаковый разряд кода записывается 1, числовые разряды исходного числа инвертируются, и к младшему числовому разряду добавляется 1.

Например, число А = 1.111 в дополнительном коде

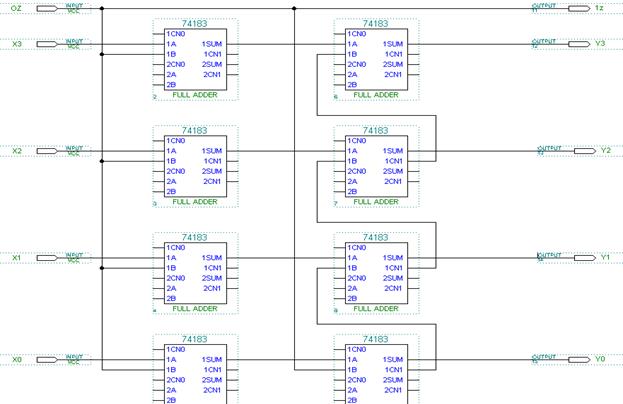

Схему такого преобразования можно собрать на сумматорах (рис.6.15).

В модифицированном дополнительном коде в отличие от дополнительного кода для представления знака числа отводится два разряда. Например, отрицательное число B, модуль которого равен 00.01110, в модифицированном дополнительном коде: [B]Mдоп = 11.10010.

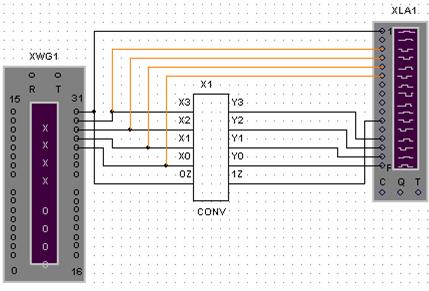

Рис. 6.14 Подключение преобразователя

Рис. 6.15 Схема для преобразования прямого кода в дополнительный (для 4-х разрядных чисел)

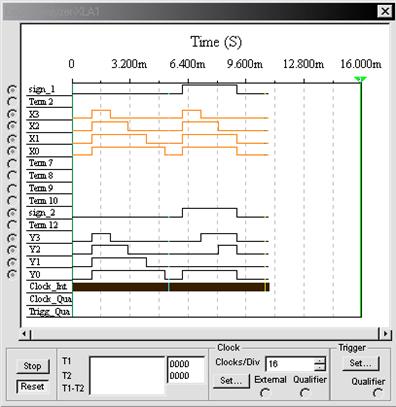

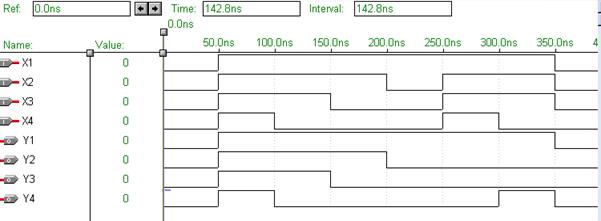

Рис. 6.16 Временные диаграммы для преобразователя прямого кода

в дополнительный

Рис. 6.17 Преобразователь прямого кода в дополнительный в пакете MAX+Plus II

Рис. 6.18 Временные диаграммы для преобразователя прямого кода в дополнительный

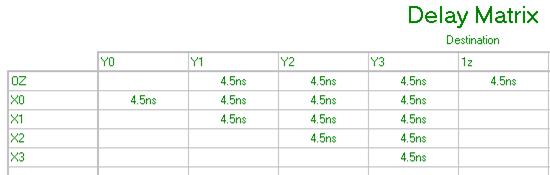

Рис. 6.19 Матрица временных задержек

Программа:

SUBDESIGN preobraz_praymogo_v_dopol

( X[3..0] : INPUT;

Y[3..0] : OUTPUT;

Q[3..0], t[3..0] : NODE;

)

BEGIN

IF x[3] == 0 THEN

Y[3..0] = x[3..0];

ELSE

t[3] = x[3];

t[2..0] = !x[2..0];

Q[3..0] = t[3..0] + B"00000001";

y[3..0] = Q[3..0];

ENDIF;

END;

Обратите внимание, на временных диаграммах показаны не все возможные входные сигналы. Вам так же не рекомендуется перебирать их все (32 шт.). На временных диаграммах видно, что:

| Прямой код | Обратный код |

| 0.0000 | 0.0000 |

| 0.1111 | 0.1111 |

| 0.0111 | 0.0111 |

| 0.0011 | 0.0011 |

| 0.0001 | 0.0001 |

| 1.1111 | 1.0001 |

| 1.0111 | 1.1001 |

| 1.0011 | 1.1101 |

Такие комбинации были выбраны потому, что их очень легко проверить.

Дата добавления: 2015-04-25; просмотров: 4943;