Преобразователь обратного кода в прямой

Если на вход схемы преобразователя четырехразрядного прямого кода в обратный код (см. рис. 6.20) подать дополнительный код, то на выходе получим прямой код.

6.4.6 Построение преобразователя двоичного кода в двоично-десятичный

Десятичные сумматоры применяются в тех случаях, когда числа X и Y представлены в десятичной системе счисления двоично-десятичным кодом 8-4-2-1 и требуется представлять сумму S в этом же коде. Числа X и Y записываются в виде:

Х’=хn,...х1х0 Y’=yn,... у1,у0

Код 8 - 4 - 2 - 1 неудобен для выполнения арифметических операций, в частности из-за сложности обнаружения переноса в следующую тетроду при Хр + Yр > 10. При вычитании десятичных чисел X' и Y’ дело обстоит еще сложнее – требуется вводить преобразователь кода 8 - 4 - 2 - 1 отрицательных чисел в дополнение до 9 (или до 10).

Десятичные сумматоры для сложения и вычитания чисел Х и Y можно построить на двоичных сумматорах, если использовать код с избытком 3. Код 8 - 4 - 2 - 1 для числа Хр + 3 называется кодом с избытком 3 числа Хри обозначается через {Ар}. Для сложения 4-разрядных двоичных кодов {Хр} и {Yр} можно использовать 4-разрядные двоичные сумматоры.

Рассмотрим особенности сложения положительных чисел Ар и Yр в коде с избытком 3. Если Хр + Yр > 10, то {Хр} + {Yр} = Хр + 3 + Yр + 3 > 16, и на выходе двоичного сумматора возникает перенос Сp+1= 1 в следующий десятичный разряд, а остаток суммы будет равен {Хр} + {Ур} - 16, в то время как он должен быть равен

{Xp+Yp-10}=Xp+Yp-10+3={Xp}+{Yp}-16+3.

Поэтому к остатку суммы {Xp}+{Yp}-16 следует прибавлять число 3.

Если Хр + Yр < 10, то {Xp}+{Yp}<16 и на выходе двоичного сумматора перенос отсутствует (Cp+1 = 0), а сумма {Хр} + {Yр} = {Хр + Yр} + 3. Поэтому из суммы {Хр} + {Yр} следует вычесть число 3, чтобы получить величину {Хр + Yр}, которая является кодом с избытком 3 суммы Хр+Yр. Вычитание какого-либо числа эквивалентно сложению его с дополнением до 2n, поэтому вместо вычитания числа 3 можно прибавить число 24 – 3 = 13 = 1101.

Таким образом, если перенос возникает, то к остатку суммы следует прибавить число 3, а если он отсутствует, то к сумме следует прибавить число 13. Итак, одноразрядный десятичный сумматор для десятичных разрядов, представленных в коде с избытком 3, описывается соотношениями:

(6.6)

(6.6)

где Cp+1 — перенос в следующий десятичный разряд; {Sp} – значение р-го десятичного разряда суммы чисел X и Y; Ср = 0 или 1 – перенос из предыдущего десятичного разряда. Сложение с числами 3 и 13 называется коррекцией суммы. Из соотношения (6.6) видно, что вычисление суммы {Sp}можно выполнить с помощью двух последовательно включенных 4-разрядных двоичных сумматоров: первый сумматор вычисляет вспомогательную сумму

и перенос Сp+1, а второй сумматор – сумму

и перенос Сp+1, а второй сумматор – сумму

так как Cp+1 Cp+1 Cp+1 1 = 13 при Ср+1 = 0 и Ср+1Cp+1Cp+1 1 = 3 при Cp+1 = 1. Такое устройство называется сумматором кодов с избытком 3.

Рассмотрим теперь вычитание n-разрядных десятичных чисел X и Y с использованием кода с избытком 3.

Так как S’=X-Y=X-10n+(10n-Y)= X-10n+W , где W=10n-Y,

То вычитание из X числа Y эквивалентно сложению X с дополнением Y до 10n с коррекцией результата на 10n.

При Х ³ 5 надо производить сложение числа Х (x4, x4, x4 , x4) с числом 3. Таким образом, данный преобразователь выполняет функцию Y = X, если 0 £ Х £ 4 и Y = X + 3, если 5£ Х£9.

Таблица 6.3Таблица истинности преобразователя

двоичного кода в двоично-десятичный

| Х4 | Х3 | Х2 | X1 | Y4 | Y3 | Y2 | Y1 |

Построим преобразователь двоично-десятичного кода в двоичный на ЛЭ.

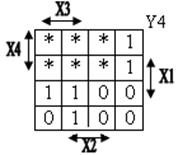

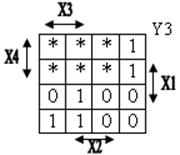

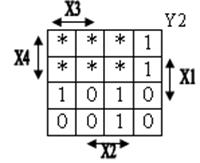

Для получения логических выражений представим переменные Y1, Y2, Y3, Y4 в форме таблиц Вейча:

Тогда для Y4 можно записать:  , или иначе:

, или иначе:

.

.

Аналогично, для остальных Y:

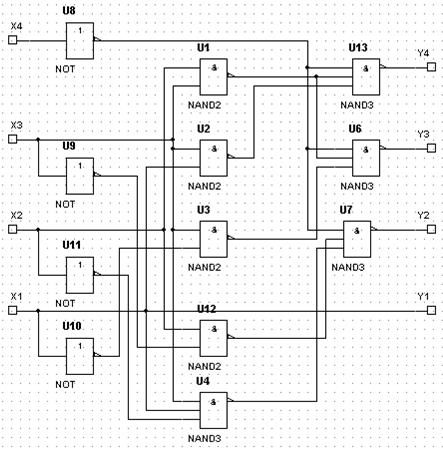

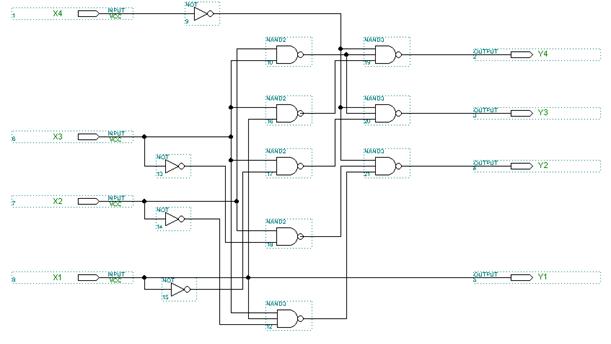

Теперь при помощи полученных логических выражений на элементах И-НЕ построим преобразователь двоичного кода в двоично-десятичный код (рис. 6.25).

Рис. 6.25 Схема преобразователя двоичного кода в двоично-десятичный код

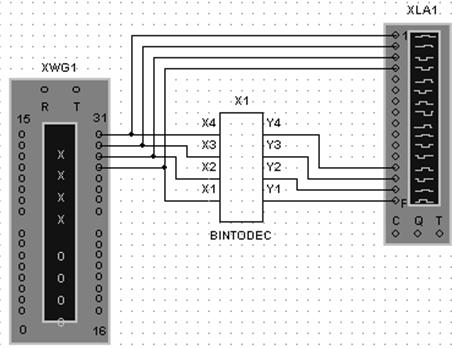

Рис. 6.26 Блок преобразователя двоичного кода в

двоично-десятичный код

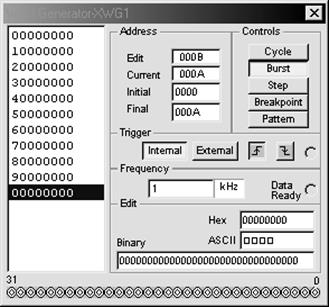

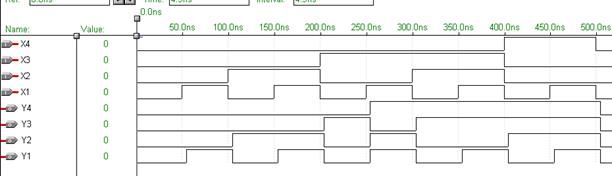

Рис. 6.27 Заданная последовательность входных сигналов

для схемы (рис. 6.20)

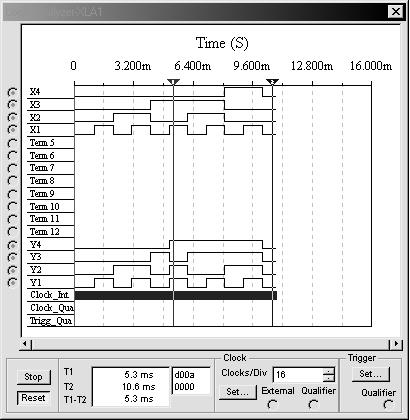

Рис. 6.28 Временные диаграммы для преобразователя двоичного кода в двоично-десятичный код

Рис. 6.29 Преобразователь двоичного кода в двоично-десятичный код в пакете MAX+Plus II

Рис. 6.30 Временные диаграммы

Рис. 6.31 Матрица временных задержек

Программа:

SUBDESIGN preobraz_dvoichnogo_v_dvoichno_desayt

(

X[3..0] : INPUT;

Y[3..0] : OUTPUT;

)

BEGIN

IF X[3..0] <= B"0100"

THEN Y[3..0] = X[3..0];

ELSE Y[0] = X[0];

TABLE

X[3..1] => Y[3..1];

B"010" => B"101";

B"011" => B"110";

B"100" => B"111";

END TABLE;

ENDIF;

END;

Примечание. В пакете Max+ Plus2 имеются микросхемы, реализующие преобразование из двоичного кода в двоично-десятичный и обратно (74184/74185).

Дата добавления: 2015-04-25; просмотров: 3035;