Архитектура типовой микросистемы

Основные типы архитектур. В большинстве современных микроЭВМ для хранения программ и данных используется одно пространство памяти. Такая организация получила название архитектуры Дж. фон Неймана—по имени математика, предложившего кодирование программ в формате, соответствующем формату данных. Программы и данные хранятся в едином пространстве, и нет никаких признаков, указывающих на тип информации в ячейке памяти. Содержимое ячейки интерпретируется оператором обработки, в качестве которого в простейшем случае выступает ЦП.

Однако почти все однокристальные микроЭВМ, представляющие класс однокристальных программируемых микроконтроллеров, выполнены по другой схеме, известной как архитектура Гарвардской лаборатории, в которой память программ CSEG (Code Segment) и память данных DSEG (Data Segment) разделены и имеют свои собственные адресные пространства и способы доступа к ним. Такое разделение, позволившее реализовать компактно кодируемый набор машинных команд, экономно использовать память программ, и было применено при разработке однокристальных микроконтроллеров первых типов, имеющих всего лишь (1—2) К байт (К = 210) управляющей памяти, расположенной на кристалле.

Дальнейшее совершенствование архитектур обоих типов состояло в выделении специального пространства данных небольшого объема, которое сегодня известно как набор программно-доступных регистров RSEG (Register Segment). В отличие от CSEG или DSEG регистры RSEG располагаются внутри ЦП в непосредственной близости от его арифметическо-логического устройства (АЛУ), что обеспечивает быстрый физический доступ к информации, хранящейся в них. В некоторые интервалы времени программа наиболее интенсивно работает лишь с небольшим объемом данных. Для временного хранения этих данных и предназначена регистровая область—набор программно-доступных регистров.

Область RSEG может быть как полностью изолирована от пространства данных DSEG, так и частично пересекаться с ним, что дает возможность рассматривать отдельные регистры МП как обычные ячейки памяти данных. Такая организация является целесообразной, если в МС поддерживается быстрый доступ ко всей или хотя бы некоторой части памяти данных DSEG.

Почти все современные МС имеют регистровые области независимо от того, к какому типу они принадлежат: неймановскому или гарвардскому. Внутренняя логическая организация RSEG очень разнообразна и играет определяющую роль в классификации архитектур. Функциональная структура регистровой области рассматривается в § 1.4. Пока отметим в ее составе лишь один регистр PC (Program Counter), который называется программным счетчиком. Данный регистр является неотъемлемой частью всех МС и связан с адресацией памяти программ. Именно он служит указателем следующего элемента программной последовательности, подлежащей выборке и исполнению.

Система ВВ в простейшем случае представляет набор адресуемых буферных схем и регистров (портов), через которые осуществляется связь с внешними и внутренними аппаратными средствами МС. Система ВВ обычно использует единый механизм адресации портов, размещенных в специальном пространстве ВВ микросистемы IOSEG (Input/Output Segment), логически изолированном от других пространств данных,—изолированный ВВ. К МС с изолированным ВВ относятся системы на базе МП КР580ВМ80, К1810ВМ86 и других, имеющих специальные наборы команд ВВ.

В некоторых системах логически изолированное пространство ВВ может отсутствовать. В этом случае в пространстве памяти данных DSEG выделяются области, в которых и размещаются порты,—совмещенный ВВ. Организация доступа к портам в таких МС ничем не отличается от процесса записи-считывания данных в память. Совмещенный ВВ используется в МС на базе МП серии К1801.

На рис. 1.2 представлены четыре типовых набора областей для хранения программ и данных. Стрелкой указан процесс изоляции отдельных областей, приводящий к появлению нового типового набора. Все наборы существуют реально, на их основе созданы те или иные серии микропроцессорных БИС. Каждый тип организации имеет свои преимущества и недостатки, учет которых позволяет создавать высокоэффективные системы различного применения.

Рис. 1.2. Типовая организация памяти и пространства ввода-вывода

Организация пространств памяти и ввода-вывода. В отличие от RSEG память программ CSEG и данных DSEG, а также область ВВ IOSEG организованы проще. В ряде случаев память МС с точки зрения программиста представляет собой линейно упорядоченный набор n-разрядных ячеек с произвольным доступом—линейная намять. Каждой ячейке набора соответствует число, называемое ее адресом. Все адреса занимают целочисленный диапазон от 0 до 2m – 1, который образует адресное пространство памяти. Разрядность адреса m обычно равна 16, 18, 20, 24 или 32. В тех случаях, когда наименьшая адресуемая единица—байт (n = 8), память имеет байтовую организацию.

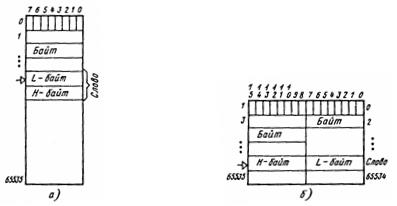

Одним из примеров МС с памятью линейной организации байтового типа является 8-разрядная система на базе МП КР580ВМ80. Команды этого МП выполняют обращение к пространству памяти емкостью 216 = 64K байт, как показано на рис. 1.3, а. В дальнейшем память МС будет представляться таким образом, чтобы ячейки со старшими адресами располагались ниже, чем с младшими. Нумерация отдельных разрядов в ячейке производится справа налево начиная с нуля, при этом разряд с нулевым номером является младшим.

Рис. 1.3. Линейная память микросистем на базе микропроцессоров КР580ВМ80 (а) и К1801ВМ1 (б)

При необходимости хранящиеся в памяти программные объекты команды и операнды (данные к командам) могут располагаться в соседних ячейках пространства памяти. Адресом объекта обычно служит наименьший из адресов ячеек, занимаемых им. Операция обращения к памяти предполагает считывание или запись всего объекта как единого целого. Например, слова в памяти МС на базе МП КР580ВМ80 хранятся в двух соседних байтах. Старшая часть слова занимает байт со старшим адресом, а младшая—байт с младшим адресом. При этом адрес младшего байта служит адресом слова (см. рис. 1.3, а).

Память большинства 16- и 32-разрядных МС также имеет байтовую организацию. Так, нижний уровень логического представления памяти МП К1810ВМ86 емкостью 1 Мбайт (М = 220) аналогичен рассмотренному выше. Однако в данном МП существует более высокий уровень организации памяти, на котором в основном и работает программист (см. § 6.3).

Очень часто организация памяти предусматривает определенные ограничения на возможное расположение многобайтовых объектов. Так, в МС на базе 16-разрядного МП К1801ВМ1, которая также имеет память с байтовым доступом емкостью 64К байт, слова в памяти могут находиться только по четным адресам, как представлено на рис. 1.3, б. Тогда при доступе к слову значение младшего разряда его адреса, указывающего на байт в слове, во внимание не принимается, т. е. такая память имеет границу слов. Порядок расположения байтов внутри слова стандартный: сначала младший, затем старший байт слова.

Организацию такого вида имеют не только пространства памяти DSEG и CSEG, но и область ВВ IOSEG.

Командный цикл. Центральный процессор осуществляет ввод, обработку и вывод данных в соответствии с программой, хранимой в CSEG.

Программа—это упорядоченная последовательность команд и данных. Процесс исполнения программы заключается в последовательном выполнении команд, образующих программу.

Команда—это функционально завершенное элементарное действие, которое определяется типом используемых данных, источником их получения, операцией над ними, приемником размещения результата, а также источником получения следующей команды. Программист рассматривает команду как одно неделимое действие. На уровне физического обмена каждая команда представляет собой ряд типовых циклов обращения к системной магистрали.

Машинное представление команды в памяти МС называется ее объектным кодом. Объектный код команды состоит из ряда нулей и единиц. Однако человеку более понятна информация, представленная в символьной форме. Поэтому наряду с объектным кодом каждой команде приписывается ее символическое обозначение, или мнемокод, который используется при написании программ человеком с последующей их перекодировкой в машинное представление. Обычно существует взаимно-однозначное соответствие между мнемокодом и объектным кодом команды.

Время, необходимое для выполнения одной команды, называется командным циклом (рис. 1.4). Командный цикл делится на две фазы: выборки и исполнения. Работа ЦП заключается в непрерывном повторении чередующихся фаз командного цикла.

Рис. 1.4. Основные фазы работы микросистемы

Основное содержание фазы выборки состоит в считывании первого байта (слова) команды из памяти МС и его ввод в специальный регистр команд IR (Instruction Register). Считывание байта (слова) происходит по адресу, хранящемуся в программном счетчике PC. Одновременно с этим содержимое PC увеличивается на 1 или 2, указывая на следующий элемент объектного кода. Фаза выборки одинакова для всех команд.

Фаза исполнения состоит в дешифрации содержимого IR и выполнении действий, определяемых этим содержимым. Состав и порядок действий фазы исполнения для каждой команды свой. Она также может включать считывание дополнительных байтов (слов) команды и соответствующего изменения PC, несколько дополнительных обращений к памяти программ и(или) данных для выборки операндов и размещения результата, циклы обращения к портам ВВ IOSEG.

В целом работа МС заключается в следующем. При включении источника питания или нажатии клавиши сброса RESET управление аппаратно передается на стартовый адрес памяти программ. Выбирается и исполняется первая команда, по результатам которой управление передается другой и т. д. При приеме специальной команды останова HLT МС приостанавливает свою работу до следующего пуска.

Дата добавления: 2019-02-07; просмотров: 839;