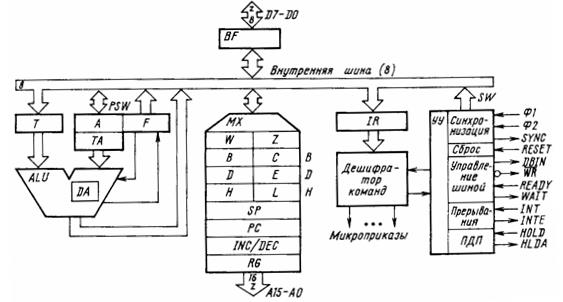

Структурная схема ВМ80

Схема однокристального 8-разрядного МП ВМ80 приведена на рис. 2.4, на рис. 2.5 дано его условное графическое обозначение.

Рис. 2.4. Схема микропроцессора ВМ80

Рис. 2.5. Условное графическое обозначение микропроцессора ВМ80

Схема содержит АЛУ, блок регистров, устройство управления и буфер данных. Обмен информацией между составными частями схемы осуществляется с помощью 8-разрядной внутренней шины. По шине передаются команды, адреса, данные, а также информация SW (Status Word) о состоянии процессора в текущем машинном цикле.

В состав интерфейса МП входят трехстабильная 16-разрядная шина адреса А15—А0, трехстабильная двунаправленная 8-разрядная мультиплексированная шина состояния/данных D7—D0, две линии двухфазной синхронизации Ф1, Ф2 и десять линий управления, из которых четыре входных, а шесть выходных. Каждая линия управления имеет свое функциональное назначение:

RESET Начальная установка

SYNC Сигнал синхронизации по машинным циклам

DBIN Строб ввода данных

WR Строб вывода данных

READY Сигнал готовности периферийных модулей к обмену

WAIT Сигнал ожидания готовности

INTE Разрешение прерывания

INT Запрос векторного прерывания

HOLD Запрос доступа к магистрали

HLDA Подтверждение доступа к магистрали

Все действия МП синхронизированы вложенными друг в друга циклами трех уровней: командными, машинными и микротактами.

Командный цикл состоит из нескольких (от 1 до 5) машинных циклов, обозначаемых М1—М5. Каждый машинный цикл представляет собой цикл обращения к системной магистрали: выборку очередного байта команды или данных из памяти, запись в память, ввод или вывод данных. Исключение составляет команда DAD (сложить HL с парой регистров). Она содержит три машинных цикла, однако только в первом цикле М1 происходит обращение к памяти, тогда как два других отводятся для исполнения команды без обращения к магистрали. Цикл М1 всегда первый и возможно единственный цикл, который реализует фазу выборки команды. Его называют также циклом FETCH. В начале каждого машинного цикла МП вырабатывает сигнал SYNC. Реализация машинного цикла возлагается на устройство управления (УУ).

Машинные циклы выполняются по микротактам, определяемым как интервал времени между двумя соседними фронтами импульсов фазы Ф1. При частоте импульсов Ф1, равной 2 МГц, длительность микротакта составляет 500 нс. Один машинный цикл включает 3—5 микротактов Т1—Т5. В течение одного микротакта исполняется один микроприказ. Обычно цикл М1 длится 4—5 тактов, циклы М2—М5 содержат 3 такта. Сигнал SYNC выдается в первом микротакте каждого машинного цикла.

Для нормального функционирования МС недостаточно управляющих сигналов. Так, в данном наборе сигналов нельзя отличить циклы обращения к памяти от циклов ВВ. Расширение числа управляющих сигналов выполнено с помощью специального 8-разрядного слова состояния SW (Status Word), которое выдается через шину данных в первом такте Т1 каждого машинного цикла. Если сигналы управления и состояния используются в основном для управления процессом исполнения машинного цикла, то сигналы SW кодируют тип машинного цикла. Последние определяют вид информации и направление ее движения через шину данных. Согласно условию SYNC∙Ф1 = 1 слово состояния SW фиксируется во внешнем регистре и используется для управления МС на уровне машинных циклов.

В состав SW входят следующие сигналы:

DO (INTA) Подтверждение прерывания. Выделяет машинные

циклы обслуживания системы прерываний

D1 (WO) Запись/вывод. Свидетельствует о выдаче в данном

цикле данных из МП

D2 (STACK) Стек. Сигнал активен, если выполняется обращение

к cтеку, т.е. addr = (SP)

D3 (HLTA) Подтверждение останова. Информирует о переходе

МП в данном машинном цикле в состояние HALT

D4 (OUT) Вывод. Свидетельствует об обращении к портам

вывода. Адрес порта установлен на младшей и

старшей половинах шины адреса

D5 (М1) Цикл М1. Обозначает первый машинный цикл

каждого командного цикла

D6 (INP) Ввод. Свидетельствует об обращении к портам ввода.

Адрес порта установлен на младшей и старшей

половинах шины адреса

D7 (MEMR) Чтение памяти. Выделяет циклы чтения данных

из памяти

Всего возможно 11 наборов сигналов SW, разбивающих множество машинных циклов на 11 типов:

Тип Мнемоника Функциональное назначение

1 FETCH Цикл М1 приема первого байта команды

в регистр команд IR

2 MEMORY__READ Цикл чтения данных из памяти по адресу,

определяемому PC, ВС, DE, HL или addr16

3 MEMORY__WRITE Цикл записи данных в память по

адресу, определяемому ВС, DE, HL или addr16

4 STACK__READ Цикл чтения из стека, чтение памяти

по адресу, определяемому SP

5 STACK__WRITE Цикл записи в стек, запись в память по

адресу, определяемому SP

6 INPUT Цикл ввода данных из порта в аккумулятор А

7 OUTPUT Цикл вывода данных из аккумулятора в порт

8 INTERRUPT__М1 Первый цикл подтверждения прерывания

9 HALT Цикл останова МП

10 HALT__INTERRUPT Первый цикл подтверждения прерывания

в состоянии HALT

11 INTERRUPT Второй и третий циклы подтверждения прерывания

Описание содержания типовых циклов обращения к магистрали представлено в табл. 2.6.

Таблица 2.6

| Слово состояния | FETCH | MEMORY __READ | MEMORY __WRITE | STACK __READ | STACK __WRITE | INPUT | OUTPUT | INTER-RUPT __M1 | HALT | HALT__ INTERRUPT | INTER-RUPT |

| D0 (INTA) | |||||||||||

D1 (  ) )

| |||||||||||

| D2 (STACK) | |||||||||||

| D3 (HLTA) | |||||||||||

| D4 (OUT) | |||||||||||

| D5 (M1) | |||||||||||

| D6 (INP) | |||||||||||

| D7 (MEMR) | |||||||||||

| Команды шины управления | MEMR | MEMR | MEMW | MEMR | MEMW | I/OR | I/OW | INTA | — | INTA | INTA |

Зная содержание допустимого множества машинных циклов, нетрудно построить их последовательности, реализующие ту или иную команду МП. Машинные циклы удобно представлять в следующем формате:

Номер Тип Состояние Состояние

цикла цикла АВ DB

STAX В—запомнить содержимое А в памяти по адресу, определяемому регистровой парой ВС:

M1 FETCH (PC) áSTAX Вñ

М2 MEMORY__WRITE (ВС) (А)

CALL addr—вызов подпрограммы по адресу addr:

M1 FETCH (PC) áCALLñ

М2 MEMORY__READ (PC) + 1 addr LB

M3 MEMORY__READ (PC) + 2 addr HB

M4 STACK__WRITE (SP) – 1 (PC) + 3 HB

M5 STACK__WRITE (SP) – 2 (PC) + 3 LB

OUT port—вывод данных из аккумулятора в порт port:

M1 FETCH (PC) áOUTñ

М2 MEMORY__READ (PC) + 1 port

M3 OUTPUT port port (A)

Во время выполнения каждого машинного цикла МП принимает или выдает информацию по шине данных. Направление передачи совпадает со стробами DBIN и  . В соответствии с этим все типы циклов можно разбить на циклы чтения и записи, связанные с вводом и выводом информации из МП:

. В соответствии с этим все типы циклов можно разбить на циклы чтения и записи, связанные с вводом и выводом информации из МП:

Циклы чтения Циклы записи

1 FETCH

2 MEMORY__READ 3 MEMORY__WRITE

4 STACK__READ 5 STACK__WRITE

6 INPUT 7 OUTPUT

8 INTERRUPT__M1

10 HALT__INTERRUPT

11 INTERRUPT

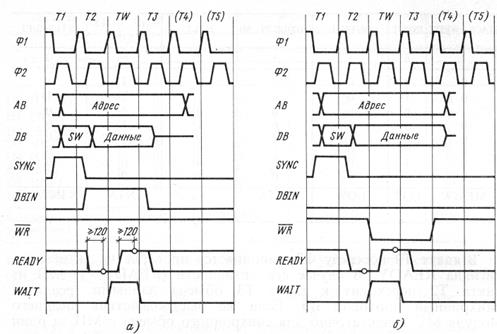

Временные диаграммы циклов приведены на рис. 2.6.

Рис. 2.6. Временные диаграммы циклов чтения (а) и записи (б) микропроцессора ВМ80

В такте Т2 по срезу Ф2 выполняется проверка на активность сигнала READY. В случае его активности (READY = 1) МП из такта Т2 переходит к такту Т3 обмена данными, реализуя синхронный протокол ВВ. Если же быстродействия внешнего модуля МС недостаточно для синхронного обмена с МП за один такт, он может задержать момент перехода к такту Т3 на целое число тактов TW. Для этого достаточно установить в 0 сигнал READY до момента его первой проверки и удерживать в этом состоянии то время, которое необходимо модулю для подготовки к обмену. В случае READY = 0 МП из такта Т2 переходит в режим ожидания WAIT, о чем свидетельствует появление высокого уровня напряжения на линии WAIT. В данном режиме МП генерирует циклы TW ожидания сигнала READY и реализует асинхронный протокол обмена с внешними модулями МС. Продолжительность режима WAIT определяется длительностью действия напряжения низкого уровня на линии READY, которая контролируется в каждом такте TW по срезу Ф2.

При обнаружении высокого уровня напряжения сигнала READY МП из такта TW переходит к выполняющему обмен такту Т3. При этом сигнал WAIT устанавливается в 0. Для нормальной работы МП установку сигнала READY в 0 или 1 рекомендуется производить более чем за 120 нс до среза Ф2 и удерживать по крайней мере до его проверки.

Микропроцессор имеет несложные встроенные средства обслуживания запросов на прерывания с тремя управляющими сигналами:

INT Запрос на прерывание

INTE Разрешение прерывания

SW.INTA Подтверждение прерывания

Управляемый программно с помощью команд ЕI и DI сигнал разрешения прерывания INTE маскирует вход INT запроса на прерывание. При условии INT∙INTE = 1, которое проверяется в последнем такте каждого командного цикла (за исключением команды ЕI), МП должен перейти к процедуре обслуживания запроса. Благодаря этому гарантируется выполнение любой команды.

Процедура обслуживания запроса на прерывание заключается в идентификации источника прерывания, сохранении точки возврата в системном стеке и переходе к соответствующей подпрограмме обслуживания прерывания. Она начинается с машинного цикла INTERRUPT__M1, который похож на цикл FETCH, но отличается от него тем, что вместо сигнала SW.MEMR активен сигнал SW.INTA. Отличие самого цикла от цикла FETCH заключается также в том, что сбрасывается флаг INTE и PC не инкрементируется. Это обеспечивает сохранность точки возврата и игнорирование всех последующих запросов до специального разрешения командой ЕI. В остальном цикл INTERRUPT__M1 не отличается от цикла FETCH и состоит из ввода первого байта команды. Далее МП работает как обычно за исключением того, что при INT = 1 сигнал SW.MEMR заменяется на SW.INTA, что предотвращает изменение PC.

Обычно в этом цикле генерируется команда CALL addr, в которой addr определяется источником прерывания и указывает на начало программы обслуживания. После выдачи команды CALL addr следует установить на линии INT напряжение низкого уровня, что обеспечит переход к обычным машинным циклам с сигналом SW.MEMR. Поэтому в фазе исполнения команды CALL addr будут сформированы два цикла STACK__WRITE, которые обеспечат запись точки возврата прерванной программы в системный стек.

Для ускорения процедуры обработки прерываний применяется специальный укороченный вариант команды CALL addr—команда RST n, где addr = 8n, n = 0—7.

Использование команды RST n подразумевает резервирование первых 64 (8´8) байтов памяти под таблицу входов в подпрограммы обслуживания прерываний. Обычно по адресам 8n, n = 0—7, находятся команды JMP, передающие управление на подпрограммы обслуживания прерываний. Модификация адресной части команд JMP позволяет оперативно изменять входы в подпрограммы. Возврат из подпрограмм обслуживания прерывания обычно выполняется с помощью командной последовательности

ЕI ;Разрешение прерывания, INTE1

RET

В МП предусмотрены простейшие средства для управления захватом шины. Процедура захвата шины инициализируется внешними средствами установкой сигнала HOLD. Микропроцессор реагирует на этот сигнал по срезу Ф2. По фронту Ф1 в такте Т3 при вводе данных или в такте, следующем за Т3, при выводе данных МП формирует сигнал HLDA, а по фронту Ф2 в этом же такте шина данных переводится в высокоомное z-состояние. Шина адреса всегда переводится в z-состояние в такте, следующем за Т3. Такты Т4, Т5 и более (для команды DAD) совмещаются по времени с состоянием HOLD. Выход из состояния захвата производится после такта Т5 при обнаружении низкого уровня напряжения на линии HOLD. Затем МП переходит к исполнению такта Т1 следующего машинного цикла.

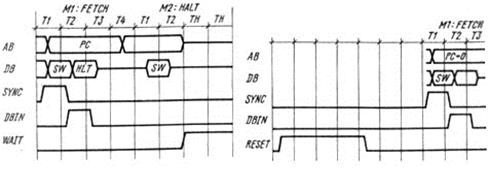

В цикле HALT обмена информации через шину данных не происходит. Этот цикл используется для вхождения в режим программного останова. Машинный цикл HALT следует за циклом FETCH, в котором принята команда HLT. При этом шина адреса и шина данных переводятся в z-состояние, а на выходе WAIT генерируется напряжение высокого уровня, как показано на рис. 2.7.

| Рис. 2.7. Временные диаграммы машинного цикла HALT | Рис. 2.8. Временные диаграммы перезапуска микропроцессора ВМ80 |

Находясь в состоянии HALT, МП не теряет возможности реагировать на сигнал HOLD, генерируя сигнал HLDA. Из состояния останова МП может быть выведен двумя путями: перезапуском сигналом RESET и прерыванием INT при разрешенной маске INTE. Временные диаграммы перезапуска сигналом RESET приведены на рис. 2.8. При перезапуске сбрасывается маска INTE и управление передается на стартовую ячейку, в качестве которой применяется ячейка с нулевым адресом.

Дата добавления: 2019-02-07; просмотров: 932;