Регистры микропроцессора

Функциональная неоднородность регистров. Регистровую область или набор программно-доступных регистров RSEG можно рассматривать как скоростное ОЗУ малой емкости, входящее в состав МП. Набор используется для временного хранения данных и адресной информации, контролируемых программистом. Число регистров колеблется от 4 до 32. Короткая адресация регистровой области и быстрый доступ к ней обеспечивают создание эффективно исполняемых программ.

Регистры МП функционально неоднородны: одни служат для хранения данных или адресной информации, другие—для управления работой ЦП. В соответствии с этим все регистры можно разделить на регистры данных, указатели и регистры специального назначения. Регистры данных участвуют в арифметических и логических операциях в качестве источников операндов и приемников результата, адресные регистры или указатели используются для вычисления адресов данных и команд, расположенных в основной памяти. Специальные регистры служат для индикации текущего состояния ЦП и управления режимами его работы.

Функциональная специализация регистров определяется системой команд. При слабой специализации часть регистров обычно применяется для хранения как операндов, так и адресов. Их называют регистрами общего назначения (РОН).

Функциональная неоднородность RSEG связана с широким использованием неявной (подразумеваемой) адресации регистров, которая, в свою очередь, определяется стремлением к созданию коротких программ. Функциональная специализация затрудняет программирование, так как требует учета особенностей организации регистрового набора, присущих данному МП. Однако в результате объектный код команд исполняется быстрее и для его хранения требуется меньшая память.

На уровне символического кодирования команд для прямой ссылки на конкретные регистры МП им присваиваются имена, например А, В, С, D, SP, X, WP или R0, R1, R2 и т. д. Обычно эти имена отражают функциональное назначение регистра и способствуют пониманию символьных команд.

Адресные регистры. Ряд функций, которые возлагаются на RSEG, распределяются между регистрами МП. Так, для реализации различных методов непрямой (вычисляемой) адресации данных в составе блока регистров применяются адресные регистры-указатели. Регистр косвенного адреса DP (Data Pointer) содержит непосредственно адрес операнда, регистр базы ВР (Base Pointer) используется для хранения начальных адресов массивов и записей, содержимое индексного регистра X (Index) является относительным адресом (индексом) операнда (рис. 1.13). Среди адресных регистров следует также отметить регистры автоинкрементной и автодекрементной адресации, которые автоматически увеличивают или уменьшают свое состояние до или после выполнения операции доступа в соответствии с длиной адресуемого ими операнда, и регистры расширения адресного пространства или указатели сегментов и страниц. (Подробно регистры данного типа будут рассмотрены в гл. 6.)

| Рис. 1.13. Адресные регистры МС | Рис. 1.14. Операции PUSH (а) и POP (б) типового стека |

Очень важной является функция хранения адреса следующего подлежащего выборке элемента программной последовательности. Эту функцию выполняет программный счетчик PC. Большая часть команд выполняется последовательно в порядке возрастания адресов памяти. Во время выборки очередной команды содержимое PC увеличивается на 1 или 2 для указания следующего байта или слова в последовательности команд. Процесс адресации следующего элемента командной последовательности, как правило, осуществляется неявно. В типовой команде, например,

MOV dst, src ;dstsrc

где dst и src—указатели приемника и источника данных, какие-либо сведения об адресе следующей команды отсутствуют. Поэтому функция PC возлагается на конкретный регистр, содержимое которого автоматически инкрементируется после очередной выборки элемента командной последовательности. Изменение последовательности процесса выборки команд осуществляется специальными командами передачи управления, связанными с загрузкой PC адресом, отличным от адреса следующей команды.

В системах с предварительной выборкой команд каждый переход также связан с очисткой буфера предварительной выборки. Регистр PC относится к классу указателей с автоинкрементированием.

Частным случаем регистра с автомодификацией является указатель стека SP (Stack Pointer). Он необходим для организации системного стека SSEG, который предназначен для хранения адресов возвратов и состояний процессора при вызове подпрограмм и обслуживании прерываний. Стек может также использоваться для временного хранения локальных переменных и передачи входных или выходных параметров при вызовах подпрограмм.

Стек—это область памяти с доступом типа «последний пришел—первый вышел» или LIFO (Last Input—First Output). Стек обычно заполняется в сторону уменьшения адресов, при этом указатель стека показывает на последнюю заполненную ячейку стека—вершину стека TOS (Top of Stack). Такой стек называется типовым, так как именно он применяется в большинстве МС. При записи в стек нового элемента данных (операция PUSH) содержимое SP уменьшается на 1 или 2 в зависимости от длины элемента (байт или слово) и затем используется в качестве адреса новой вершины, в которую заносится элемент. При считывании элемента данных из стека (операция POP) сначала считывается содержимое TOS, а затем содержимое SP увеличивается на 1 или 2 для адресации новой вершины стека. Работа стека показана на рис. 1.14. Исключительные удобства, предоставляемые стеком при вызове подпрограмм, привели к тому, что практически все современные МП имеют средства для его построения в виде SP.

При использовании стека для хранения локальных переменных и обмена параметрами между вызываемой и вызывающей процедурой может оказаться полезным специальный адресный регистр, указывающий на начало области параметров в стеке (см. рис. 1.13). Регистр с таким функциональным назначением называется указателем кадра FP (Frame Pointer). Действительно, значение SP непрерывно меняется, поэтому применять его в качестве точки отсчета при доступе к данным в стеке крайне неудобно. Процедуру доступа можно значительно упростить, если функцию точки отсчета отдать специально зарезервированному для этой цели указателю FP, который принадлежит к классу базовых регистров.

Специальные регистры. При выполнении команд АЛУ генерирует ряд сигналов-признаков, характеризующих результат операции. Функцию хранения этих сигналов, а также некоторых других выполняет специальный регистр слова состояния программы PSW (Program Status Word). С каждым признаком результата операции связывается одноразрядная переменная—флажок. Флажки группируются во входящее в состав PSW поле кода условия СС (Condition Code). Типовой состав флажков-признаков результата операции F = Fn-1Fn-2…F1F0 следующий:

| CF (Carry Flag) | Флажок переноса из старшего разряда АЛУ. Флажок CF используется наиболее часто. При арифметических операциях CF = Cn, при сдвигах CF = F-1 или Fn выдвинутое при операциях значение младшего или старшего разряда |

| ZF (Zero Flag) | Флажок признака нуля,

|

| SF (Sign Flag) | Флажок знака результата, SF = Fn-1. Применяется при целочисленной арифметике со знаком |

| AF (Auxiliary Carry Flag) | Флажок дополнительного переноса или переноса из младшей тетрады, AF = C4 |

| OF (Overflow Flag) | Флажок арифметического переполнения. При выполнении арифметики в дополнительном коде OF = CnÅCn-1 |

| PF (Parity Flag) | Флажок четности результата,

|

Здесь Сi—входной перенос в i-й разряд, который одновременно является выходным переносом из (i – 1)-гo разряда сумматора АЛУ.

Удобно, если поле условия СС содержит один или несколько флажков пользователя U0, U1,..., функциональное назначение которых определяет он сам. Обычно эти флажки служат для связи между отдельными частями программы. Состояние поля условия СС тестируется различными командами условного типа.

В состав PSW входит также ряд специальных флажков, управляющих работой МП:

| IF (Interrupt Flag) | Маски и приоритеты прерываний, а также условия реакции на прерывания |

| TF (Trace Flag) | Флажок пошаговой трассировки, маска специального прерывания |

Регистр PSW включает и различные модификаторы команд (например, флажок направления DF в МП К1810ВМ86), изменяющие реакцию МП на отдельные команды. Для обеспечения особых условий выполнения программ в PSW вводят специальный флажок, определяющий эти условия. Так, флажок  (Halt/User) в МП К1801ВМ2 служит для разрешения особых условий выполнения программ и реализации директив пультового терминала.

(Halt/User) в МП К1801ВМ2 служит для разрешения особых условий выполнения программ и реализации директив пультового терминала.

Упаковка всех флажков в одно слово дает возможность организовать их быструю засылку в память с последующим восстановлением. В некоторых сложных МП специальных регистров может быть несколько.

Регистры данных. Наиболее типичным представителем регистров данных является аккумулятор A (Accumulator), который используется для временного хранения исходных операндов и промежуточных результатов. С аккумулятором связано большинство команд арифметической и логической обработки. Ссылка на него, как правило, производится неявно с помощью кода операции:

LDA src ;Asrc

Неявная адресация позволяет не указывать в командах местоположения одного из операндов src и (или) результата операции dst, что существенно уменьшает длину их кода:

ANA src ;AA AND src

Это очень важно в условиях ограниченной пропускной способности системной магистрали, особенно для 8-разрядных МС. Поэтому большинство первых МП, например КР580ВМ80, имели аккумулятор и были ориентированы на его интенсивное использование.

В составе МП может находиться один или несколько аккумуляторов. Так, в МП МС6809 два аккумулятора—А и В. Они имеют одноадресную систему команд, так как в коде команды явно указывается адрес лишь одного операнда. При этом предполагается, что источником другого операнда служит аккумулятор. Он же, как правило, применяется и для хранения результата операции:

ADDA src ;AA + src

SUBB src ;BB – src

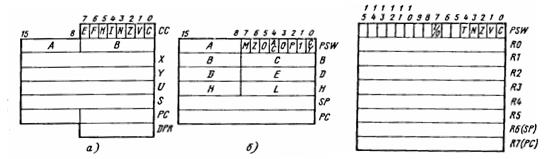

Влияние аккумулятора на организацию МС настолько велико, что включение А в состав RSEG стало типичным, поэтому системы с аккумулятором выделили в отдельный класс. На рис. 1.15, а представлен минимальный набор программно-доступных регистров 8-разрядной МС аккумуляторного типа, в состав которых кроме аккумулятора входят индексный регистр X, указатели SP и PC, а также PSW с одним флажком переноса CF. Наличие полноразмерного индексного регистра в составе RSEG объясняется его функциональной универсальностью при адресации данных. Действительно, полноразмерный индексный регистр может выполнять функции ВР, а при нулевом значении прямого компонента, задаваемого непосредственно в команде,—функции DP.

Рис. 1.15. Типовые составы RSEG:

а—с аккумулятором; б—с регистрами общего назначения; в—с рабочими областями; г—с вычислительным стеком

Другим примером регистров данных служат рабочие регистры R0, R1,... В отличие от аккумулятора они адресуются явно и могут интерпретироваться как сверхскоростные регистровые ОЗУ данных. Рабочие регистры используются в операциях как совместно с аккумулятором, так и без него. Некоторые рабочие регистры совмещают свою функцию хранения данных с функцией их адресации. В этом случае они приобретают функции РОН (МП К1801ВМ1). При необходимости для образования полноразмерного указателя регистры данных объединяются в пары. Ориентация архитектуры на рабочие регистры приводит к полутораадресной системе команд:

MOV dst, reg ;dstreg

OR reg, src ;regreg OR src

В полутораадресных командах допускается только один операнд, хранящийся в памяти МС, тогда как другой должен находиться в регистровой области. Для двухместных операций приемником результата, как правило, является регистр—источник одного из операндов. Типовой минимальный набор RSEG для 8-разрядной МС с регистрами общего назначения приведен на рис. 1.15, б.

В ряде МП, предназначенных для работы в реальном масштабе времени, предусмотрены не один, а два (К1816ВЕ48) или даже четыре (К1816ВЕ51) набора рабочих регистров, один из которых резервируется для системных целей или обработки прерываний, а все остальные—для прикладных задач пользователя. В каждый момент времени доступен только один набор рабочих регистров, выбираемый специальным указателем WP (Work Pointer). Переключение доступного набора связано с перезагрузкой малоразрядного указателя WP.

Расширение разрядности указателя WP до полного размера адресного регистра и отображение набора рабочих регистров на основную память данных с базой WP приводит к типовой архитектуре с рабочими областями (см. рис. 1.15, в). Однако при передаче функции промежуточного хранения данных, выполняемой ранее RSEG, DSEG, теряется быстрый доступ к промежуточным данным. Решение этой проблемы связано с реализацией части основной памяти данных на одном кристалле с ЦП и размещением рабочих областей в этом внутреннем сегменте ОЗУ.

Передача функции аккумулятора вершине стека TOS приводит к стековым архитектурам. Стековая организация МС дает возможность построить безадресные машины, объектный код которых имеет наименьшую длину. Безадресные команды стековой архитектуры оперируют элементами, находящимися на вершине стека и непосредственно под ней:

DEC ;PUSH(POP – 1)

ADD ;PUSH(POP + POP)

При выполнении операций исходные операнды извлекаются из стека, а результат передается на вершину TOS. Стековая архитектура обладает высокой вычислительной эффективностью [41], однако в классической форме она большого практического распространения не нашла. Это объясняется тем, что стек обычно размещается в основной памяти, доступ к которой требует отдельного цикла обращения к системной магистрали.

Для уменьшения времени доступа к стеку он должен быть физически приближен к АЛУ, например, за счет реализации на одном кристалле с ЦП внутренней памяти данных и размещении в нем стека. Совмещение стека с внутренней частью памяти может привести к сокращению разрядности указателя SP.

В другом случае в состав архитектуры вводят специальный стек, который размещается в регистровой области МП и используется исключительно для промежуточного хранения данных. Он обладает быстрым доступом и называется вычислительным. Глубина вычислительного стека невелика—составляет 3—8 машинных слова. Прямой доступ к содержимому указателя вершины вычислительного стека, как правило, отсутствует. Манипуляция содержимым указателя выполняется только через запись-считывание данных из стека. Примерный состав RSEG 8-разрядной МС с вычислительным стеком из трех регистров А, В, С приведен на рис. 1.15, г. Регистровые наборы такого типа можно встретить только в самых современных архитектурах МС [5].

Регистровые наборы микропроцессоров, выпускаемых промышленностью. Организация RSEG реальных МП отличается от приведенных выше типовых составов. Выпускаемые промышленностью МП, как правило, результат компромиссного выбора между несколькими типами организаций и, следовательно, могут быть отнесены к тому или иному классу лишь условно. Рассмотрим несколько примеров таких МП.

Приведенные на рис. 1.15 типовые наборы являются минимальными. Как правило, они подвергаются дальнейшему расширению в соответствии с теми или иными практическими соображениями. Так, расширение набора с аккумулятором путем прямого дублирования его состава приводит к регистрам МП МС6809 фирмы Motorola [41], который представлен на рис. 1.16, а. В их составе два указателя стека S, U, два индексных регистра X, Y и два аккумулятора А, В. Набор дополнен также регистром выбора страницы DPR. Значительно расширен состав PSW. Другой путь увеличения аккумуляторного набора, выбранный фирмой Intel, привел к МП типа 8080/85А (рис. 1.16, б). К минимальному составу был добавлен блок из четырех 8-разрядных РОН В, С, D, Е, образующих попарно два 16-разрядных адресных указателя В и D. Расширились и функции типового индексного регистра H, состоящего из двух 8-разрядных регистров Н и L. Таким образом, оба МП следует отнести к классу приборов аккумуляторного типа, но с расширенными возможностями.

| Рис. 1.16. Регистры микропроцессоров МС6809 (а) и 8080/85А (б) | Рис. 1.17. Регистры микропроцессоров К1801ВМ1/ВМ2 |

Архитектура ЦП однокристальных микроЭВМ типов К1816ВЕ48/ВЕ51 тоже имеет элементы организации аккумуляторного типа, которая расширена набором из восьми рабочих регистров. Если в приборе К1816ВЕ48 [61] предусмотрено два набора, то в К1816ВЕ51 [64] их уже четыре. Два первых регистра в наборах являются РОН и, следовательно, могут быть использованы для адресации данных в ОЗУ. Наборы располагаются в области внутренней памяти данных, как это предусмотрено архитектурой с рабочими областями. Однако их размещение в памяти данных строго регламентировано, поэтому для выбора набора используется одно- или двухразрядный указатель BS, входящий в состав PSW. Существует также ряд ограничений на размещение системного стека, который находится во внутреннем ОЗУ. (Более подробно организация однокристальных микроЭВМ данного типа рассмотрена в гл. 4.)

К МП с РОН принадлежат К1801ВМ1/ВМ2 [61] и им подобные, совместимые по архитектуре с ЦП мини-ЭВМ PDP-11. Практическая реализация 8-разрядных архитектур с РОН затруднена из-за сложностей, возникающих при кодировании системы команд. Поэтому архитектуры такого типа реально существуют только для 16-разрядных систем. На рис. 1.17 представлен базовый состав RSEG микропроцессоров К1801ВМ1/ВМ2, содержащий восемь 16-разрядных РОН R0—R7. Все регистры предназначены для хранения и данных, и адресной информации. Два старших выполняют также функции указателей SP и PC.

Применение РОН дает возможность создавать регулярную систему команд, большинство из которых используют любой регистр многими способами. Поэтому ряд 16- и 32-разрядных МП был ориентирован на широкое применение РОН. К их числу относятся такие МП, как Z8001/02 фирмы Zilog [41].

Как уже отмечалось, стековая организация еще не получила широкого распространения в промышленных приборах. Однако уже можно назвать некоторые процессоры, имеющие вычислительные стеки. Это прежде всего сопроцессор числовых данных 8087 (рис. 1.18) [61], блок рабочих регистров которого организован дополнительно в виде стека из восьми 80-разрядных элементов. Вершина стека адресуется с помощью 3-разрядного указателя ST, входящего в состав слова состояния SW. Все элементы рабочей области могут адресоваться либо явно как регистры ST0—ST7, отсчитываемые от вершины стека, либо неявно с помощью указателя ST. Программист может условно разделить регистровый блок на вычислительный стек и стандартные рабочие регистры, используя различные способы доступа к ним. Кроме рабочих регистров в RSEG числового сопроцессора входят указатели, регистры управления и состояния.

Рис. 1.18. Регистры сопроцессора 8087

Приведенных примеров вполне достаточно, чтобы показать, как разнообразны по своей структуре регистровые наборы МП, выпускаемые промышленностью. Однако несмотря на это многообразие все же удается найти возможность для их сравнения и оценки с помощью рассмотренных в данном параграфе типовых наборов RSEG.

Адресация данных

Представление адресной информации. Источниками и приемниками операндов команд служат регистровая память RSEG, память данных DSEG, а также порты ВВ IOSEG. В дальнейшем для обозначения какого-либо элемента регистровой области будем использовать символ reg, адреса системной памяти—addr, порта ВВ—port. Адрес операнда, считываемого или размещаемого в одном из пространств МС, называется исполнительным.

Исполнительные адреса строятся по сведениям, заложенным в командах. Метод построения исполнительного адреса называется способом адресации (mod). Примером одного из наиболее простых способов адресации служит прямое указание полного исполнительного адреса в команде. Однако такой способ адресации, обычно называемый прямым, оказывается неэффективным во многих случаях. В частности, при прямой адресации манипуляция исполнительными адресами связана с модификацией программы, что не всегда удобно, а иногда и невозможно.

Для повышения эффективности адресации операндов разработан ряд способов задания исполнительного адреса. Каждый способ эффективен только в конкретной ситуации размещения данных. Правильный выбор и использование всего набора позволяет обеспечить эффективный доступ к структурированным данным, таким как массивы, стеки, списки, а также перемещаемость программ и данных на этапе загрузки и выполнения, сократить длину программного кода и число обращений к магистрали, адресовать большую основную память в условиях малой разрядности ЦП.

Необходимость адресовать память большой емкости при коротком слове данных придает проблеме адресации в МС особо острый характер. Поэтому механизмы адресации памяти в МС оказываются наиболее совершенными и требуют минимального числа обращений к магистрали.

Сведения об адресе операнда могут быть заложены в команду в двух формах: явной и неявной. Явная форма предполагает наличие в команде специального поля, называемого адресной частью команды, в котором эти сведения содержатся. Неявная форма обеспечивает передачу адресной информации через именную часть команды или код операции (ОР), т. е. сама операция несет определенные сведения о месте нахождения одного или всех операндов, используемых в ней.

Явная форма представления адресной информации более гибкая. Она позволяет связывать с одной операцией множество адресов, что повышает ее эффективность. Однако эта форма требует увеличения длины машинной команды, что снижает эффективность объектного кода. Неявная форма связывает часть адресной информации с операцией, сужая область ее действия, но длина машинной команды при этом существенно уменьшается. В реальных командах, как правило, применяются обе формы представления адресной информации. Широко распространена и такая форма представления адресных сведений: часть информации о месте нахождения одного и того же операнда передается в неявной форме, остальная информация представляется в адресном поле в явной форме.

В общем случае кодирование адресной информации операнда в команде сводится к указанию способа адресации mod и числовой информации, используемой при этом способе. Способ адресации как часть адресной информации может кодироваться в явной и неявной формах. Общепризнанной является явная форма представления mod, при которой в адресной части машинной команды резервируется специальное поле, а на уровне символьного кодирования—ряд специальных суффиксов, префиксов и указателей в поле операндов: #, @, %, (...), (...)+, –(...) и т. д. Например:

.disp ;oper = (PC + disp)

(reg)+ ;oper = (reg), regreg + 1

@addr ;oper = ((addr))

#data ;oper = data

При неявной форме кодирования способ адресации передается ОР, тогда как дополнительная информация представляется явно. Примерами такого представления служат команды

STAX reg ;(reg)A

MVI reg, data ;reg#data

BR disp ;PCPC + disp

Они эквивалентны следующим командам:

ST A, @reg

MOV reg, #data

JMP .disp

Однокомпонентные способы адресации. Самым простым способом задания места расположения данных является включение его полного адреса в состав команды (рис. 1.19, а). Применительно к основной памяти данных МС такой способ адресации называется прямым (ptr = addr). Прямая адресация дает возможность явно указать на любую конкретную ячейку памяти во всем адресном пространстве DSEG. Примером команды с прямой адресацией служит

INC addr ;addr(addr) + 1

Рис. 1.19. Способы адресации данных:

а—прямая; б—регистровая; в—прямая адресация портов; г—непосредственная

Для явного задания полного m-разрядного адреса в команде должно быть выделено m разрядов. С целью сокращения числа разрядов во многих системах используется короткий вариант прямой адресации, обеспечивающий непосредственный доступ к ограниченной, заранее определенной области памяти. Как правило, это наиболее важная нижняя и (или) верхняя часть адресного пространства. Короткая прямая адресация может быть достаточно эффективной в МС гарвардского типа.

Неявная форма представления прямой адресации приводит к указанию конкретной ячейки системной памяти. Такой способ адресации используется крайне редко.

Основной недостаток прямой адресации состоит в том, что манипуляция адресом связана с изменением объектного кода, которое не всегда возможно. Например, в МС гарвардского типа доступ к CSEG с целью модификации объектного кода логически запрещен. В МС неймановского типа доступ к кодовому сегменту может быть тоже запрещен, но уже на физическом уровне, так как исполняемая программа записана в ПЗУ. В любом случае модификация объектного кода нежелательна, что связано со значительными трудностями при его анализе, например, с целью отладки. Использование прямой адресации ограничено случаем, когда расположение данных в памяти известно заранее и не изменяется в процессе исполнения программы. Для МС гарвардского типа могут быть предусмотрены специальные варианты доступа к CSEG с прямой адресацией для считывания констант и постоянных таблиц, которые могут храниться в ней. При этом выбор кодового сегмента кодируется неявно. Применительно к регистровой памяти вариант прямого включения адреса в команду приводит к регистровой адресации (ptr = reg) (рис. 1.19,б). Для прямой ссылки на регистр, входящий в состав небольшой регистровой памяти МС, обычно требуется несколько бит. Кроме того, отсутствуют циклы обращения к системной магистрали. Все это обеспечивает большую эффективность регистровой адресации. Распределение данных по регистрам легко контролируется программистом и не вызывает особых затруднений при ссылке на них. Приведем примеры команд с регистровой адресацией:

MOV reg, addr ;reg(addr)

NEG reg ;reg – reg

В МС широко распространена неявная форма регистровой адресации, когда код операции подразумевает вполне конкретный регистр, например аккумулятор А:

LDA addr ;эквивалентно MOV A, addr

ANA reg ;эквивалентно AND A, reg

На уровне мнемокода регистровая адресация отличается от прямой использованием специальных имен, зарезервированных для обозначения регистров A, X, Ri и т. д. В некоторых системах вводится специальный символ регистровой адресации %:

CLR %n ;Rn0

Здесь n—целое, указывающее на конкретный регистр области. Обычно регистровая адресация—единственный способ доступа к пространству регистров МС.

Прямая адресация портов (ptr = port) используется для адресации изолированного пространства портов ВВ (рис. 1.19, в). Доступ к портам обычно задается неявно кодом операции:

IN port ;Aport

OUT port ;portA

Иногда для этой цели применяют резервные имена портов:

ANL Рn ;PnA AND Pn, n = 0—7

Очень часто прямая адресация портов является единственным способом доступа к пространству ВВ. Встречается также вариант прямой короткой адресации портов, например, в системе команд К1810ВМ86.

В некоторых случаях источником данных служит сама команда (рис. 1.19, г). Тогда говорят о непосредственной адресации (prt = #data), которая позволяет задавать константы как часть команды:

MOV reg, #data ;regdata

ADD reg, #data ;regreg + data

Для более эффективного кодирования операций с часто используемым непосредственным операндом—литералом—обычно вводят специальные коды с неявным определением данных:

CLR reg ;reg0

INC reg ;regreg + 1

или варианты короткой непосредственной адресации:

INC reg, #sdata ;regreg + sdata

Здесь sdata может восприниматься как целое без знака или как целое со знаком. В любом случае перед выполнением операции sdata расширяется с учетом знака до полноразмерного операнда. Основной недостаток непосредственной адресацией состоит в отсутствии возможности манипуляции данными без модификации объектного кода, что привело к созданию ряда способов с вычисляемым адресом. Простейшим среди них является косвенная адресация (ptr = @addr или (addr)), схема выполнения которой показана на рис. 1.20, а. В командах с данным типом адресации используется не прямой адрес, а косвенный, указывающий на ячейку памяти с адресом операнда. Манипуляция исполнительным адресом сводится к изменению содержимого этой ячейки памяти и, следовательно, никак не связана с объектным кодом. К недостаткам косвенной адресации следует отнести двойное обращение к основной памяти и большую разрядность поля, отводимого под косвенный адрес.

| Рис. 1.20. Способы адресации данных: a—косвенная; б—косвенная регистровая; в— косвенная регистровая адресация портов | Рис. 1.21. Способы адресации с автомодификацией: а—автоинкрементная; б—автодекрементная; в—преавтоинкрементная; г—поставтодекрементная |

От вышеуказанных недостатков косвенной адресации свободен ее вариант (рис. 1.20, б), в котором в качестве области, содержащей прямой адрес, используется не основная память данных, а регистровая. При этом все другие свойства, характерные для косвенной адресации, сохраняются, что объясняет широкое применение регистровой косвенной адресации (ptr = @reg или (reg)) практически во всех МС.

Для хранения прямого адреса требуется регистр достаточной длины. В ряде МС аккумуляторного типа для этой цели предусматриваются специальные адресные регистры. В МС с РОН регистры данных при необходимости объединяются в пары для образования адресных регистров. Примерами команд с косвенной регистровой адресацией являются

CLR @reg ;(reg)0

INC @reg ;(reg)(reg) + 1

Пример неявного кодирования данного способа адресации можно привести из системы команд МП КР580ВМ80:

LDAX В ;А(ВС)

STAX D ;(DE)A

Косвенная регистровая адресация портов (рtr = @reg или (reg)) через регистр может быть полезна при доступе к пространству IOSEG (рис. 1.20, в). Благодаря этому удается использовать одну и ту же программу для ВВ через порт, адрес которого заранее неизвестен и может меняться в процессе работы МС. Примеры команд ВВ:

IN @reg ;AI0SEG(reg)

OUT @reg ;IOSEG(reg)A

Для пошагового просмотра таблиц и списков удобно применять косвенную регистровую адресацию. Настройка на следующий адрес элемента выполняется программным способом с помощью операций, манипулирующих с адресным регистром:

LOOP: MOVB ptr, @reg ;Поиск байта

INC reg ;data в строке

СМРВ ptr, #data ;сравнение байтов, начиная с

JNZ LOOP ;адреса (reg)

Очень часто данные располагаются в памяти последовательно (очереди, последовательности, файлы и т. д.). Для повышения эффективности работы со структурами такого типа используются автоинкрементный и автодекрементный способы адресации (ptr = (reg)+, ptr = –(reg)).

При автоинкрементном способе (рис. 1.21, а) обеспечивается вычисление исполнительного адреса, как и при косвенном, но с последующим автоматическим увеличением содержимого адресного регистра на длину операнда, что позволяет подготовиться к выборке следующего элемента данных:

MOVB dst, (reg)+ ;dst(reg), regreg + 1

При автодекрементной адресации (рис. 1.21, б) содержимое адресного регистра сначала уменьшается на длину операнда, а затем используется как исполнительный адрес:

MOVB dst, –(reg) ;regreg – 1, dst(reg)

Эти способы адресации позволяют исключать из программы настройку адреса, что существенно ускоряет процедуры просмотра потоковых структур.

Комбинирование автоинкрементных способов адресации позволяет организовать стеки с адресным регистром в качестве SP. Для загрузки данных в стек применяется автодекрементная адресация:

MOV –(reg), src

для выталкивания—автоинкрементная:

MOV dst, (reg)+

Доступ к вершине стека TOS осуществляется с помощью косвенной регистровой адресации:

MOV dst, @reg

Указатель стека reg всегда указывает на вершину стека, который заполняется в сторону уменьшения адресов. Это соответствует принятой ранее стандартной организации стека.

Неявно заданный способ адресации с модификацией реализуется в операциях со стеком:

PUSH src ;–(SP)src

POP dst ;dst(SP)+

CALL src ;–(SP)PCsrc

RET ;PC(SP)+

CALL reg, src ;–(SP)regPCsrc

RET reg ;PCreg(SP)+

B этом случае его называют стековым.

Процедура выборки программной последовательности также использует неявно заданную автоинкрементную адресацию по PC. Действительно, после считывания очередного элемента объектного кода указатель PC автоматически увеличивает свое содержимое на 1 или 2, в зависимости от длины программного элемента.

Непосредственную адресацию данных можно интерпретировать как автоинкрементную по PC. Например, программная последовательность

MOVB reg, (PC)+

DB data

эквивалентна команде с литералом

MOVB reg, #data

Здесь DB (Define Byte) не имя какой-либо машинной команды, а символическое обозначение директивы размещения последовательности байтов данных. Эти данные должны быть указаны следом за директивой и при необходимости отделяются друг от друга запятыми. В нашем случае последовательность содержит один байт данных. После приема команды

MOVB reg, (PC)+

указатель PC адресует байт data. После выполнения операции и следующей за ней автоматической модификации он будет указывать на начало новой команды.

Возможны два варианта определения автоинкрементной адресации (ptr = +(reg) и ptr = (reg)–), которые называют преавтоинкрементной и поставтодекрементной соответственно (рис. 1.21, в, г). Их совместное использование также обеспечивает организацию стека с указателем, адресующим TOS. Однако растет такой стек в сторону увеличения адресов.

В общем случае каждой паре автомодификации соответствуют по два типа стека. Эти стеки характеризуются следующими операциями доступа:

Операция PUSH src POP src

Стандартный стек MOV –(reg), src MOV dst, (reg)+

Стек типа 1 MOV (reg)+, src MOV dst, –(reg)

Стек типа 2 MOV +(reg), src MOV dst, (reg)–

Стек типа 3 MOV (reg)–, src MOV dst, +(reg)

В отличие от стандартного стека и стека типа 2 указатель reg в двух новых стеках адресует первую свободную ячейку над TOS. При этом стек типа 1 растет в сторону уменьшения адреса, а стек типа 3 в сторону увеличения. Согласованность операций доступа стандартного стека с операцией выборки объектного кода, а также прямая адресуемость TOS по содержимому SP определили его широкое использование в качестве типового стека МС.

Комбинирование адресации с автомодификацией и косвенной позволяет построить более универсальные способы доступа по сравнению с рассмотренными выше—косвенную автоинкрементную и автодекрементную адресацию (ptr = @(reg)+, ptr = @–(reg)). Четыре способа представлены на рис. 1.22. В их основу положен стандартный вариант автомодификации. Достаточно широкое распространение находит лишь первая пара (рис. 1.22, а, б), которая характеризуется однократным обращением к памяти данных. Вторая пара способов (рис. 1.22, в, г) требует до трех обращений к памяти, что существенно снижает их практическую ценность.

| Рис. 1.22. Способы комбинированной адресации: а—косвенная автоинкрементная; б—косвенная автодекрементная; в—прекосвенная автоинкрементная; г—прекосвенная автодекрементная | Рис. 1.23. Двухкомпонентные способы адресации: а—по базе ; б—индексная; в—относительная; г—двухкомпонентная косвенная регистровая |

Многокомпонентные способы адресации. При многокомпонентных способах адресации для построения исполнительного адреса используется несколько источников адресной информации, содержимое которых суммируется. Каждое слагаемое—это прямо или косвенно заданный компонент (возможен вариант компонента с автомодификацией). В двухкомпонентном случае практический интерес представляют следующие комбинации способов адресации: прямая + косвенная регистровая, косвенная регистровая + косвенная регистровая, прямая + автоинкрементная. Наибольшее распространение нашла первая комбинация.

В случае адресации по базе (ptr = (breg).index) исполнительный адрес формируется по схеме, приведенной на рис. 1.23, а, когда

ea = (breg) + index, MOD 2|ea|

Адресация по базе необходима для организации доступа к конкретным полям блока данных, адрес которого может быть неизвестен во время создания программы. Например, блок данных динамически создается в разных областях памяти или его размещение определяется в момент загрузки. В такой ситуации переменный адрес начала блока (базу) удобно располагать в регистре breg (базовом), а известный относительный адрес элемента (индекс) хранить непосредственно в команде. Допустим и вариант короткого индекса, уменьшающий длину объектного кода: |index| ≤ |ea|. При этом индекс может восприниматься как целое либо без знака (offset), либо со знаком (disp). Во втором случае появляется возможность адресоваться относительно базы в обе стороны. При необходимости для выполнения операции суммирования (breg) + index производится расширение знака короткоразмерного индекса до полного размера.

Адресация по базе используется: для передачи данных в блоке параметров (базовый регистр служит указателем блока); для передачи данных через стек (базовый регистр выполняет роль указателя кадра FP); для передачи данных и организации переходов в программах, не зависящих от места их размещения в памяти (базовый регистр указывает на начало программы); для доступа к конкретному полю блока в связном списке (базовый регистр применяется для адресации элементов списка) или к одному и тому же полю динамически созданной записи (базовый регистр указывает на начало записи).

Схема вычисления исполнительного адреса при индексной адресации (ptr = base(ireg)) показана на рис. 1.23, б и похожа на схему вычисления по базе:

ea = base + (ireg), MOD 2|ea|

Однако методика ее использования иная.

Индексная адресация применяется при последовательном доступе к элементам блока (массив, таблица, очередь), адрес размещения которого (база) известен. При этом номер элемента блока (индекс) является переменной, вычисляемой во время исполнения программы. Поэтому индекс удобно хранить в регистре ireg (индексном), а базу—в объектном коде команды. Отличие индексной адресации от адресации по базе состоит в том, что в объектном коде должен храниться полный адрес памяти |base| = |еа|, тогда как в качестве индексного регистра может использоваться регистр меньшей длины. При |ireg| = |ea| индексная адресация включает адресацию по базе. По этой причине последнюю часто называют индексной. В случае нулевой базы индексная адресация с полноразмерным индексом совпадает с косвенной, тогда регистр косвенной адресации называется индексным.

Разновидностью адресации по базе является относительная (PC).disp, при которой в качестве базового регистра breg используется PC (рис. 1.23, в), как правило, указываемый неявно (ptr = .disp).

Отметим, что во всех случаях двухкомпонентной адресации индекс может быть целым числом со знаком. Это дает возможность адресоваться не только в сторону больших, но и меньших адресов. При относительной адресации смещение всегда целое число со знаком. Существует вариант короткого смещения, обеспечивающий более компактное кодирование команд.

Относительная адресация применяется для создания позиционно-независимых программ, т. е. программ, исполнение которых не зависит от их размещения в памяти. Примерами команд с относительной адресацией являются

MOV reg, .disp ;reg(PC + disp)

JMP .disp ;PCPC + disp

Каждому из вышеприведенных двухкомпонентных способов адресации соответствует вариант косвенной адресации:

@(breg).index Косвенный по базе

@base(ireg) Косвенный индексный

@.disp Косвенный относительный

Здесь исполнительный адрес формируется по схеме

еа = (base + index)

Косвенные варианты требуют двойного обращения к памяти МС, поэтому они не получили широкого распространения.

Двухкомпонентная косвенная регистровая адресация (ptr = (breg) (ireg)) может быть получена, когда обе компоненты—и база, и индекс—заданы косвенно (рис. 1.23, г). Способ симметричен по отношению к своим компонентам только при полноразмерном индексном регистре.

Трехкомпонентные способы адресации. Дальнейшего увеличения числа способов адресации можно достичь при переходе к трехкомпонентным схемам типа прямая + косвенная регистровая. Среди них

(breg).index (ireg) Базированная с индексированием

basе(ireg1) (ireg2) С двойным индексированием

Адресация такого типа используется в МП К1810ВМ86, в котором

index = disp8/disp16

base = offset16

ГЛАВА 2.

Дата добавления: 2019-02-07; просмотров: 3590;