Центральный процессор на базе БИС серии КР580

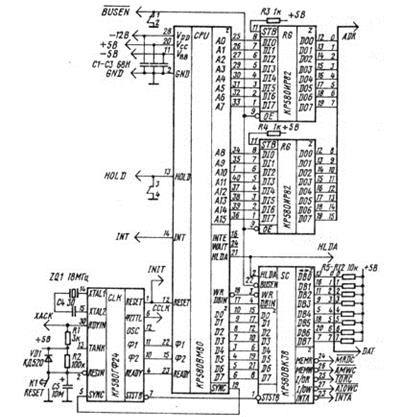

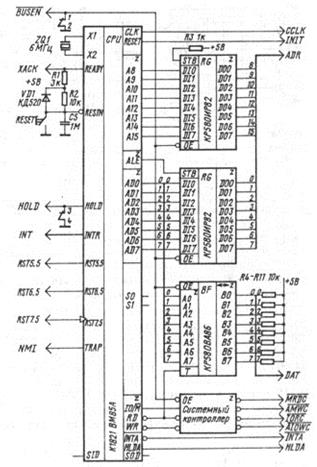

Схема ЦП на базе БИС серии КР580 приведена на рис. 2.17 [23, 53]. В простейшем случае она может содержать только три кристалла: МП КР580ВМ80, генератор тактовых импульсов КР580ГФ24 и системный контроллер КР580ВК28/ВК38, применение которых гарантирует компактность ЦП при полном сохранении всех функциональных возможностей МП.

Рис. 2.17. Схема центрального процессора на базе серии КР580

Чтобы выполнить функцию начальной установки МП, необходимо ко входу RESIN ГТИ подключать RC-цепочку. Наличие гистерезиса на входе RES1N (см. рис. 2.9, а) гарантирует быстрое переключение схемы в момент достижения порога переключения. Постоянная времени RC-цепочки рассчитывается из требований, накладываемых на длительность сигнала RESET.

Период следования синхросигналов Ф1, Ф2 микропроцессора КР580ВМ80 определяется кварцевым резонатором ZQ1. При выборе и установке кварцевого резонатора следует обеспечить минимальное сопротивление внешней цепи генератора XTAL2—XTAL1. Со стороны кварцевого резонатора генератор представляет индуктивный элемент, приводящий к снижению рабочей частоты. Для компенсации данного эффекта рекомендуется последовательно с кварцевым резонатором со стороны вывода XTAL2 включить конденсатор небольшой емкости. Для кварцевого резонатора частотой 18 МГц емкость 15—30 пФ. При повышении частоты может потребоваться уменьшение емкости конденсатора.

Кроме синхросигналов Ф1, Ф2 генератор формирует также системный сигнал CCLK (ток нагрузки I0L ≤ 15 мА) и сигнал системного сброса INIT (I0L ≤ 15 мА). Сигнал INIT предназначен для начальной установки системы в исходное состояние. Он реализуется при наличии сигнала, формируемого RC-цепочкой на входе  генератора. Применяемые в схеме на рис. 2.17 элементы обеспечивают длительность сигнала сброса 0,35 с.

генератора. Применяемые в схеме на рис. 2.17 элементы обеспечивают длительность сигнала сброса 0,35 с.

Сигнал подтверждения ХАСК используется при работе с медленными модулями памяти и ВВ. Он может быть задействован также для организации ожидания ЦП некоторого внешнего события. Микропроцессор КР580ВМ80 будет переведен в состояние ожидания WAIT, если сигнал ХАСК окажется неактивным в момент первой его проверки (начало второй трети такта Т2). В зависимости от размера и характеристик системы сигнал подтверждения может быть организован одним из двух способов.

В больших системах линия подтверждения ХАСК обычно выполняется с низким уровнем активности, что обеспечивает асинхронный способ доступа к модулям памяти и ВВ. Для этого перед входом RDYIN генератора следует поставить дополнительный инвертор. После того как выбранное устройство получит строб чтения или записи, оно генерирует сигнал подтверждения, формируемый на линии ХАСК по схеме с открытым коллектором. Для максимальной производительности системы ее модули должны возвращать сигнал подтверждения до его первой проверки.

В малых системах с быстродействующими устройствами рекомендуется использовать линию ХАСК с высоким уровнем активности. Процессор работает в синхронном режиме без тактов ожидания с максимальной для него скоростью. Следовательно, в устройствах, успевающих выполнить операцию в синхронном режиме, можно опустить логику подтверждения обмена, тем самым упростив их.

В схеме на рис. 2.17 использован системный контроллер типа КР580ВК38. От контроллера КР580ВК28 он отличается тем, что формирует упрежденные стробы  и

и  (см. рис. 2.12), рассчитанные на периферийные приборы второго поколения. В контроллере КР580ВК28 эти стробы представляют собой задержанный на 4—45 нс строб WR микропроцессора КР580ВМ80, который генерируется за время такта Т3, т. е. уже после первой проверки сигнала подтверждения ХАСК.

(см. рис. 2.12), рассчитанные на периферийные приборы второго поколения. В контроллере КР580ВК28 эти стробы представляют собой задержанный на 4—45 нс строб WR микропроцессора КР580ВМ80, который генерируется за время такта Т3, т. е. уже после первой проверки сигнала подтверждения ХАСК.

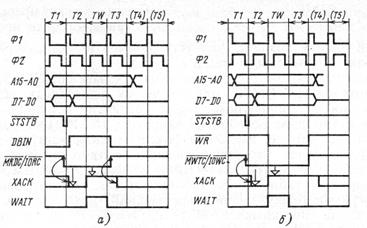

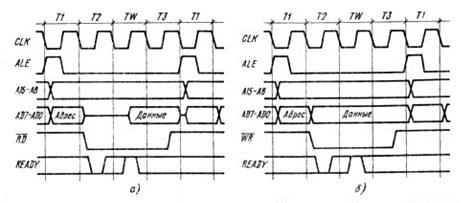

Как показано на рис. 2.12, все командные стробы КР580ВК38 связаны со стробом STSTB и задержаны относительно его начала на 20—60 нс. Так как STSTB опережает на Т/3 фазу Ф2 такта Т2, то до момента первой проверки сигнала ХАСК еще остается 4Т/9—60 нс. При Т = 400 нс это время примерно равно 120 нс, что вполне достаточно для сброса сигнала ХАСК. Временная диаграмма работы ЦП приведена на рис. 2.18.

Рис. 2.18. Временные диаграммы циклов чтения (а) и записи (б) центрального процессора

Таким образом, применение контроллера КР580ВК28 возможно либо в системах с синхронным обменом, либо в системах асинхронного доступа с инверсной линией ХАСК. В МС, допускающих оба протокола обмена, рекомендуется использовать микросхему КР580ВК38. Во всех случаях нагрузочная способность командных линий  ,

,  ,

,  и

и  следующая: I0L ≤ 10 мА, CL ≤ 100 пФ. Допустимый ток I0L и емкость CL линии

следующая: I0L ≤ 10 мА, CL ≤ 100 пФ. Допустимый ток I0L и емкость CL линии  равны 5 мА и 100 пФ.

равны 5 мА и 100 пФ.

Системный контроллер обеспечивает также двунаправленную буферизацию шины данных МП без инверсии, доводя I0L до 10 мА и CL до 100 пФ. Дополнительная задержка в шине данных около 30 нс.

Удобно, но не обязательно системную шину данных DAT7—DAT0 подключать к источнику питания +5 В через резисторы 10 кОм. Это практически не скажется на нагрузочной способности шины. С другой стороны, чтение команды из несуществующей области памяти приведет к выполнению команды RST 7, это может быть использовано в отладочных и диагностических целях.

Адресная шина МП ВМ80 обеспечивает ток нагрузки I0L = 1,8 мА и емкость нагрузки CL до 100 пФ. Этой нагрузочной способности достаточно для построения одноплатного МК закрытого типа. В открытых для расширения МС требуется дополнительная буферизация адресной шины, которая может быть выполнена с помощью двух буферных регистров КР580ИР82 без инверсии. Буферизация адреса позволяет увеличить максимальные значения I0L до 32 мА и CL до 300 пФ. Вместе с этим в шине появляется дополнительная задержка 35 нс.

Возможна реализация адресного буфера на других микросхемах, например КР580ИР83, КР580ВА86/ВА87, К589ИР12, К589АП16/АП26 и т. д. Они имеют другие нагрузочные и временные характеристики и могут приводить к инверсии адреса.

Три сигнала ЦП—запрос на захват шины HOLD, подтверждение захвата HLDA (I0L = 1,8 мА) и разрешение шины BUSEN—служат для организации доступа к магистрали со стороны других активных модулей системы. Частным случаем такого модуля является устройство с прямым доступом к памяти, управляемое БИС КР580ВТ57. Для запуска ЦП в системах, которые не имеют других активных модулей кроме ЦП, необходимо установить перемычки 1-2, 3-4.

Организация ВМ85А

Архитектурные отличия от ВМ80. Однокристальный МП К1821ВМ85А (ВМ85А) является усовершенствованным 8-разрядным МП, имеющим полную архитектурную совместимость со своим предшественником КР580ВМ80 [65].

Разработка нового МП была направлена на повышение производительности, скоростных характеристик и уменьшение числа БИС, необходимых для построения законченной МС. В результате удалось на одном кристалле кремния разместить устройство, функционально эквивалентное трем БИС: микропроцессору КР580ВМ80, генератору тактовых импульсов КР580ГФ24 и системному контроллеру КР580ВК28/ВК38.

С точки зрения программиста архитектура ВМ85А практически тождественна архитектуре ВМ80. В нем используется тот же самый набор программно-доступных регистров аккумуляторного типа (см. рис. 2.2). Сохранена логическая организация памяти и пространства ВВ. Система команд ВМ85А включает весь набор команд ВМ80 в их старой кодировке, что гарантирует полную совместимость с ПО микропроцессора ВМ80 на уровне объектного кода. Вместе с этим в состав системы команд ВМ85А введены две новые, что связано с расширением средств обработки прерываний и последовательным ВВ:

RIM ;Чтение маски прерываний

SIM ;Установка маски прерываний

Полный набор команд, включая новые, их характеристики и кодировка приведены в табл. 2.1—2.5.

Методология построения системы прерываний ВМ85А подчинена архитектуре ВМ80, однако число возможных источников прерываний на аппаратном уровне увеличено с одного до пяти. Наряду с типовым векторным запросом INTR (INT для ВМ80) введены еще четыре, имеющие фиксированные векторы прерываний. Это означает, что при появлении соответствующего запроса управление передается на ячейку с фиксированным адресом, приведенным в табл. 2.7. Из таблицы видно, что стартовые адреса подпрограмм обслуживания прерываний находятся в области точек входа по команде RST n, n = 0—7, но расположены посередине между ними. Это разъясняет ряд наименований, принятых для запросов RST n.5, n = 5—7.

Таблица 2.7

| Имя | Приоритет | Стартовый адрес | Вид сигнала |

| TRAP RST 7.5 RST 6.5 RST 5.5 INTR | 24H 3CH 34H 2CH Вводится при подтверждении прерывания | Переход из 0 в 1, затем 1 Переход из 0 в 1 |

Все запросы, за исключением TRAP, могут быть запрещены или разрешены одновременно с помощью команд EI и DI, управляющих общим флагом разрешения прерываний IEN. Существует также возможность раздельного маскирования запросов типа RST независимо друг от друга, которое выполняется с помощью новой команды SIM. По команде SIM обеспечивается установка нового состояния маски в соответствии с содержимым аккумулятора. При выполнении этой команды содержимое аккумулятора интерпретируется следующим образом:

А0 М5.5 Маска RST 5.5

A1 M6.5 Маска RST 6.5

А2 М7.5 Маска RST 7.5

A3 MSEN Разрешение установки маски

А4 R7.5 Сброс триггера приема запроса RST 7.5

А5 —Не используется

А6 SDEN Разрешение вывода данных

А7 SOD Последовательные данные для вывода через SOD

Установленная маска запрещает соответствующее прерывание. Смена маски в соответствии с А0—А2 выполняется только при разрешении ее установки: MSEN = 1. В противном случае функция установки маски подавляется.

Текущее состояние масок прерываний может быть прочитано по команде RIM. Команда пересылает текущее состояние масок в аккумулятор в соответствии со следующим распределением:

А0 М5.5 Маска RST 5.5

A1 M6.5 Маска RST 6.5

А2 М7.5 Маска RST 7.5

A3 IEN Флаг разрешения прерывания

А4 D5.5 Флаг запроса RST 5.5

А5 D6.5 Флаг запроса RST 6.5

А6 D7.5 Флаг запроса RST 7.5

А7 SID Последовательные данные ввода через SID

При включении источника питания или пуске МП все индивидуальные маски устанавливаются, а флаг разрешения прерывания IEN сбрасывается, что приводит к запрету прерываний. Прием какого-либо запроса на прерывание тоже вызывает общее запрещение всех маскируемых прерываний, но при сохранении состояния индивидуальных масок. Кроме этого запрос TRAP сохраняет и состояние флага общего разрешения, которое может быть прочитано только первой командой RIM. Вторая команда дает результат текущего состояния маски, показывающего общий запрет прерываний.

Запросы на прерывания строго упорядочены, как это показано в табл. 2.7. Высшим приоритетом обладает немаскируемый запрос TRAP, низший присвоен векторному прерыванию INTR. Установленная приоритетная схема разрешает конфликт при одновременном появлении нескольких запросов и не учитывает текущего приоритета программы. Так, прерывание с более низким приоритетом, разрешенное во время исполнения процедуры обслуживания запроса с более высоким приоритетом, может остановить последнюю, не учитывая соотношения приоритетов.

Еще одно важное отличие архитектуры ВМ85А от ВМ80 состоит в поддержке последовательной линии ВВ. В ВМ85А имеется возможность программного доступа к изолированному однобитовому пространству ВВ, реализуемого с помощью команд RIM и SIM. При исполнении данных команд наряду с чтением или установкой регистра масок производится ввод данных с линии в старший разряд аккумулятора или их вывод в обратном направлении. Вывод данных осуществляется только при установке флага разрешения вывода данных SDEN. В противном случае функция вывода подавляется. Управление функциями вывода и установки маски прерывания независимыми флажками SDEN и MSEN соответственно позволяет выполнить ВВ, не затрагивая систему прерываний.

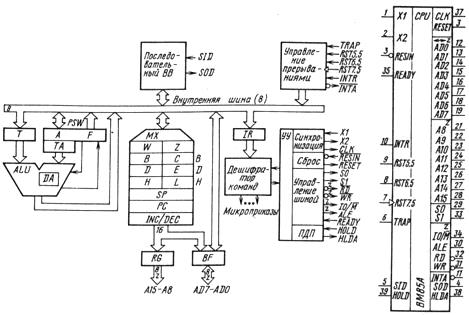

Структурная схема ВМ85А. Если на уровне архитектуры МП ВМ85А аналогичен ВМ80, за исключением отмеченных выше отличий, то на физическом уровне они значительно отличаются друг от друга [43, 56].

Схема МП ВМ85А приведена на рис. 2.19, а его условное графическое изображение—на рис. 2.20.

Рис. 2.20. Условное графическое обозначение микропроцессора ВМ85А

Рис. 2.19. Схема микропроцессора ВМ85А

По сравнению со схемой МП ВМ80 (см. рис. 2.4) в схеме ВМ85А используется совмещенная шина адреса/данных AD7—AD0, по которой передаются младшая часть адресной информации и 8-разрядные данные. Старшая часть адреса фиксируется в регистре адреса и выводится на шину А15—А8. Существенно видоизменен набор линий шины управления, которые обеспечивают прямое подключение кварцевого резонатора, а также управление периферийными БИС памяти и ВВ. Расширен и модифицирован состав физических линий для поддержки системы прерываний. Введен блок последовательного ВВ. Приведем физический интерфейс ВМ85А.

AD7—AD0 Двунаправленная трехстабильная мультиплексированная шина младшей части адреса и

данных

А15—А8 Трехстабильная шина вывода старшей части адреса

XI, Х2 Вход и выход усилителя для подключения внешнего кварцевого резонатора или

RC-цепочки. Вход X1 может быть использован для приема внешних тактовых импульсов

CLK Выход тактовых импульсов

RESIN Вход для приема сигнала сброса МП в начальное состояние. По сигналу

PC принимает нулевое значение, сбрасываются триггеры разрешения прерывания

и состояния HLDA

RESET Выходной сигнал системного сброса, синхронизированный тактовыми импульсами CLK

S0, S1 Состояние МП:

S1 S0 Назначение

0 0 HALT (останов)

0 1 WRITE (запись)

1 0 READ (чтение)

1 1 FETCH (выборка команды)

Линия SI может быть использована в качестве упреждающего сигнала R/W

,

,  Трехстабильные линии для вывода стробов чтения и записи.

Трехстабильные линии для вывода стробов чтения и записи.

Данные действительны в конце строба

Линия выбора системы памяти или устройств ВВ

Линия выбора системы памяти или устройств ВВ

Имеет три состояния

ALE Строб разрешения фиксации адреса. Адрес действителен на срезе строба. Линия

имеет три состояния. Может быть использован для стробирования информации о

состоянии

READY Линия для приема подтверждения обмена во время стробов  и

и

INTR Линия запроса векторного прерывания, который вызывает генерацию строба INTA.

Предусмотрены программные средства запрещения (разрешения) приема сигнала. При

сбросе прием запроса запрещен

Выходная линия для генерации строба подтверждения векторного прерывания после

Выходная линия для генерации строба подтверждения векторного прерывания после

завершения текущего командного цикла. Используется аналогично стробу  для

для

приема вектора прерывания

RST 5.5, Входы для принятия запросов прерывания типа RST n,

RST 6.5, n = 5.5, 6.5 и 7.5 соответственно. Вход RST 7.5 имеет высший

RST 7.5 приоритет в группе. Приоритет группы выше приоритета INTR. Прерывания могут быть

замаскированы независимо друг от друга

TRAP Вход немаскируемого прерывания типа RST n, n = 4.5, высшего приоритета

SID, SOD Вход и выход последовательной передачи данных. Входные данные загружаются в

старший разряд аккумулятора А7 по команде RIM, вывод данных осуществляется из А7

по команде SIM

HOLD Линия запроса захвата шины внешним модулем

HLDA Линия подтверждения захвата шины, активизируется в ответ на сигнал HOLD в конце

текущего машинного цикла. При этом линии адреса/данных, а также  ,

,  ,

,

и ALE переводятся в третье состояние

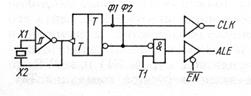

Работа МП синхронизируется внешним кварцевым резонатором или RC-цепочкой, подключаемой непосредственно к выводам X1 и Х2. Схема синхронизации представлена на рис. 2.21. Из схемы видно, что фронт сигнала на входе X1 переключает счетный триггер, который формирует две последовательности несовпадающих импульсов Ф1 и Ф2, используемые для тактирования внутренних схем МП. Внешний сигнал синхронизации CLK совпадает по фазе с импульсами Ф2. Сигнал ALE представляет собой один импульс Ф1, выделяемый в такте Т1 каждого машинного цикла. Он является синхросигналом начала машинного цикла.

Рис. 2.21. Схема синхронизации микропроцессора ВМ85А

Основная тактовая частота сигнала CLK микропроцессоров ВМ85А и 8085А равна 3 МГц, что обеспечивает более высокую производительность, чем у стандартного МП ВМ80 с тактовой частотой 2,5 МГц. Существуют также БИС, рассчитанные на работу с частотой 5 МГц, например 8085А-2, что дополнительно повышает производительность МП данного типа.

В каждом машинном цикле МП обращается к магистрали для ввода или вывода одного байта информации, согласно временным диаграммам, изображенным на рис. 2.22. Работа канала синхронизируется стробами ALE, RD, WR и соответствует типовому протоколу на двухшинную магистраль (ср. с рис. 1.10). Каждый машинный цикл или цикл обращения к внешнему каналу содержит от 3 до 5 периодов Т1—Т5 сигнала CLK основной тактовой частоты. К этим тактам может быть добавлено произвольное число тактов ожидания готовности канала TW, которые включаются между Т2 и Т3. Непосредственно для ВВ информации отводятся лишь первые три такта совместно с тактами ожидания готовности. В такте Т1 производится вывод адресной информации, а в тактах Т2 и Т3—обмен данными.

Рис. 2.22. Временные диаграммы циклов чтения (а) и записи (б) микропроцессора ВМ85А

При необходимости добавляются еще один или два такта для реализации операций внутри МП. В это время канал не используется.

Линия READY служит для организации обмена с медленными устройствами. При READY = 1 реализуется синхронный режим работы, характеризующийся максимальной скоростью обмена без тактов ожидания, которую обеспечивает МП. В этом случае длительность стробов RD, WR минимальна и составляет 1,5Т—80нс, где Т—период CLK. Стробы задержаны на 50 нс относительно начала Т2.

Проверка активности сигнала READY выполняется в середине Т2 и всех следующих за ним тактов TW. Для организации асинхронного доступа этот сигнал должен быть установлен в 0 за 110 нс и удерживаться в таком состоянии вплоть до момента его первой проверки. Эти же временные ограничения характерны и для процесса установки сигнала готовности. Манипуляция сигналом READY дает возможность удлинить строб RD или WR до (1,5 + N)T—80 нс, где N—целое число периодов ожидания TW, обеспечив надежный обмен с медленной памятью или портами ВВ.

Особенностью процедур ВВ служит тот факт, что данные действительны только на срезе стробов RD и WR, т. е. протокол МП ВМ85А предполагает использование периферийных БИС второго поколения. Времена предустановки и удержания данных при выводе принимают значения tDW ≥ 420 нс, tWD ≥ 80 нс соответственно. Аналогично для цикла чтения tDR ≥ 120нс, tRDH ≥ 0нс.

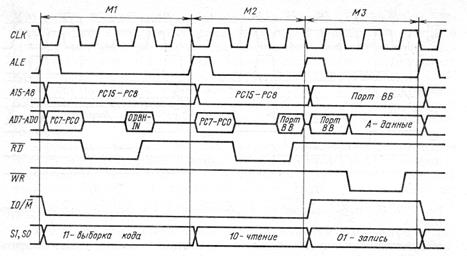

Каждый командный цикл включает от одного до пяти машинных циклов M1—М5. Синхронизацию по командным циклам можно получить, выделяя с помощью сигналов состояния S1 и S0 все циклы M1 (FETCH). Этому типу цикла соответствует состояние S1 = S0 = 1. На рис. 2.23 приведен пример командного цикла IN port при работе без тактов ожидания. Из временных диаграмм видно, что команда выполняется за три цикла обращения к каналу: M1—выборка кода операции, М2—чтение из памяти второго байта команды и МЗ—выдача содержимого аккумулятора в порт ВВ.

Рис. 2.23. Временные диаграммы командного цикла IN port

Следует отметить, что, подобно ВМ80, микропроцессор ВМ85А выводит 8-разрядный адрес порта как на старшую, так и на младшую половину 16-разрядной шины адреса. Модули ВВ могут быть ориентированы на использование только старшей половины шины А15—А8 и, следовательно, отпадет необходимость во внешнем адресном регистре для приема адреса по сигналу ALE.

Длительность командных циклов ВМ85А в периодах основной тактовой частоты отличается от длительности исполнения соответствующих команд в МП ВМ80. Эти отличия можно проследить по табл. 2.1—2.5, где для каждой команды указано число тактов, необходимых для ее исполнения как в одном, так и в другом случае. Одни команды требуют меньшего, другие—большего числа тактов, что объясняется изменениями, внесенными в физическую организацию МП ВМ85А.

Как уже отмечалось, МП ВМ85А имеет пять линий для приема запросов на прерывание: INTR, RST 5.5, RST 6.5, RST 7.5 и TRAP. Линия INTR по своим функциям аналогична линии INT микропроцессора ВМ80. В ответ на запрос INTR генерируется один или три машинных цикла INTA с временными диаграммами, эквивалентными циклу RD без тактов ожидания. Внешняя аппаратура отвечает на циклы INTA генерацией команды либо типа RST n, n = 0—7 (случай одного цикла INTA), либо типа CALL addr (случай трех циклов INTA), обеспечивая передачу управления на подпрограмму обслуживания прерывания.

Согласно методике приема запросов все входы можно разделить на три группы. К первой относятся входы статического типа RST 5.5, RST 6.5, а также INTR. Запрос на прерывание по этим входам фиксируется каждый раз, когда на них при сброшенной маске обнаружено напряжение высокого уровня. Время предустановки сигнала до начала Т1 цикла M1 tINS ≥ 360 нс и время его удержания tINH ≥ 0 нс. Для предотвращения повторной фиксации одного и того же запроса сигнал прерывания по статическому входу должен быть снят, прежде чем будет сброшена соответствующая маска.

Ко второй группе относится вход RST 7.5, который является входом динамического типа и фиксирует запрос на прерывание при каждом переходе сигнала из 0 в 1, даже при установленной маске и запрещенных прерываниях. Запрос сохраняется до тех пор, пока он не будет обслужен или не сброшен командой SIM. Сброс триггера осуществляется при установленном четвертом разряде аккумулятора R7.5. Сброс запроса реализуется также при перезапуске МП.

Третью группу образует вход TRAP, который не является чисто статическим или динамическим. Так, если для подтверждения прерывания на нем должно устанавливаться напряжение высокого уровня, то для фиксации нового запроса он должен генерировать напряжение низкого уровня, а затем вновь вернуться в исходное состояние (вход комбинированного типа). Это позволяет избежать ложных запусков из-за помех на линии по высокоприоритетному немаскируемому входу TRAP, используемому для фиксации важнейших для МС событий. Времена фиксации запроса TRAP эквивалентны временам предустановки и удержания сигналов по статическим входам.

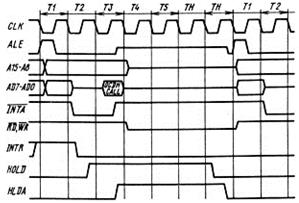

Сигнал запроса на захват шины проверяется в начале каждого такта Т3. Времена предустановки и удержания сигнала принимают значения tHDS ≥ 170 нс, tHDH ≥ 0 нс соответственно. При фиксации запроса шина освобождается в такте, непосредственно следующем за Т3. Для этого за 110 нс до окончания Т3 устанавливается сигнал подтверждения захвата HLDA, а затем линии А15—А8; AD7—ADO,  ,

,  , ALE,

, ALE,  переводятся в третье состояние, тем самым освобождая магистраль для управления со стороны внешних модулей. При необходимости МП завершает такты Т4, Т5 и переходит в состояние HOLD, которое длится до снятия сигнала запроса. Временные диаграммы цикла захвата шины и подтверждения прерываний приведены на рис. 2.24.

переводятся в третье состояние, тем самым освобождая магистраль для управления со стороны внешних модулей. При необходимости МП завершает такты Т4, Т5 и переходит в состояние HOLD, которое длится до снятия сигнала запроса. Временные диаграммы цикла захвата шины и подтверждения прерываний приведены на рис. 2.24.

Рис. 2.24. Временные диаграммы цикла подтверждения прерывания и захвата шины

Центральный процессор на базе ВМ85А. В отличие от ВМ80 микропроцессор ВМ85А представляет собой практически законченный однокристальный ЦП. Для его запуска необходим только кварцевый резонатор, подключенный к входам X1, Х2, и схема сброса на входе RESIN. Схема подключения кварцевого резонатора приведена на рис. 2.25, а. Конденсаторы емкостью 20 пФ на входах X1 и Х2 могут потребоваться при запуске кварцевого резонатора с частотой 4 МГц и выше. Возможны другие варианты синхронизации МП. Схема на рис. 2.25, б обеспечивает частоту колебаний

,

,

где СIN—входная емкость между X1 и Х2.

Рис. 2.25. Схемы тактирования микропроцессора ВМ85А:

а—внутренний генератор с кварцевым резонатором; б—внутренний генератор с настроенным LC-контуром;

в—внутренний генератор с RC-цепочкой; г—внешний генератор 1—6 МГц; д—внешний генератор 6—10 МГц.

Если установка точной тактовой частоты не обязательна, то применяется схема, показанная на рис. 2.25, в, которая обеспечивает частоту колебаний около 3 МГц. В схеме на рис. 2.25, г,д синхронизация МП осуществляется от внешнего генератора.

В качестве схемы сброса рекомендуется цепочка, эквивалентная примененной в схеме на рис. 2.17. .Вход READY может быть использован для организации асинхронного доступа к системной магистрали. Как и в ЦП на базе ВМ80, в ЦП на базе ВМ85А возможны два варианта построения системной линии подтверждения обмена, отличающиеся друг от друга уровнем активности. Выходы CLK и RESET применяются в качестве системных линий CCLK и INIT передачи тактовых импульсов и сигнала начальной установки соответственно.

Возможности выходов схемы ВМ85А по току составляют IоL = 2 мА Iон = 400 мкА. Зная требования по постоянному току, предъявляемые к обычным логическим элементам по входу:

Технология IIH, мкA IIL, мА

ТТЛ 40 1,6

ТТЛШ 40 2

n-МОП 10 0,01

ТТЛШ маломощная 20 0,4

можно оценить нагрузочную способность МП ВМ85А.

Для увеличения числа нагрузок по постоянному току сигнал должен быть буферизирован.

Другой фактор, который необходимо учитывать—это емкостная нагрузка СL. Временные соотношения для ВМ85А гарантируются при cl ≤150 пФ. При превышении этой нагрузки временные соотношения ухудшаются. Отклонение емкостной нагрузки от 150 пФ в сторону уменьшения или увеличения влечет за собой изменение временных соотношений приблизительно на 0,2 нс/пФ.

Построенный таким образом ЦП оказывается ориентированным на двухшинную магистраль, шина управления которой состоит из следующих основных сигналов: ALE,  ,

,  ,

,  . Попытка реализовать трехшинную магистраль, эквивалентную магистрали на рис. 2.17, привела к схеме, представленной на рис. 2.26. Буферные регистры КР580ИР82 и шинный формирователь КР580ВА86 служат не только для раздела совмещенной шины AD, но и для повышения нагрузочной способности системной магистрали до IOL = 32 мА и Cl = 300 пФ. Возможно использование других схем подобного типа.

. Попытка реализовать трехшинную магистраль, эквивалентную магистрали на рис. 2.17, привела к схеме, представленной на рис. 2.26. Буферные регистры КР580ИР82 и шинный формирователь КР580ВА86 служат не только для раздела совмещенной шины AD, но и для повышения нагрузочной способности системной магистрали до IOL = 32 мА и Cl = 300 пФ. Возможно использование других схем подобного типа.

Рис. 2.26. Схема центрального процессора на базе микропроцессора ВМ85А

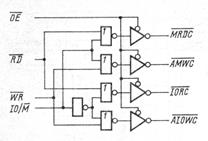

Системный контроллер представляет собой комбинационную схему (рис. 2.27). На выходах схемы предусмотрены трехстабильные буферы, управляемые сигналом  . Этот вход предназначен для перевода командных линий в высокоомное состояние при захвате магистрали внешним модулем, когда BUSEN = 0. Логика данного типа может быть реализована как на микросхемах малой степени интеграции, так и на программируемых логических матрицах (ПЛМ) [50].

. Этот вход предназначен для перевода командных линий в высокоомное состояние при захвате магистрали внешним модулем, когда BUSEN = 0. Логика данного типа может быть реализована как на микросхемах малой степени интеграции, так и на программируемых логических матрицах (ПЛМ) [50].

Рис. 2.27. Схема системного контроллера для микропроцессора ВМ85А

Сравнение схем на рис. 2.17 и 2.26 показывает, что применение МП ВМ85А выгодно за счет увеличения числа входных линий для приема запросов на прерывание, использования канала последовательного ВВ и перехода к единственному источнику питания +5 В. Не следует также забывать об улучшении скоростных свойств системного канала ЦП на базе МП ВМ85А.

Эффективность использования МП может быть повышена, если от трехшинной структуры вернуться к совмещенной магистрали AD. Однако в этом случае потребуется ряд специальных БИС памяти и ВВ, которые должны быть ориентированы на магистраль данного типа. Примером БИС такого типа служит семейство расширителей серии iMCS-85 фирмы Intel [56].

ГЛАВА 3.

ПОДСИСТЕМА ВВОДА-ВЫВОДА

ПОДСИСТЕМА ВВОДА-ВЫВОДА

Дата добавления: 2019-02-07; просмотров: 1680;