Средства параллельного ввода-вывода

Многорежимный буферный регистр К589ИР12. Параллельный ВВ—один из наиболее простых и широко распространенных способов обмена информацией с ПУ, при котором практически не требуется никакого промежуточного преобразования данных. Поэтому параллельный обмен информацией производится непосредственно портами ВВ.

Для построения портов могут быть использованы различные БИС буферных регистров и шинных формирователей. При этом принципиальные схемы практически копируют вышеприведенные схемы соответствующих портов. Из числа специально разработанных для этой цели периферийных БИС следует отметить многорежимный буферный регистр (МБР) типа К589ИР12 (ИР12) [16].

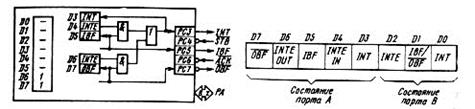

Логическая схема МБР (рис. 3.12) явилась результатом анализа и обобщения схем простейших портов ВВ. В ее состав кроме 8-разрядного регистра-защелки с трехстабильным буфером на выходе входит логика флажка состояния и средства начального сброса. Благодаря этому БИС К589ИР12 является удобным средством построения портов условного обмена. Схема выполнена по ТТЛШ-технологии и имеет 24-выводной корпус типа 239.24. Ток потребления Iсс = 130 мА.

Регистр-защелка принимает данные по входам D17—D10 (Data Input), если на его синхровход подано напряжение высокого уровня

WR = DS∙MD Ú STB∙

При возврате к напряжению низкого уровня происходит фиксация данных. Выходной буфер разрешает передачу состояния регистра без инверсии при

EN = MD Ú DS

В противном случае выходные линии D07—D00 (Data Output) имеют высокое выходное сопротивление. Нагрузочная способность выходной шины следующая: IL = 100 мА, СL = 300 пФ. Задержка от входа DI до выхода DO составляет 30 нс.

Управляющий вход MD (Mode) определяет режим работы МБР. При MD = 1 (режим выходного порта) работа выходных буферов разрешена, a WR = DS. Схема реализует выходной порт МС. При MD = 0 (режим входного порта) состояние выходного буфера определяется сигналом DS (Device Select), a WR = STB. Схема реализует входной порт МС. При этом входы DS1, DS2 используются для выбора устройства со стороны ЦП, а вход STB—для фиксации данных в режиме входного порта и подтверждения считывания в режиме выходного порта со стороны ПУ.

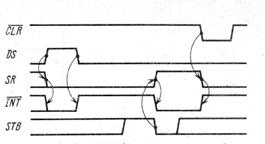

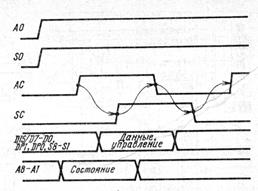

В состав микросхемы включен триггер запроса обслуживания SR (Service Request), отражающий состояние МБР. Триггер устанавливается в 1 по срезу сигнала STB, а в исходное состояние при высоком уровне внутреннего сигнала DS (рис. 3.13). Дополнительный элемент ИЛИ на выходе триггера обеспечивает переключение выхода  только по срезам сигналов STB и DS, т. е. после завершения операций записи или считывания данных, что соответствует логике установки флажка готовности. Выход запроса

только по срезам сигналов STB и DS, т. е. после завершения операций записи или считывания данных, что соответствует логике установки флажка готовности. Выход запроса  выполнен по схеме с открытым коллектором. Внутренний регистр и триггер запроса могут быть установлены в исходное состояние при подаче напряжения низкого уровня на вход

выполнен по схеме с открытым коллектором. Внутренний регистр и триггер запроса могут быть установлены в исходное состояние при подаче напряжения низкого уровня на вход  (Clear).

(Clear).

Рис. 3.13. Временные диаграммы работы многорежимного буферного регистра ИР12

Программируемый периферийный адаптер ВВ55/ВВ55А. Использование БИС с организацией ИР12 позволяет реализовывать различные параллельные интерфейсы ВВ. Проектирование интерфейса осуществляется аппаратными средствами за счет предварительной коммутации управляющих входов БИС. Оперативное изменение такого интерфейса практически невозможно, а его функции ограничены. Это обстоятельство сужает область применения МБР, она ограничивается реализацией простейших параллельных интерфейсов с постоянной по времени логикой обмена.

В усложненном интерфейсе, когда логика обмена заранее не известна или характеристики процедур обмена во время работы МС должны меняться, используются программируемые периферийные адаптеры (ППА). В их состав входят программно-доступные регистры управляющих слов CW, которые и определяют режим работы адаптера. Программный доступ к управляющему регистру со стороны ЦП дает возможность оперативно управлять работой ППА и изменять характеристики интерфейса.

К числу ППА следует отнести следующие БИС:

КР580ВВ55, 8255 Программируемый периферийный адаптер фирмы Intel (базовый вариант)

КР580ВВ55А, 8255А Программируемый периферийный адаптер фирмы Intel (улучшенный вариант)

МС6820 Программируемый периферийный адаптер фирмы Motorola (базовый вариант)

МС6821 Программируемый периферийный адаптер фирмы Motorola (улучшенный

вариант)

Программируемый периферийный адаптер КР580ВВ55 (ВВ55)—это однокристальное программируемое устройство параллельного ВВ информации произвольного формата. В состав осуществляемых им процедур входит параллельный обмен данными с квитированием или без него как в режиме программного управления,так и по прерываниям. При этом обеспечивается организация не только однонаправленного, но и двунаправленного ВВ. Определение и переопределение типа интерфейса выполняется программными методами с помощью cпeциальных процедур инициализации.

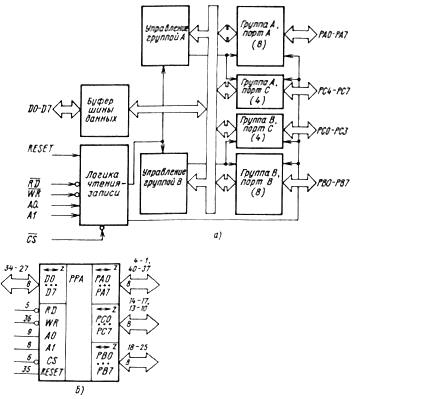

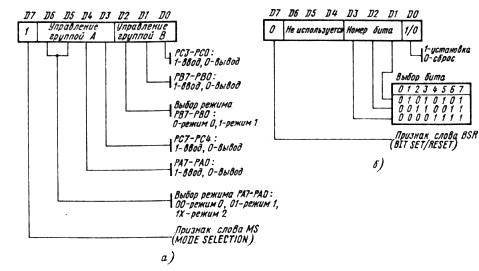

В состав ППА (рис. 3.14) входят три двунаправленных 8-разрядных порта, разбитых на две группы, два устройства управления группами портов и интерфейсная логика для согласования с системной магистралью. Организации портов, содержащих буферные регистры и шинные формирователи с тремя состояниями (рис. 3.15), значительно отличаются друг от друга. Схема управления содержит регистр управляющего слова CW, который доступен только для записи, чтение CW не допускается.

Рис. 3.14. Программируемый периферийный адаптер ВВ55:

а—структурная схема; б—условное графическое обозначение

Рис. 3.15. Организация портов А (а) и В (б) программируемого периферийного адаптера

Обмен информацией между МП и внутренними регистрами ППА осуществляется через двунаправленный шинный формирователь и управляется сигналами  , А0, A1,

, А0, A1,  и

и  в соответствии с требованиями к шине Microbus. Адресные сигналы выбирают один из внутренних регистров, а стробы

в соответствии с требованиями к шине Microbus. Адресные сигналы выбирают один из внутренних регистров, а стробы  и

и  управляют направлением передачи согласно табл. 3.1. Сигнал

управляют направлением передачи согласно табл. 3.1. Сигнал  необходим для выбора кристалла.

необходим для выбора кристалла.

Таблица 3.1

| A1 | A0 |

|

|

| Операция |

| DПорт A | |||||

| DПорт B | |||||

| DПорт C | |||||

| Недопустимо | |||||

| Порт AD | |||||

| Порт BD | |||||

| Порт CD | |||||

| УправлениеD | |||||

| X | X | X | Нет операции | ||

| X | X | X | X | Нет операции |

Вход RESET служит для аппаратного сброса БИС в исходное состояние. Все внутренние регистры ППА, включая регистр управляющего слова CW, устанавливаются в 0. Сброс CW соответствует переводу всех портов в режим прямого ввода без квитирования.

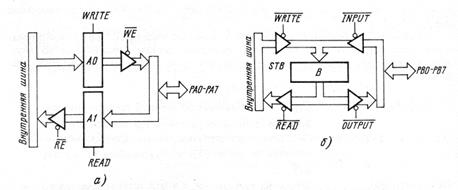

Дальнейшая настройка ППА выполняется программно с помощью специального управляющего слова MS (Mode Selection), которое назначает режим работы каждому каналу. Эти режимы могут быть изменены в любое время. Для хранения MS используется регистр CW.

Регистр управляющего слова 7-разрядный. Запись в него осуществляется только при передаче в ППА управляющего слова с D7 = 1 (признак слова MS), которое определяет режим работы каждого канала ВВ в соответствии с форматом, приведенным на рис. 3.16, а. Каждое из управляющих устройств группы А или В принимает свою часть слова выбора режима. При записи нового управляющего слова все буферные регистры портов устанавливаются в 0.

Рис. 3.16. Форматы управляющих слов MS (а) и BSR (б) программируемого периферийногоадаптера

Адаптер поддерживает три режима работы портов:

режим 0—однонаправленный ВВ без квитирования (применим к любому из трех портов);

режим 1—однонаправленный ВВ с квитированием (применим к портам А и В);

режим 2—двунаправленный ВВ (допускается только для порта А).

При работе портов А и В в режимах 1 и 2 часть линий порта С из соответствующей группы используется для управления обменом с внешними ПУ. Функциональные отличия портов предопределены их структурной организацией.

При D7 = 0 управляющее слово применяется для независимой установки (сброса) разрядов выходного порта С и носит название BSR (Bit Set/Reset). Выборочная манипуляция содержимым выходного буферного регистра порта С важна при его использовании в качестве шины управления ПУ. Формат слова BSR представлен на рис. 3.16, б.

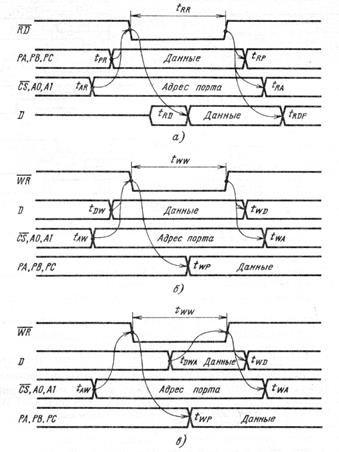

В режиме 0 осуществляется прямой однонаправленный ВВ через любой из трех портов без каких-либо сигналов сопровождения. Данные вводятся или выводятся через выбранный канал в соответствии с временными диаграммами на рис. 3.17. В данном режиме интерфейс можно представить как набор параллельных линий ВВ, организованных в две байтовые и две 4-разрядные шины, причем каждая может быть применена либо для ввода, либо для вывода независимо от других (рис. 3.18). Входная информация адаптером не запоминается и читается при низком уровне напряжения сигнала на входе  . Выходная информация защелкивается в выходной буферный регистр выбранного порта по срезу системного сигнала

. Выходная информация защелкивается в выходной буферный регистр выбранного порта по срезу системного сигнала  и остается на выходе порта до нового цикла вывода или изменения режима.

и остается на выходе порта до нового цикла вывода или изменения режима.

Рис. 3.17. Временные диаграммы режима 0:

а—ввод в режим 0; б—вывод в режим 0 (вариант ВВ55); в—вывод в режиме 0 (вариант ВВ55А)

| Рис. 3.18. Организация однонаправленного ВВ без квитирования: а—группа А; б—группа В | Рис. 3.19. Временные диаграммы режима 1: а—ввод; б—вывод |

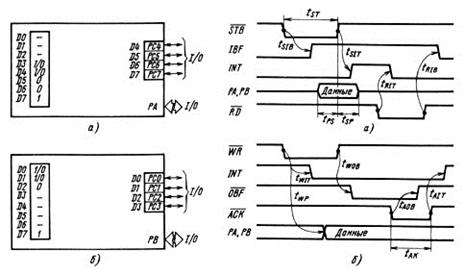

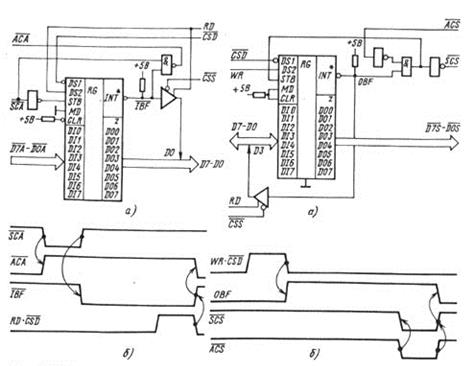

Режим 1 обеспечивает организацию однонаправленного ВВ с квитированием через порты А и В. Входные и выходные данные фиксируются во внутренних регистрах ППА. Управление вводом (рис. 3.19, а) осуществляется сигналами

(Strobe) Строб записи данных во входной регистр-защелку. Загрузка данных осуществляется по

(Strobe) Строб записи данных во входной регистр-защелку. Загрузка данных осуществляется по

фронту

IBF (Input Buffer Full) Подтверждение загрузки данных. Сигнал устанавливается по срезу  и

и

сбрасывается по фронту

INT (Interrupt) Запрос на прерывание. Сигнал устанавливается по фронту  и сбрасывается по

и сбрасывается по

срезу  . Используется для организации ввода по прерываниям

. Используется для организации ввода по прерываниям

Другой набор сигналов управления применяется при выводе данных (рис. 3.19, б):

(Output Buffer Full) Строб вывода новых данных. Низкий уровень сигнала

(Output Buffer Full) Строб вывода новых данных. Низкий уровень сигнала  информирует о выводе

информирует о выводе

новых данных. Сигнал  устанавливается по фронту

устанавливается по фронту  и сбрасывается по срезу

и сбрасывается по срезу

(Acknowledge) Подтверждение приема выходных данных со стороны внешнего устройства. Низкий

(Acknowledge) Подтверждение приема выходных данных со стороны внешнего устройства. Низкий

уровень напряжения сигнала сообщает ППА, что данные приняты

INT (Interrupt) Запрос на прерывание. Сигнал устанавливается по фронту  и сбрасывается по

и сбрасывается по

срезу  . Используется для организации вывода по прерываниям

. Используется для организации вывода по прерываниям

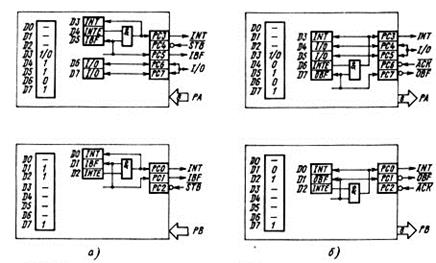

Для генерации вышеуказанных сигналов управления применяются отдельные линии порта С в соответствии с рис. 3.20. Свободная от управления часть порта С может выполнять свою стандартную функцию ВВ в режиме 0.

Рис. 3.20. Организация однонаправленного ВВ с квитированием:

а—ввод; б—вывод

Для управления обменом в режиме 1 со стороны ЦП предусмотрен программный доступ к линиям INT, IBF и  . Доступ организован через операцию чтения порта С. На рис. 3.20 показано, как при этом интерпретируются отдельные разряды введенных данных, называемые словом состояния SW адаптера. В состав SW входят также флажки разрешения прерывания INTE, управление состоянием которых может быть выполнено с помощью команды BSR с соответствующим параметром. Генерация запроса на прерывание INT и установка связанного с ним одноименного флажка готовности в SW возможна только при установленном флажке INTE. Функция маскирования прерывания позволяет запретить или разрешить работу устройства ВВ, не затрагивая какие-либо другие устройства в структуре прерываний.

. Доступ организован через операцию чтения порта С. На рис. 3.20 показано, как при этом интерпретируются отдельные разряды введенных данных, называемые словом состояния SW адаптера. В состав SW входят также флажки разрешения прерывания INTE, управление состоянием которых может быть выполнено с помощью команды BSR с соответствующим параметром. Генерация запроса на прерывание INT и установка связанного с ним одноименного флажка готовности в SW возможна только при установленном флажке INTE. Функция маскирования прерывания позволяет запретить или разрешить работу устройства ВВ, не затрагивая какие-либо другие устройства в структуре прерываний.

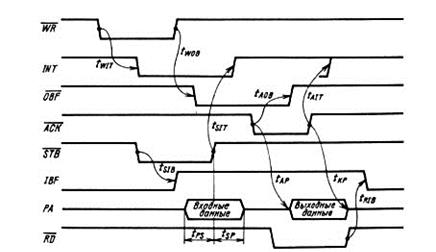

Особенности порта А (см. рис. 3.15 и 3.20) дают возможность организовать двунаправленный ВВ, называемый также режимом 2. В данном режиме линии РА7—РА0 выполняют роль двунаправленной трехстабильной шины, управляемой сигналами  , IBF,

, IBF,  ,

,  и INT согласно временным диаграммам на рис. 3.21.

и INT согласно временным диаграммам на рис. 3.21.

Рис. 3.21. Временные диаграммы режима 2

Сигналы IBF и  информируют внешнее устройство о готовности принять или передать данные соответственно. Правила их формирования тождественны правилам режима 1. В соответствии с состоянием IBF и

информируют внешнее устройство о готовности принять или передать данные соответственно. Правила их формирования тождественны правилам режима 1. В соответствии с состоянием IBF и  внешнее ПУ либо генерирует очередные данные, сопровождая их стробом

внешнее ПУ либо генерирует очередные данные, сопровождая их стробом  , либо формирует сигнал подтверждения приема

, либо формирует сигнал подтверждения приема  , готовясь к приему данных. Низкий уровень напряжения сигнала

, готовясь к приему данных. Низкий уровень напряжения сигнала  открывает выходные буферы порта А, разрешая выдачу данных на шину. В остальных случаях шина РА имеет высокое выходное сопротивление.

открывает выходные буферы порта А, разрешая выдачу данных на шину. В остальных случаях шина РА имеет высокое выходное сопротивление.

Сигнал INT используется для организации ВВ по прерываниям. Логика его формирования приведена на рис. 3.22. При получении очередного запроса на прерывание ЦП читает слово состояния SW и по флажкам IBF,  уточняет статус порта А, выполняя ввод или вывод очередных данных. В SW предусмотрены два независимых флажка разрешения прерывания для ввода и вывода, что дает возможность переводить порт либо в режим ввода, либо в режим вывода выборочно.

уточняет статус порта А, выполняя ввод или вывод очередных данных. В SW предусмотрены два независимых флажка разрешения прерывания для ввода и вывода, что дает возможность переводить порт либо в режим ввода, либо в режим вывода выборочно.

| Рис. 3.22. Организация двунаправленного ввода-вывода | Рис. 3.23. Формат слова состояния SW программируемого периферийного адаптера |

Порты А, В и С для работы в том или ином режиме программируются независимо друг от друга. Так, если порт В запрограммирован для ввода данных в режиме 1, то порт А может выполнять любую другую операцию обмена из числа возможных. Свободная от управления часть порта С также программируется либо для ввода, либо для вывода в режим 0, причем младшая половина порта независимо от старшей. Часть порта С, занятая под управление обменом, реализует функцию слова состояния в соответствии с форматом, представленным на рис. 3.23.

Адаптеры типа ВВ55 относятся к приборам первого поколения и являются эффективным средством построения систем ВВ. Их улучшенный вариант ВВ55А осуществляет работу с расширенными стробами записи, генерируемыми системным контроллером ВК38 и МП ВМ85А.

Интерфейс радиальный параллельный. В качестве примера практического использования МБР ИР12 и ППА ВВ55/ВВ55А рассмотрим задачу построения адаптера интерфейса радиального параллельного, удовлетворяющего требованиям шины Microbus, стандарт на которую был разработан Британским комитетом по стандартизации промышленных средств обработки информации в 1969 г. под названием BS 4421. В нашей стране стандарт известен как интерфейс радиальный параллельный (ИРПР) [33]. Базовый вариант интерфейса предусматривает одностороннюю асинхронную передачу информации по параллельной 16/8-разрядной шине D0—D15/D7 (D1—D16/D8) от источника к приемнику на расстояние до 15 м. (В скобках приводятся отечественные обозначения сигналов ИРПР.) Передача байта данных сопровождается двумя управляющими сигналами: управление приемника АС (Acceptance Control) или запрос приемника (ЗП) и управление источника SC (Source Control) или строб источника (СТР), приведенными на рис. 3.24. Данные истинны, когда АС = 1 и SC = 1. Однако циклы передачи данных могут начинаться и выполняться только при условии, что сигналы готовности приемника А0 (ГП) и источника S0 (ГИ) активны. Скорость передачи данных не регламентирована и зависит от быстродействия обеих сторон.

Рис. 3.24. Временные диаграммы протокола ИРПР

В состав интерфейса входит ряд необязательных вспомогательных линий. Это прежде всего линии контроля четности DP0 (Data Parity) и DP1 (KP0, KP1) для младшего и старшего байта данных соответственно, а также линии состояния приемника А1—А8 (СП1—СП8) и линии состояния источника S1—S8 (СИ1—СИ8). Сигналы DP0, DP1 и S1—S8 выдаются аналогично данным, сигналы А1—А8 действительны только при АС = 1 и SC = 0. В некоторых случаях допускаются асинхронные сигналы состояния источника и приемника. Предусматривается также линия нуля Z (0 В) и экрана S (Э).

Из двух однонаправленных каналов может быть организован один двунаправленный ИРПР-канал с раздельными шинами данных. Для отличия одних и тех же функциональных линий, принадлежащих источнику и приемнику двунаправленного канала в их обозначение добавляется символ А (П)—приемная часть или S (И)—передающая часть, например АСА, SCA, АСS, SCS и т. д.

Функциональное назначение сигналов состояния источника и приемника конкретизируется в зависимости от использования интерфейса: печатающее устройство (ИРПР-ПЧ), дисплей (ИРПР-ВТ), фотосчитыватель, ленточный перфоратор (ИРПР-ПЛ) [33]. Например:

S1 (PV) Наличие или отсутствие контроля

S2 Внимание

А1 (АЕ) Ошибка четности

А2 Автономный режим

Уровень активности сигналов может быть как высоким (ИРПР-ЕС), так и низким (ИРПР-СМ).

Интерфейс ИРПР получил широкое распространение в практике связи МС с ПУ. Многие внешние устройства имеют встроенный интерфейс данного типа. Реализация интерфейса со стороны МС несложна и может быть выполнена на программном уровне (см. рис. 3.5) без дополнительных аппаратных затрат.

Интерфейс ИРПР-СМ используется для реального подключения стандартных ПУ: дисплеев, печатающих устройств, перфораторов, фотосчитывателей и т. д. Он является удобным средством обмена информацией между МС и внешним объектом, в качестве которого может выступать другая МС.

Реализация входного и выходного каналов адаптера ИРПР-СМ на базе МБР ИР12 приведена на рис. 3.25 и 3.26 соответственно. Внутренний интерфейс адаптера удовлетворяет требованиям, предъявляемым к шине Microbus. Учет низкого уровня активности входной и выходной шин данных ИРПР-СМ выполняется на программном уровне дополнительной инверсией данных. Согласование уровней активности внешней и внутренней шин данных возможно и на аппаратном уровне, однако это связано с вводом инвертирующего буфера, что приводит к росту аппаратных затрат. Нагрузочная способность выходного канала IOL = 100 мА. При необходимости ВВ дополнительных сигналов состояния (управления) используется адекватное расширение входного и выходного каналов адаптера.

| Рис. 3.25. Входной канал адаптера ИРПР-СМ: а—структурная схема; б—временные диаграммы | Рис. 3.26. Выходной канал адаптера ИРПР-СМ: а—структурная схема; б—временные диаграммы |

Простейший драйвер ИРПР-адаптера может содержать только две подпрограммы. Первая подпрограмма TTS—условный ввод с совмещением—возвращает в одном из флажков PSW, например в ZF, признак готовности ввода. При готовности (ZF = 0) возвращаются также введенные данные, для чего используется регистр А:

IBF EQU 01Н ;Маска IBF

TTI: IN CSS ;Ввод слова состояния

СМА ;Инверсия слова состояния

ANI IBF ;Выделение IBF

RZ ;Возврат, если нет готовности

IN CSD ;Ввод данных

СМА ;Прием нулевого байта

RET ;игнорируется

Вторая подпрограмма ТТО—условный вывод с совмещением. Выводимые данные передаются через регистр А:

NOBF EQU 08H ;Маска

ТТО: PUSH В

MOV В, А ;Сохранить слово данных

IN CSS ;Ввод слова состояния

СМА ;Инверсия слова состояния

ANI NOBF ;Выделение

MOV А, В ;Восстановление данных

POP В

RZ ;Возврат, если нет готовности

СМА ;Иначе—инверсия данных

OUT CSD ;Вывод данных

СМА ;При выводе нулевого байта

RET ;признак вывода вбрасывается

На основе этих двух подпрограмм могут быть построены все остальные: ВВ с занятием цикла, ввод с эхо-выводом и т. д.

Анализ временных диаграмм работы ППА в режиме 1 (см. рис. 3.19) показывает, что при его проектировании были учтены логические требования интерфейса ИРПР. Это дает возможность реализовать ИРПР-адаптер с минимальным числом дополнительных внешних элементов (рис. 3.27). Схема построена на базе ППА ВВ55/ВВ55А и двух шинных формирователей типа ВА87. Последние используются как для промежуточной инверсии входных и выходных шин интерфейса, так и для создания необходимой нагрузочной способности по выходу IL = 32 мA. Возможна их прямая замена на регистры ИР83.

Рис. 3.27. Схема адаптера ИРПР-СМ на базе ВВ55/ВВ55А

Отличие ИРПР-адаптера состоит в необходимости его инициализации перед началом работы. Это может быть сделано с помощью специальной программы:

MS EQU 0A7H ;А—вывод в режиме 1, В—ввод в режиме 1, С4,

С5—вывод в режиме 0

PAINI: PUSH PSW

MVI A, MS ;Mode Selection

OUT PPA + 3

MVI A, 5 ;INTE__B1, разрешение

OUT PPA + 3 ;прерываний по каналу В

MVI A, 0DH ;INTE__A1, разрешение

OUT PPA + 3 ;прерываний по каналу А

POP PSW

RET

Линии РС4 и РС5 ППА могут быть применены по усмотрению пользователя как в качестве входных (MS = 0AFH), так и выходных (MS = 0A7H). Напомним, что при инициализации ППА все регистры данных сбрасываются, следовательно, при выводе РС4 = РС5 = 0. Управление их состоянием выполняется с помощью команд BSR.

Процедуры условного ВВ PAI, РАО могут иметь тот же самый вид, что и TTI, ТТО для адаптера ИРПР-СМ на базе ИР12. Отличие состоит в отсутствии команд СМА, так как теперь инверсия осуществляется на аппаратном уровне. Кроме этого в процедурах используются разные адреса портов данных при вводе (CSD = PPA + 1) и выводе (CSD = PPA). Адрес порта слова состояния CSS = PPA + 3. Здесь под РРА понимается базовый адрес адаптера ВВ55.

Дата добавления: 2019-02-07; просмотров: 1443;