Цифровой компаратор.

Общие принципы построения комбинационных логических устройств.

Согласно приведенной ранее классификации общим свойством комбинационных логических устройств, является выражаемая в виде таблицы истинности однозначная связь входных и выходных сигналов. Поэтому таблица истинности и соответствующие ей ФАЛ позволяют однозначно определить алгоритм работы устройства и являются основой для его анализа и синтеза.

Алгоритм проектирования комбинационных устройств можно представить следующей последовательностью действий:

- составить таблицу истинности, характеризующую алгоритм работы проектируемого устройства;

- получить МДФ, описывающую работу устройства;

- привести полученную МДФ к базису заданных логических элементов;

- составить схемы устройства.

Возможности реализации данной методики мы рассмотрели ранее. Среди множества комбинационных устройств часто встречаются однотипные алгоритмы, реализация которых привела к созданию класса типовых комбинационных устройств. К ним, первую очередь, относятся мультиплексоры и демультиплексоры, преобразователи кода (шифраторы и дешифраторы), цифровые компараторы и сумматоры. Рассмотрим их свойства и алгоритмы функционирования.

Типовые комбинационные устройства

Мультиплексор

Мультиплексором называется комбинационное логическое устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал.

Согласно определению, мультиплексор должен иметь один выход (  ) и две группы входов: информационные (

) и две группы входов: информационные (  ) и адресные (

) и адресные (  ). Код, подаваемый на адресные входы, определяет, какой из информационных входов в данный момент подключен к выходному выводу. Поскольку

). Код, подаваемый на адресные входы, определяет, какой из информационных входов в данный момент подключен к выходному выводу. Поскольку  -разрядный двоичный код, подаваемый на адресные входы мультиплексора может принимать

-разрядный двоичный код, подаваемый на адресные входы мультиплексора может принимать  значений, то число информационных входов так же равняется

значений, то число информационных входов так же равняется  .

.

Таблица 8.1. (таблица истинности) отражает алгоритм работы мультиплексора, управляемого двухразрядным кодом адреса. В ней учтено, что мультиплексор обычно снабжается инверсным входом разрешения работы Е, позволяющим блокировать его работу.

Таблица 8.1. Таблица истинности мультиплексора

|

|

|

|

| х | х | ||

| |||

| |||

| |||

|

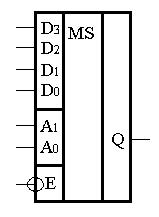

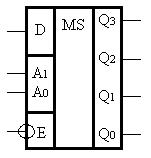

На рис.8.1.приведено условное графическое обозначение мультиплексора, соответствующего таблице истинности табл.8.1.

|

Рис. 8.1. Условное графическое обозначение мультиплексора.

Используя таблицу истинности нетрудно записать ФАЛ, описывающую работу мультиплексора:

(8.1)

(8.1)

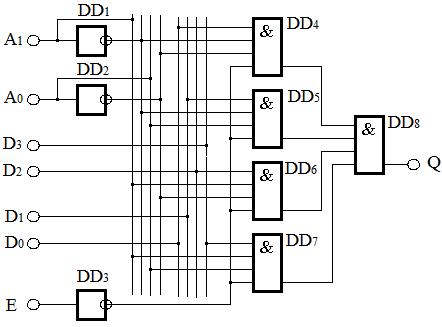

Выражение (8.1) позволяет построить логическую схему мультиплексора (рис.8.2).

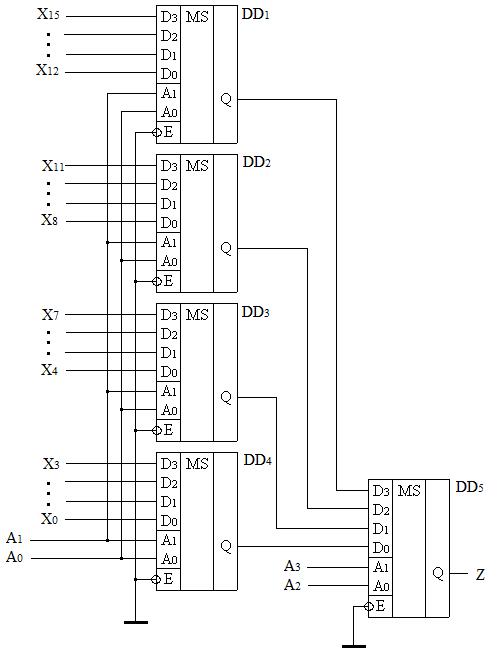

Обычно число входов мультиплексоров, выпускаемых в виде готовых интегральных схем, не превышает 16. При необходимости иметь большее число информационных входов используют структуру так называемого мультиплексорного дерева. Пример построения такой структуры показан на рис.8.3. В ней выходные сигналы мультиплексоров верхнего уровня (  ), управляемых младшими разрядами адресного слова (

), управляемых младшими разрядами адресного слова (  ), являются входными для мультиплексора нижнего уровня (

), являются входными для мультиплексора нижнего уровня (  ), управляемого старшими разрядами адресного слова (

), управляемого старшими разрядами адресного слова (  ).

).

|

Рис.8.2. Логическая схема мультиплексора.

Демультиплексор.

Демультиплексором называется комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов. То есть демультиплексор выполняет преобразование сигнала обратное мультиплексору. Поэтому при управлений  -разрядным адресным словом (

-разрядным адресным словом (  ) он имеет один информационный вход (

) он имеет один информационный вход (  ) и

) и  выходов (

выходов (  ).

).

Алгоритм работы демультиплексора, управляемого двухразрядным адресным словом (  ), приведен в таблице истинности (табл.8.2). Этой таблице соответствует система из четырех ФАЛ (выражение 8.2.). В ФАЛ так же учтено наличие инверсного входа разрешения работы

), приведен в таблице истинности (табл.8.2). Этой таблице соответствует система из четырех ФАЛ (выражение 8.2.). В ФАЛ так же учтено наличие инверсного входа разрешения работы

(8.2)

(8.2)

|

Рис.8.3. Мультиплексорное дерево.

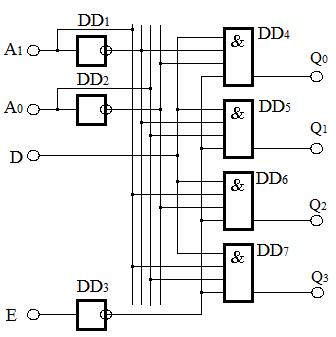

Полученная система ФАЛ позволяет синтезировать логическую схему демультиплексора (рис.8.4.).

Используя рассмотренный для мультиплексора подход, с использованием демультиплексора можно построить демультиплексорное дерево, что позволяет увеличить число выходов устройства до требуемого значения. При этом выходные сигналы демультиплексоров первого уровня используются для формирования сигнала разрешении работы (  ) демультиплексоров второго уровня.

) демультиплексоров второго уровня.

Таблица 8.2. Таблица истинности демультиплексора.

|

|

|

|

|

|

|

| x | x | |||||

| ||||||

| ||||||

| ||||||

|

а)

а)

|  б)

б)

|

Рис.8.4. Логическая схема а) и графическое обозначение демультиплексора.

Шифратор.

В цифровой технике используются различные методы кодировании информации. Поэтому возникает задача изменения вида ее кодирования. Эта задача решается с использованием комбинационных устройств, называемых преобразователями кода. Основой для разработки таких устройств является их таблица истинности. Из-за большого разнообразия различных видов кодирования, преобразователи кода, как правило, не выпускаются в виде готовых интегральных схем и проектируются по приведенной выше методике. Частным случаем преобразователя кода является шифратор. Шифратором, или кодером называется комбинационное логическое устройство для преобразования унитарного  -разрядного кода в двоичный код ( унитарный – код содержащий единицу только в одном разряде).

-разрядного кода в двоичный код ( унитарный – код содержащий единицу только в одном разряде).

В качестве примера, рассмотрим преобразователь десятиразрядного унитарного кода в двоичный, который, например, может быть использован для ввода десятичных чисел с клавиатуры в ЭВМ. Появление сигнала логической единицы в одном из разрядов входного кода соответствует вводу определенной десятичной цифры. Алгоритм работы такого шифратора приведен в таблице истинности табл. 8.3.

Таблица 8.3. Таблица истинности преобразователя кода

|

|

| 0 0 0 0 0 0 0 0 0 1 | 0 0 0 0 |

| 0 0 0 0 0 0 0 0 1 0 | 0 0 0 1 |

| 0 0 0 0 0 0 0 1 0 1 | 0 0 1 0 |

| 0 0 0 0 0 0 1 0 0 0 | 0 0 1 1 |

| 0 0 0 0 0 1 0 0 0 0 | 0 1 0 0 |

| 0 0 0 0 1 0 0 0 0 0 | 0 1 0 1 |

| 0 0 0 1 0 0 0 0 0 0 | 0 1 1 0 |

| 0 0 1 0 0 0 0 0 0 0 | 0 1 1 1 |

| 0 1 0 0 0 0 0 0 0 0 | 1 0 0 0 |

| 1 0 0 0 0 0 0 0 0 0 | 1 0 0 1 |

Используя приведенную таблицу можно записать систему ФАЛ, описывающую алгоритм работы данного шифратора (8.3):

(8.3)

(8.3)

По системе ФАЛ можно синтезировать логическую схему шифратора в заданном базисе элементов.

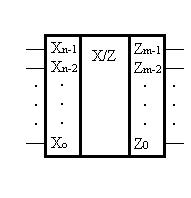

На рис.8.5. приведено общее условное обозначение преобразователя кода и обозначение дешифратора.

а)

а)

|  б)

б)

|

Рис.8.5. Условные обозначения преобразователя кода а) и дешифратора б)

Дешифратор

Дешифратором, или декодером называется комбинационное логическое устройство для преобразования чисел из двоичной системы счисления в унитарный код. Согласно определению дешифратор относится к классу преобразователей кодов. Здесь также понимается, что каждому входному двоичному числу ставится в однозначное соответствие сигнал, формируемый на определенном выходе устройства. Таким образом, дешифратор выполняет преобразование сигнала обратное шифратору. Если число адресных входов дешифратора (  ) связано с числом его выходов (

) связано с числом его выходов (  ) соотношением

) соотношением  , то дешифратор называется полным. В противном случае (

, то дешифратор называется полным. В противном случае (  ) дешифратор неполный. Примером неполного дешифратора являя двоично-десятичный дешифратор, которые для 4-х разрядного адресного кода формирует только 10 выходных сигналов.

) дешифратор неполный. Примером неполного дешифратора являя двоично-десятичный дешифратор, которые для 4-х разрядного адресного кода формирует только 10 выходных сигналов.

Таблица истинности дешифратора может быть легко получена из таблицы истинности шифратора (см. табл. 8.2) при замене входных сигналов выходными и наоборот. ФАЛ дешифратора повторяют ФАЛ демультиплексора (см выражение 8.2) при условии, что входной сигнал  равен лог 1. Поэтому и логическая схема дешифратора фактически аналогична схеме демультиплексора (см.рис.8.4).

равен лог 1. Поэтому и логическая схема дешифратора фактически аналогична схеме демультиплексора (см.рис.8.4).

Условное обозначение дешифратора приведено на рис. 8.6.

|

Рис.8.6. Условное обозначение дешифратора.

Цифровой компаратор.

Цифровым компаратором называется комбинационное логическое устройство, предназначенное для сравнения чисел, представленных в виде двоичных кодов. Число входов цифрового компаратора определяется разрядностью сравниваемых кодов, а на выходе всегда формируется только три сигнала: F = - равенство кодов, F > - если числовой эквивалент первого кода больше второго, F < - если числовой эквивалент первого кода меньше второго.

Работу цифрового компаратора при сравнении двух одноразрядных кодов (  и

и  ) поясняет таблица истинности (табл. 8.4).

) поясняет таблица истинности (табл. 8.4).

Таблица 8.4. Таблица истинности цифрового компаратора.

|

|

|

|

|

Анализ таблицы истинности показывает, что при любой комбинации входных сигналов на выходе компаратора может быть сформирован только один активный (например, единичный) логический сигнал. Поэтому, при любой разрядности входных кодов достаточно сформировать только любые два из выходных сигналов. Третий сигнал всегда может быть получен из двух известных.

Приведенной таблице истинности соответствует следующая система ФАЛ:

(8.4)

(8.4)

Анализируя полученные ФАЛ можно сказать, что для уменьшения аппаратных затрат на реализацию удобнее всего первоначально получить значения  и

и  , а

, а  реализовать как их функцию.

реализовать как их функцию.

Выражение для  в цифровой технике имеет большое самостоятельное значение и называется функцией исключающее ИЛИ-НЕ или инверсия от суммы по модулю два (

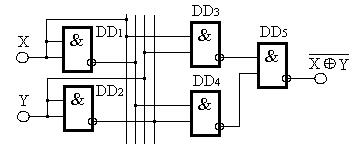

в цифровой технике имеет большое самостоятельное значение и называется функцией исключающее ИЛИ-НЕ или инверсия от суммы по модулю два (  ). На рис. 8.7 показана реализация этой функции на элементах 2И-НЕ и ее условное обозначение.

). На рис. 8.7 показана реализация этой функции на элементах 2И-НЕ и ее условное обозначение.

а)

а)

|  б)

б)

|

Рис.8.7. Реализация функции исключающее ИЛИ-НЕ а) и ее условное обозначение б).

Дата добавления: 2016-03-10; просмотров: 4365;