Выполнение операции суммирования

Составим таблицы истинности, описывающие алгоритм сложения младших и старших разрядов двоичного кода. Отличие этих устройств состоит в наличие или отсутствие сигнала переноса из младших разрядов.

| Таблица 8.5. Таблица истинности сложения младших разрядов.

| Таблица 8.6. Таблица истинности сложения старших разрядов.

|

В таблицах обозначено:  и

и  - разряды слагаемых,

- разряды слагаемых,  - разряд суммы,

- разряд суммы,  - разряд переноса в старший разряд,

- разряд переноса в старший разряд,  = разряд переноса из младшего разряда.

= разряд переноса из младшего разряда.

ФАЛ, соответствующие таблице 8.5. имеют вид:

(8.5)

(8.5)

Нетрудно заметить, что для получения разряда суммы над слагаемыми необходимо выполнить операцию исключающего ИЛИ. Действительно,  то есть инверсия от

то есть инверсия от  определяется тем же выражением, что и функция

определяется тем же выражением, что и функция  в цифровом компараторе.

в цифровом компараторе.

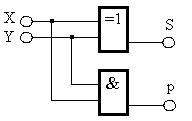

Устройство, реализующее данный алгоритм работы, называется полусумматором. Его схема и условное изображение приведены на рис.8.8.

а)

а)

|  б)

б)

|

Рис.8.8. Логическая схема а) и условное обозначение б) полусумматора.

ФАЛ для таблицы 8.6 имеет более сложный вид:

(8.6)

(8.6)

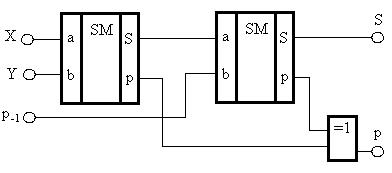

Нетрудно заметить, что в этом случае для получения разряда суммы необходимо два раза выполнить операцию исключающего ИЛИ, сначала над слагаемыми, а затем над полученным результатом и разрядом переноса из младшего разряда. Устройство, реализующее данный алгоритм работы, называется одноразрядным сумматором. Его логическая схема и условное обозначение приведены на рис.8.9.

а)

а)

|  б)

б)

|

Рис.8.9. Логическая схема а) и условное обозначение б) одноразрядного сумматора.

Дата добавления: 2016-03-10; просмотров: 1196;