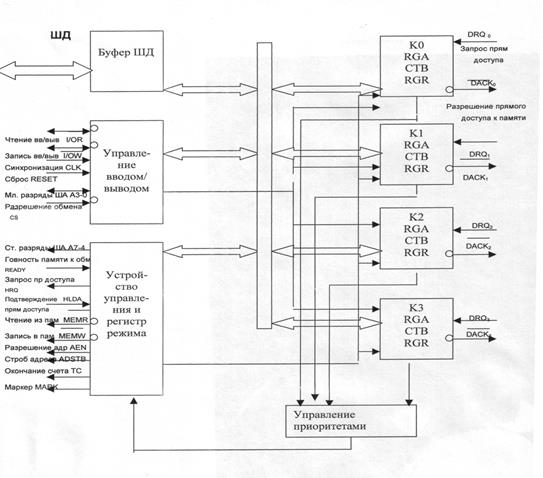

Программируемый контроллер прямого доступа к памяти.

Такой контроллер служит для управления обменом данными между четырьмя ПУ и памятью. Управление работой каждого из 4 каналов ПДП осуществляется с помощью двух 16-разрядных регистров: регистра начального адреса и регистра управления. В регистр начального адреса при программировании БИС заносится начальный адрес передаваемого массива данных . В 14-и младших разрядов регистра управления размещается счетчик байт, в который заносится число на единицу меньше длины передаваемого массива данных. Два оставшихся разрядов (15 и 14) регистра управления определяют тип операции обмена: 00 – контроль, 01 – запись в память, 10 – чтение из памяти, 11 – запрещенное состояние.

Связь контроллера с системным интерфейсом микроЭВМ осуществляется по шине данных ШД. Запись информации в регистр начального адреса и в регистр управления производится программным путем перед началом передачи данных.

По четырем входным линиям DRQ запросов от ПУ внешние устройства сигнализируют контроллеру об их готовности к передаче данных. Программно запросам DRQ могут быть назначены либо фиксированные приоритеты (при этом DRQ0 - высший, а DRQ3 - низший), либо циклические приоритеты.

|

В ответ на получение запроса DRQ контроллер сигналом

извещает ПУ о начале запрошенного им цикла ПДП.

Когда контроллер получает управление системной шиной он выводит на ШД 8 старших бит адреса памяти из старшей половины регистра начального адреса работающего канала ПДП. По сигналу «Строб адреса» ADSTB эти 8 бит загружаются во внешний регистр старших разрядов адреса, выходы которого подключены к линиям А15 - А8 шины адреса системного интерфейса. Младшие разряды адреса формируются на линиях А7 – А0 .

Контроллер может быть либо ведомым, либо ведущим. Ведомым контроллер является при его программировании или при считывании содержимого его внутренних регистров. При этом контроллер управляется МП. Когда же контроллер получает управление системным интерфейсом он становится ведущим и управляет процессом передачи данных без участия микропроцессора.

|

Если контроллер ведомый, то он по сигналу

|

принимает с ШД байт и загружает его в адресуемый по линиям А3 – А0 внутренний регистр. По сигналу

содержимое адресуемого регистра передается на ШД (чтение из контроллера).

|

Когда контроллер является ведущим, то он формирует пару сигналов

|

при передаче данных в основную память, и

при передаче данных из памяти в ПУ.

Сигнал «Запрос ПДП» HRQ подается на вход HOLD микропроцессора и сигнализирует о необходимости его отключения от системной шины.

Сигнал «Подтверждение ПДП» HLDA формируется МП и извещает контроллер о том, что он может управлять системной шиной.

Сигнал «Разрешение адреса» AEN служит для управления работой шинных формирователей, связывающих МП, и другие устройства с системной шиной.

Сигнал «Окончание счета» ТС форсируется при достижении нуля в 14-битном счетчике работающего канала. Это сигнал извещает об окончании передачи заданного блока данных.

Дата добавления: 2015-08-14; просмотров: 1412;