Программируемый контроллер прерываний фирмы Intel .

Программируемый контроллер прерываний обеспечивает управление восьми уровневыми векторными приоритетными прерываниями, то есть один контроллер прерываний обеспечивает приемную обработку до восьми сигналов прерывания.

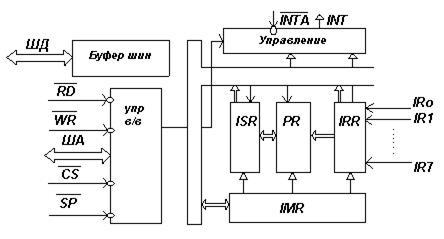

Структурная схема контроллера прерываний имеет следующий вид. (Рис.1.)

Рис.1.

Рис.1.

-запрос прерывания

-запрос прерывания

Запросы прерывания обрабатываются тремя взаимосвязанными регистрами. Регистр запросов (IRR) фиксирует все запросы прерываний, а регистр обслуживания (ISR) хранит только те прерывания, которые приняты на обслуживание .

Регистр масок-IMR идентифицирует маскируемые коды прерывания.

Шифратор приоритетов (арбитр приоритетов)-PR анализирует содержимое этих трех регистров и определяет нужно или нет генерировать сигнал запроса прерывания INT.

Контроллер прерываний может работать в одном из двух режимов:

1)контроллер является ведущим.

2)контроллер является ведомым.

Если на вход контроллера поступает сигнал SP с отриц.=1, то в этом случае контроллер является ведущим, в противном случае ведомым. Когда контроллер ведомый, то микропроцессор загружает в его регистры специальную управляющую информацию. Когда контроллер ведущий, то он управляет процессом передачи данных.

Рассмотрим алгоритм работы контроллера:

1)ПУ посылает по одной из линий  единичный сигнал.

единичный сигнал.

2)в регистре IRR происходит установка соответствующих разрядов в единицу под действием сигналов, поступающих от ПУ.

3)незамаскированные запросы, то есть те, для которых соответствующие разряды регистров IMG содержат 1, передаются в арбитр PR ,замаскированные запросы при этом блокируются.

4)арбитр PR выделяет наиболее приоритетный запрос и передает его в регистр обслуживания ISR.

5)приоритет запроса сравнивается с текущим приоритетом программы, выполняемой в микропроцессоре. Если приоритет запроса выше приоритета программы, то контроллер формирует сигнал прерывания INT, в противном случае обработка запроса откладывается.

6)Микропроцессор принимает микро запросы прерываний INT и начинает реализовывать последовательности прерываний, выполняя с цикла подтверждения прерывания, с формированием сигнала  в каждом из этих циклов.

в каждом из этих циклов.

7)В первом цикле подтверждение с прерывания происходит установка соответствующего разряда ISR и сброса аналогичного сигнала в регистре IRR.

8)Во втором цикле подтверждение прерывания текущее содержимое адреса прерывания передается в микропроцессор по шине данных.

9)Микропроцессор принимает этот адрес и использует его для обращения к таблице векторов прерывания, где хранятся сами вектора прерывания.

10)Текущее значение вектора прерывания , прерванное программой, запоминается в стеке, а вместо него в микропроцессор загружается вектор прерывания , выбранный из таблицы векторов прерывания. Управление передается прерывающей программе по адресу, содержащемуся в первом слове вектора прерывания.

11)По завершению прерывающей программы происходит восстановление сохраненного в стеке вектора прерывания прерванной программы, после этого управление возвращается к прерванной программе с той точки, где произошло прерывание.

Контроллер может быть запрограммирован на один из следующих режимов работы:

1)вложенные прерывания.

Каждому из восьми входов запросов прерывания  назначается фиксированный приоритет , при этом наивысший приоритет будет у запроса

назначается фиксированный приоритет , при этом наивысший приоритет будет у запроса  и далее в порядке убывания приоритетов до

и далее в порядке убывания приоритетов до  .Запрос с большим приоритетом прерывает обслуживание того ПУ , у которого меньший приоритет.

.Запрос с большим приоритетом прерывает обслуживание того ПУ , у которого меньший приоритет.

2)круговой (циклический) приоритет

В этом режиме также каждому входу  назначается приоритет, однако, после запроса и обслуживания прерывания приоритеты изменяются в круговом порядке таким образом, что последний обслуженный вход будет иметь самый маленький приоритет.

назначается приоритет, однако, после запроса и обслуживания прерывания приоритеты изменяются в круговом порядке таким образом, что последний обслуженный вход будет иметь самый маленький приоритет.

Дата добавления: 2015-08-14; просмотров: 993;