Триггеры. Триггер – это устройство, имеющее два устойчивых состояния, способное под воздействием управляющего сигнала скачком переходить из одного состояния в другое и

Триггер – это устройство, имеющее два устойчивых состояния, способное под воздействием управляющего сигнала скачком переходить из одного состояния в другое и хранить это состояние сколь угодно долго. Способность хранить состояние сколь угодно долго и определяет "память" триггера.

Триггеры классифицируются:

- по числу информационных входов: с одним входом, с двумя входами и более;

- по моменту срабатывания: асинхронные и синхронные триггеры;

- по функциональному назначению:

триггеры с раздельным запуском (RS-типа),

счетные (Т-типа), комбинированные (RST-типа), универсальные (JK-типа), задержки (D-триггер) и др.;

- по типу входного воздействия: триггеры со статическими входами, триггеры с динамическими входами.

Статические входы – это такие, по которым входной сигнал оказывает свое воздействие в течение всей его длительности. При динамических входах сигнал воздействует на триггер только на длительности фронта или среза.

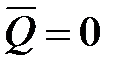

Все триггеры имеют два выхода – прямой "Q" и инверсный "  ". Информация на одном выходе является инверсией информации на другом. В основу построения триггеров положено применение логических элементов "ИЛИ-НЕ" или "И-НЕ" и обратных связей.

". Информация на одном выходе является инверсией информации на другом. В основу построения триггеров положено применение логических элементов "ИЛИ-НЕ" или "И-НЕ" и обратных связей.

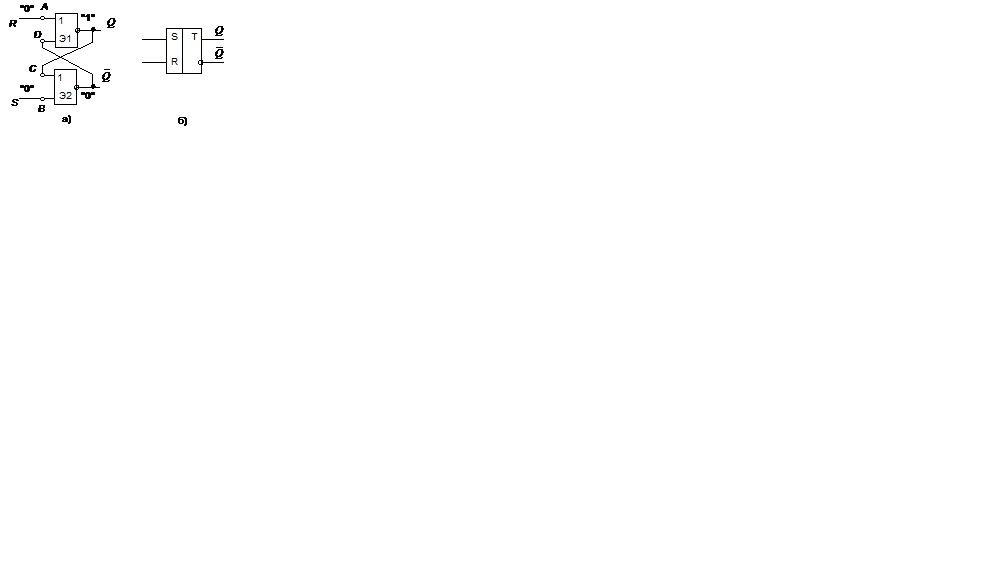

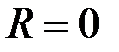

Схема RS триггера на элементах "ИЛИ-НЕ" приведена на рис.18.1а. На рис. 18.1б показано его условное обозначение. Управление схемой.

Входы Входы

| прямой выход | |

| S | R | Qn+1 |

| Qn | ||

| Неопреде-ленность |

в)

Рис. 18.1

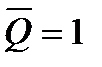

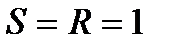

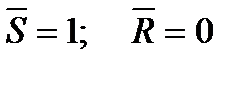

осуществляется по уровню логической "1". Это значит, что когда на входах присутствует "0", т. е.  ,

,  , состояние триггера не меняется. Уровень "0" является нейтральным.

, состояние триггера не меняется. Уровень "0" является нейтральным.

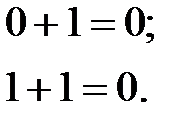

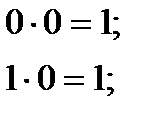

Перед анализом работы схемы приведем логические действия элемента "ИЛИ-НЕ":

(18.1)

(18.1)

Пусть после включения питания на входах и выходах схемы установились состояния: R = 0; S = 0; Q = 1;  . Уровень "1" с выхода Q поступает на вход С элемента Э2. На входе В по условию присутствует "0". Согласно (18.1) входные сигналы Э2 сформируют на его выходе уровень логического "0".

. Уровень "1" с выхода Q поступает на вход С элемента Э2. На входе В по условию присутствует "0". Согласно (18.1) входные сигналы Э2 сформируют на его выходе уровень логического "0".

Этот уровень поступает на вход D элемента Э1. На входе А этого элемента также присутствует "0". Такие состояния, согласно (18.1), формируют на выходе Э1 уровень логической "1". Таким образом, состояние первого элемента поддерживает состояние второго и наоборот, т. е. это устойчивое состояние триггера.

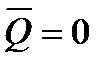

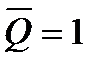

Пусть в некоторый момент времени t1 на вход R поступает сигнал с логическим уровнем "1". Так как на входе D Э1 в это время присутствует уровень "0", то, согласно (18.1), уровень выхода Э1 скачком изменится с "1" до "0", т. е. Q = 0. Теперь на входы С и В элемента Э2 воздействует уровень логического "0". Поэтому выход Э2 скачком изменяет уровень от "0" до "1", т. е.  .

.

Новое состояние триггера так же устойчивое. Оно не изменится, когда на вход R будет воздействовать уровень логического "0". При поступлении на вход R новых "1" состояние триггера останется прежним. Оно изменится только в том случае, когда уровень "1" поступит на вход S. Таким образом, RS-триггер управляется поочередно по двум входам.

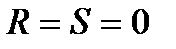

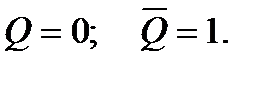

Таблица возможных состояний триггера приведена на рис. 18.1в. При отсутствии входных сигналов  триггер сохраняет информацию о последней из поступивших команд, т. е. служит элементом памяти. Сочетание входных сигналов

триггер сохраняет информацию о последней из поступивших команд, т. е. служит элементом памяти. Сочетание входных сигналов  является недопустимым. При таком сочетании триггер может принять любое состояние. Потому оно не применяется.

является недопустимым. При таком сочетании триггер может принять любое состояние. Потому оно не применяется.

Схема RS-триггера на элементах "И-НЕ" приведена на рис. 18.2. На рис. 18.1б показано его условное обозначение. Собственно триггер собран на элементах Э3 и Э4. Элементы Э1 иЭ2 выполняют роль инверторов. Логические действия для элементов "И-НЕ" имеют вид:

(18.2)

(18.2)

Исполнительным значением двоичного сигнала для элементов "И-НЕ" является "0", нейтральным – "1". Если на А и В присутствует уровень "1", то состояние триггера устойчивое. Пусть, например, А = В = 1, Q = 1,  . Уровень "1" с выхода Q поступает на вход С, а так как вход В = 1 по условию, то согласно (18.2) на выходе элемента Э4 формируется уровень логического "0". Этот уровень поступает на вход D элемента Э3. Вход А этого элемента равен "1" по условию. По (18.2) эти уровни сформируют на выходе элемента Э3 логическую "1". Таким образом, состояние элемента Э3 поддерживает состояние элемента Э4 и наоборот, т. е. это устойчивое состояние триггера.

. Уровень "1" с выхода Q поступает на вход С, а так как вход В = 1 по условию, то согласно (18.2) на выходе элемента Э4 формируется уровень логического "0". Этот уровень поступает на вход D элемента Э3. Вход А этого элемента равен "1" по условию. По (18.2) эти уровни сформируют на выходе элемента Э3 логическую "1". Таким образом, состояние элемента Э3 поддерживает состояние элемента Э4 и наоборот, т. е. это устойчивое состояние триггера.

Совершенно аналогично можно показать, что состояние А = В = 1, Q = 0,  так же устойчиво. Включение инверторов Э1 и Э2 позволяет изменить исполнительный уровень входных сигналов, т. е. для входов S и R исполнительным уровнем является "1", а нейтральным "0". Поэтому возможные состояния схемы рис. 18.2 соответствуют таблице рис. 18.1в. Согласно этой таблице состояние входов S = R = 0 является нейтральным и позволяет триггеру сохранять память о последней из поступивших команд. Чтобы изменить состояние выходов триггера, необходимо на вход S или R подать "1". Состояние S = R = 1 недопустимо.

так же устойчиво. Включение инверторов Э1 и Э2 позволяет изменить исполнительный уровень входных сигналов, т. е. для входов S и R исполнительным уровнем является "1", а нейтральным "0". Поэтому возможные состояния схемы рис. 18.2 соответствуют таблице рис. 18.1в. Согласно этой таблице состояние входов S = R = 0 является нейтральным и позволяет триггеру сохранять память о последней из поступивших команд. Чтобы изменить состояние выходов триггера, необходимо на вход S или R подать "1". Состояние S = R = 1 недопустимо.

Триггеры по рис. 18.1а и 18.2 переходят в новое состояние сразу после поступления входного сигнала и поэтому называются асинхронными.

Синхронные RS-триггеры.

Во многих устройствах необходимо синхронизировать во времени переключение триггеров. Дело в том, что неодновременное переключение может привести к появлению непредусмотренных состояний устройства и к срыву его работы. Синхронные триггеры имеют дополнительный вход для подачи на него синхронизирующего (тактового) импульса определенной длительности.

Синхроимпульс своим исходным (нулевым) значением блокирует (закрывает) информационные входы S и R. В этом случае триггер не реагирует на входные сигналы, сохраняя предыдущее состояние. Триггер воспринимает информацию на входах, когда значение синхронного импульса равно "1" и переходит в новое состояние на интервале среза синхроимпульса.

Схема синхронного RS-триггера приведена на рис. 18.3а. На рис. 18.3б – его условное обозначение. Во всех случаях, когда С = 0 на выходах элементов Э1 и Э2 уровни  , т. е. нейтральны для элементов Э3 и Э4 не зависимо от состояния входных сигналов S и R. В этом и заключается эффект блокирования входов.

, т. е. нейтральны для элементов Э3 и Э4 не зависимо от состояния входных сигналов S и R. В этом и заключается эффект блокирования входов.

При С = 1 на выходах элементов Э1 и иЭ2 сигналы становятся инверсными по отношению к исходным S и R. Их комбинация вызовет реакцию триггера в соответствии с таблицей рис. 18.1в.

Например:

- если S = R = 0, то  , триггер сохраняет «память» о предыдущем состоянии;

, триггер сохраняет «память» о предыдущем состоянии;

- если S = 1, а R = 0, то  ;

;  , триггер переходит в состояние "1", т. е.

, триггер переходит в состояние "1", т. е.  ;

;

- если S = 0, а R = 1, то  , триггер переходит в состояние "0", т. е.

, триггер переходит в состояние "0", т. е.

Пример наглядно показывает, что для входов S, R и С исполнительным уровнем является "1".

Кроме синхронных входов R и S синхронный триггер снабжается асинхронными входами SA и RA. Асинхронные входы позволяют задать триггеру определенное исходное состояние перед началом работы в синхронном режиме. При синхронном управлении триггером на входах SA и RA должен поддерживаться нейтральный уровень, т. е. "1".

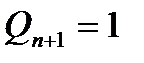

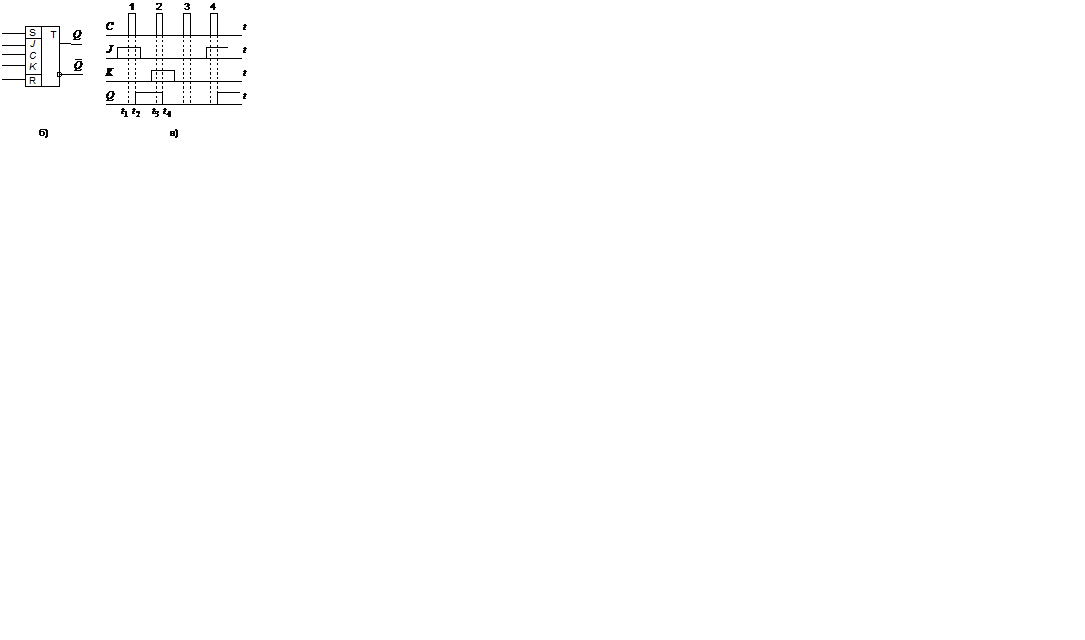

JK-триггеры – это универсальные синхронные триггеры. Работа JK-триггера описывается таблицей рис. 18.4а. Входы триггера  . Как и RS-триггер, он сохраняет свое состояние при J = K = 0. Когда J = 1, триггер переходит в состояние

. Как и RS-триггер, он сохраняет свое состояние при J = K = 0. Когда J = 1, триггер переходит в состояние  . При R = 1 – в состояние

. При R = 1 – в состояние  . При J = K = 1 начальное состояние триггера меняется на противоположное, т. е.

. При J = K = 1 начальное состояние триггера меняется на противоположное, т. е.  . Это основное отличие JK от RS-триггера.

. Это основное отличие JK от RS-триггера.

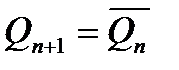

Условное обозначение JK-триггера показано на рис. 18.4б, а временные диаграммы, поясняющие его работу на рис. 18.4в. Во время действия тактового

| Входы | Прямой выход | |

| J | K |

|

| ||

|

А)

Рис. 18.4

импульса С = 1 на интервале  вход J = 1. Поэтому в момент среза импульса С триггер переходит в состояние Q = 1. На интервале

вход J = 1. Поэтому в момент среза импульса С триггер переходит в состояние Q = 1. На интервале  С = 0. Триггер не воспринимает входную информацию. На интервале второго тактового импульса

С = 0. Триггер не воспринимает входную информацию. На интервале второго тактового импульса  вход К = 1. Поэтому в момент t4 триггер переключается: Q = 0. Во время действия третьего синхроимпульса J = 0; K = 0. Поэтому он не меняет своего состояния.

вход К = 1. Поэтому в момент t4 триггер переключается: Q = 0. Во время действия третьего синхроимпульса J = 0; K = 0. Поэтому он не меняет своего состояния.

Обычно JK-триггеры снабжаются установочными входами R и S. Эти входы асинхронные. При S = 1 триггер устанавливается в состояние  . При R = 1 –

. При R = 1 –  .

.

Схема JK-триггеров достаточно сложна и в лекции не рассматривается. Схемное усложнение позволило ликвидировать состояние неопределенности и увеличить число входов J и K (обычно по 3).

Счетный Т-триггер реализует только четвертую строку таблицы рис.18.4а. Таким свойством обладает JK-триггер, когда его входы J = K = 1. При таком включении входов триггер переключается в момент среза каждого тактового импульса. Отсюда следует, что счетный триггер имеет один тактовый вход, который обозначают символом «Т». Обозначение Т-триггера приведено на рис. 18.5а. На рис.18.5б приведены временные диаграммы, поясняющие его работу. Из диаграмм видно, что частота повторения импульсов на выходе триггера Q в два раза меньше частоты повторения импульсов на входе Т, т. е. Т-триггер делит частоту входных импульсов на 2. Счетные триггеры широко применяются в счетчиках, распределителях и делителях частоты.

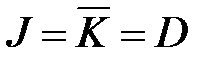

D-триггер запоминает входную информацию в момент фронта синхроимпульса и хранит ее до следующего тактового импульса. D-триггер может быть выполнен на основе JK-триггера, при включении на входе элемента "НЕ", обеспечивающего условие  . Отсюда следует, что D-триггер имеет тактовый вход С и вход D. Его работа описывается второй и третьей строкой таблицы рис. 18.4а, т. е.

. Отсюда следует, что D-триггер имеет тактовый вход С и вход D. Его работа описывается второй и третьей строкой таблицы рис. 18.4а, т. е.  . Поэтому D-триггер является элементом памяти и находит широкое применение, в том числе в регистрах. Условное обозначение D-триггера и временные диаграммы, поясняющие его работу, приведены на рис. 18.6.

. Поэтому D-триггер является элементом памяти и находит широкое применение, в том числе в регистрах. Условное обозначение D-триггера и временные диаграммы, поясняющие его работу, приведены на рис. 18.6.

В микросхемном исполнении триггеры выпускаются в составе многих серий цифровых интегральных микросхем. Для условного обозначения им присвоены следующие индексы:

RS-триггеры – ТР;

JK-триггеры – ТВ;

D-триггеры – ТМ.

Например, микросхема К555 ТР2 содержит 4 RS-триггера.

Микросхемы К555 ТВ6 и К555 ТВ9 включают в свой состав по два IK триггера каждая. Микросхемы позволяют путем внешних коммутационных изменений получить схемы, выполняющие функции RS, D и Т-триггеров.

Дата добавления: 2015-08-11; просмотров: 1693;