Запоминающие логические элементы (триггеры).

На основе простейших логических элементов могут быть созданы схемы, обладающие более сложными функциональными возможностями, обеспечивающими хранение поступающей на их входы информации, такими наиболее распространенными в вычислительной технике схемами являются триггеры. Триггерами называют большой класс электронных устройств, обладающих способностью длительно находиться в одном из двух или более устойчивых состояний и чередовать их под воздействием внешних сигналов. То, есть в отличие от логических элементов И, ИЛИ, НЕ и их комбинаций - это логические устройства с памятью. Их выходные сигналы (т.е. информация о том в каком состоянии они находится) зависит не только от того какие сигналы приложены на вход в данный момент времени, но и от сигналов, воздействовавших на них ранее. В зависимости от функционального назначения (возможностей) числа и назначения входов триггеры можно разделить на несколько видов. Тем не менее, любой вид триггера можно представить некоторой обобщенной схемой.

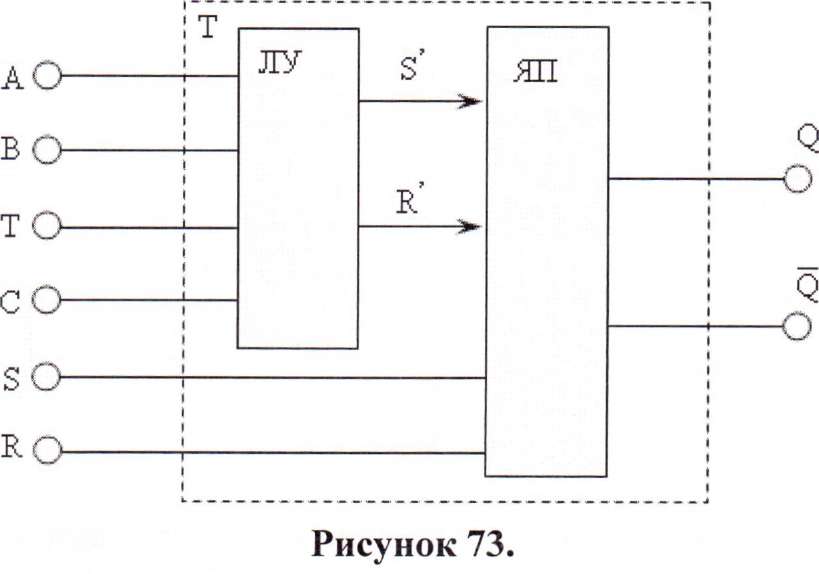

|

Из данной схемы видно что триггер Т в общем виде можно представить в виде устройства, состоящего из ячейки памяти ЯП и логического устройства управления, преобразующего входную информацию в комбинацию сигналов, под воздействием которых ЯП принимает одно из двух устойчивых состояний.

Информационные сигналы поступают на входы А и В ЛУ и преобразуются в сигналы S и R, поступают на ЯП. Процесс преобразования информационных сигналов осуществляется при воздействии сигналов, подаваемых на вход Т предустановки и вход С синхронизации. Вход Т обычно используется для разрешения приема информации, а исполнительный вход С обеспечивает тактируемый прием информации. В простейшем триггере ЛУ может отсутствовать, а информационные сигналы подаются непосредственно на входы S и R ЯП. При наличии входа С триггер называют синхронным, а при его отсутствии - асинхронным.

Изменение состояния асинхронного триггера происходит сразу же после соответствующего изменения потенциалов на его информационных входах А и В. В синхронном триггере изменение состояния может произойти только в момент присутствия соответствующего сигнала на входе С. Синхронизация может осуществляться импульсом (потенциалом) или фронтом (перепадом потенциала). В первом случае сигналы на информационных входах оказывают влияние на состояние триггера только при наличии разрешающего потенциала на входе С. Во втором случае воздействие информационных сигналов проявляется только в момент изменения потенциала на входе С, т.е. при переходе его от 1 к 0 или от 0 к 1. Универсальные триггеры могут работать как в синхронном так и в асинхронном режиме. В интегральном исполнении изготавливаются и применяются триггеры типов: RS; JK-триггер; D - триггер; Т - триггер.

SR - триггер является наиболее простой триггерной схемой:

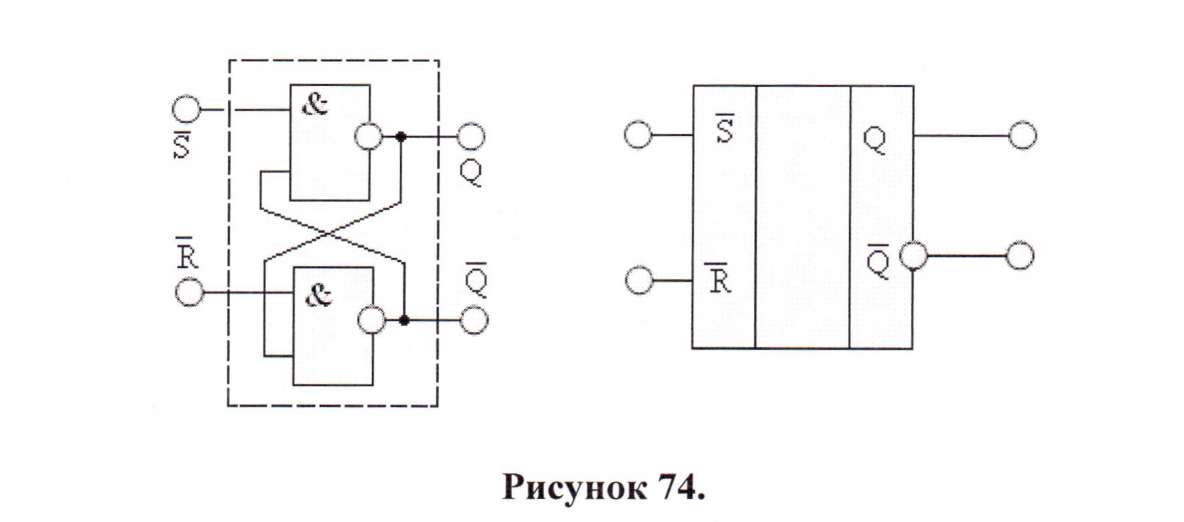

|

SR - триггер имеет два информационных входа S и R (   ). Подача на вход S сигнала 1, а на вход R сигнала 0 устанавливает на входе Q триггера сигнал 1. Наоборот, при сигналах S = О, R = 1 сигнал на выходе триггера Q=0. Функционирование SR - триггера с прямыми входами описывается уравнениями: ). Подача на вход S сигнала 1, а на вход R сигнала 0 устанавливает на входе Q триггера сигнал 1. Наоборот, при сигналах S = О, R = 1 сигнал на выходе триггера Q=0. Функционирование SR - триггера с прямыми входами описывается уравнениями:

|

Для SR - триггера комбинация S = 1 и R = 1 является запрещенной. После такой комбинации информационных сигналов состояние триггера будет неопределенным: на его выходе Q может быть 0 или 1. Существуют разновидности SR - триггеров, называемые Е, R и S - триггерами, для которых состояния S = R = 1 не является запрещенным. Е - триггер при S = R = 1 не изменяет своего состояния, S - триггер при S = R = 1 устанавливается в состояние Q = 1, а триггер R - триггер в этом случае устанавливается в состояние q=o.

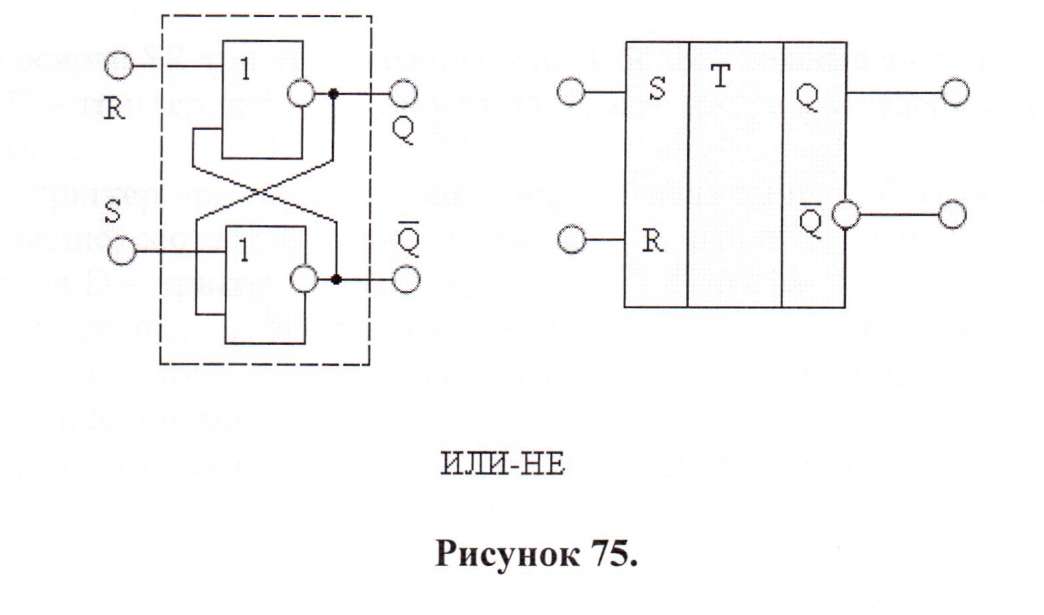

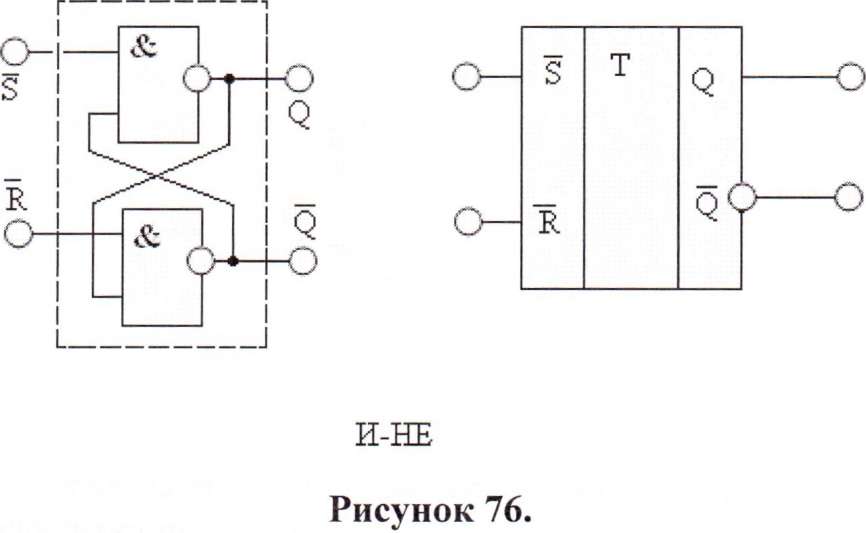

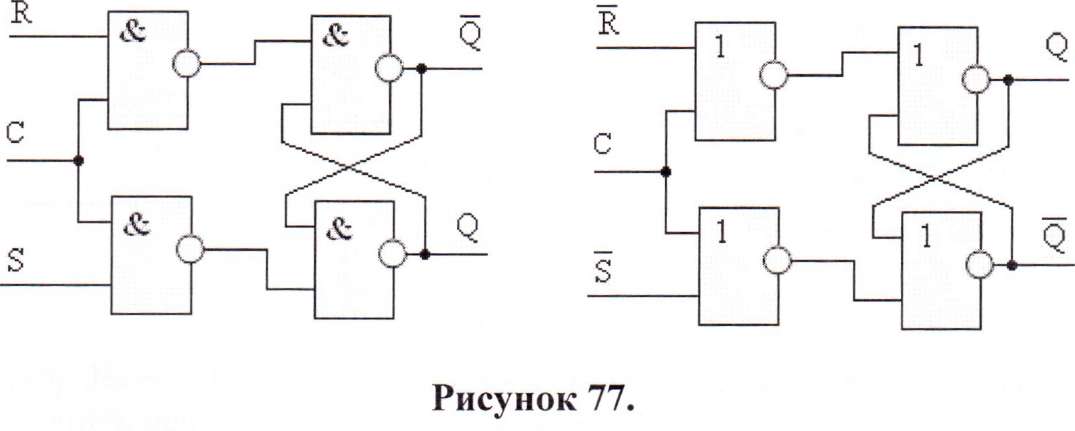

Возможные варианты схем асинхронных SR - триггеров:

|

|

| И возможные варианты синхронизируемых SR триггеров: |

Синхронный триггер SR также имеет запрещенную комбинацию SnRnCn=1.

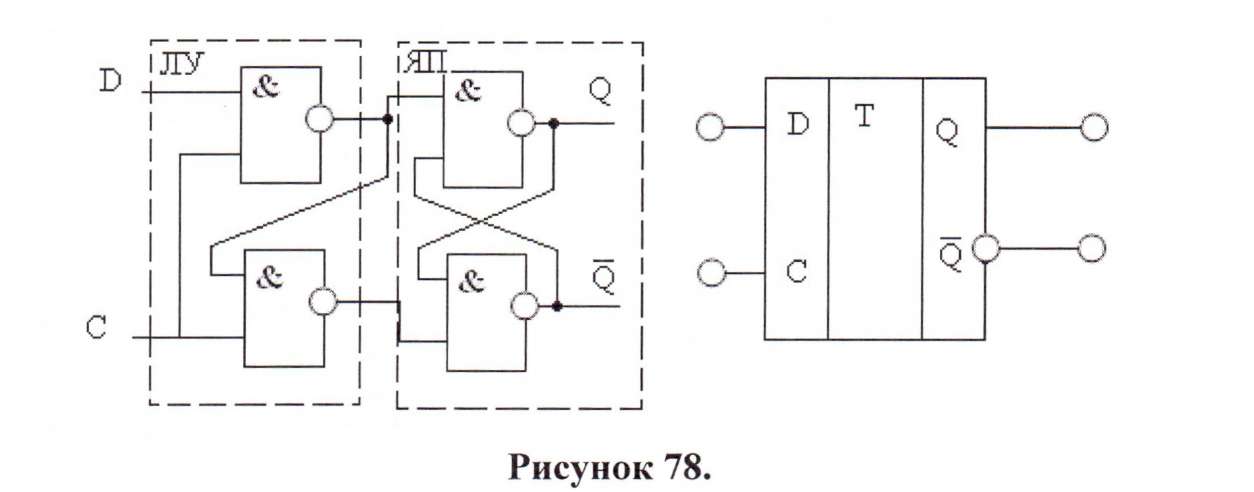

На основе SR триггера можно создать более сложные элементы. Это, например D - триггер, который иногда называют триггером задержки (Delay - задержка).

D - триггер при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D. Уравнение функционирования D - триггера имеет вид Qn = Dn-1. Это уравнение показывает, что выходной сигнал Qn изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, т.е. с задержкой на один период импульсов синхронизации.

Синхронизация D - триггера может осуществляться импульсом или фронтом.

|

Возможен также вариант D - триггера с инверсными входами, и дополнительным разрешающим входом Е.

|

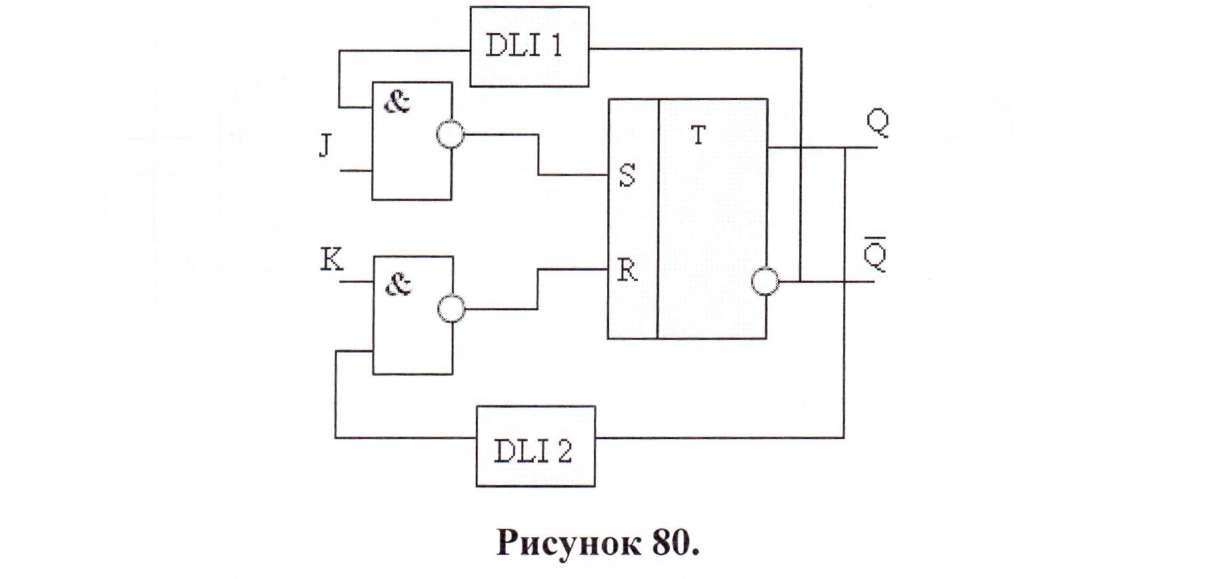

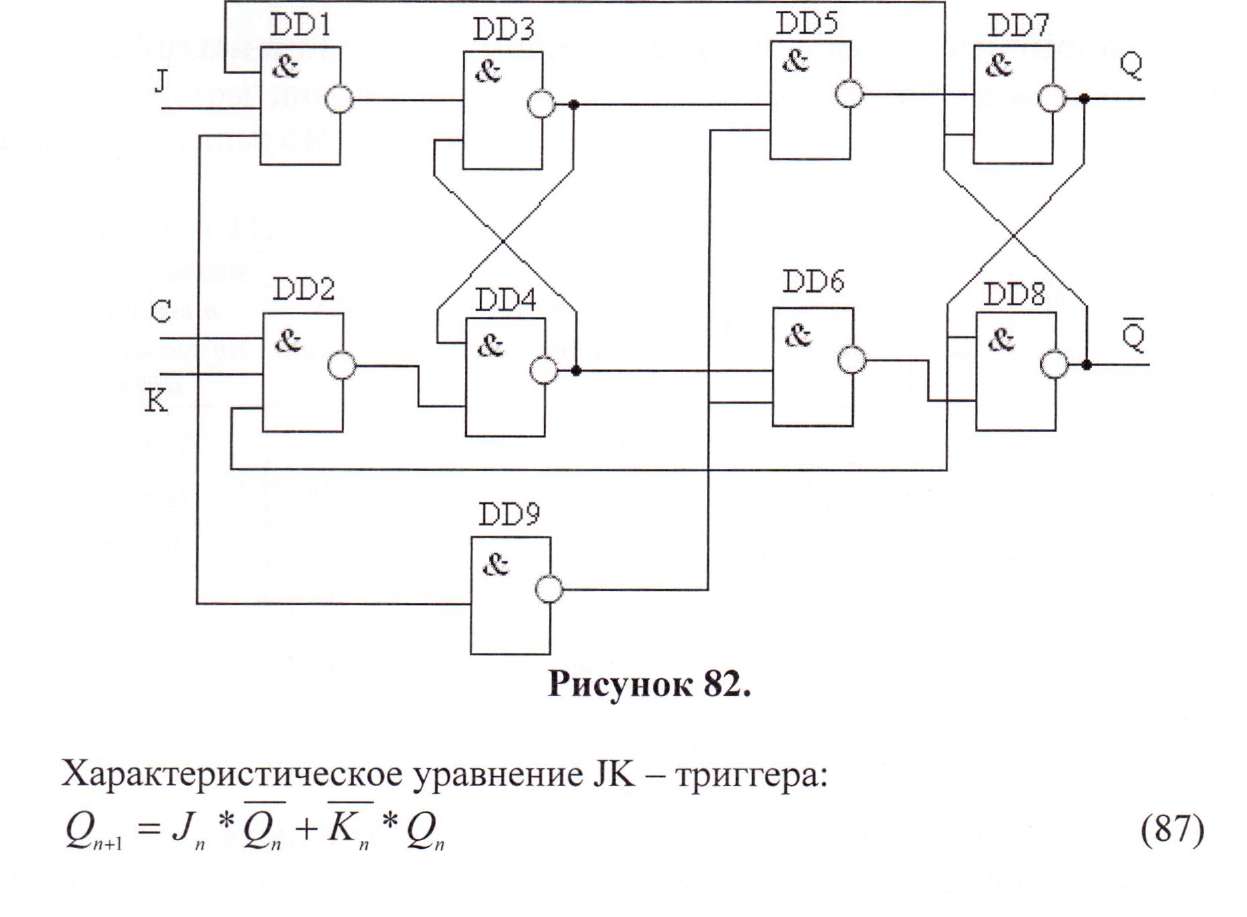

Триггер JK - типа называют универсальным. Схема JK - триггера позволяет исключить неопределенные состояния.

|

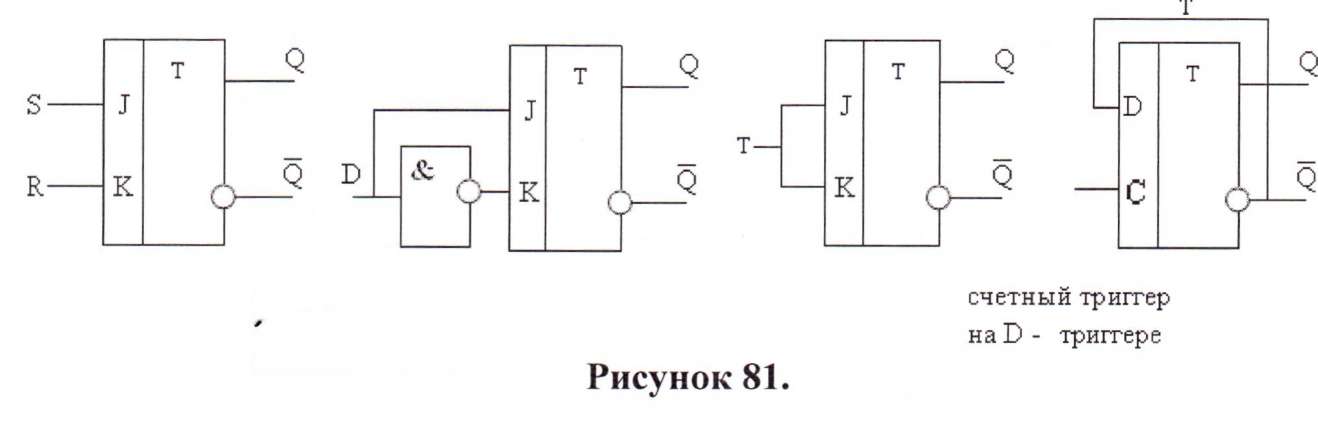

В этом триггере если на входы J и К одновременно подаются сигналы логической единицы, то состояние JK - триггера изменяется на противоположное при каждом новом приходящем импульсе. Таким образом если J и К объединены

мы получаем новую схему, которая называется счетным Т - триггером. Следовательно JK - триггер при определенных доработках схемы можно использовать как SR, D и Т - триггеры.

|

Универсальные JK - триггеры в интегральном исполнении обычно выполняется синхронными и двухступенчатыми. В них имеется основной триггер (первая ступень) в который записывается приходящая информация, и вспомогательный (вторая ступень) в который информация переписывается из первой ступени. Для построения такого триггера требуется в 2 раза больше логических элементов, но он обладает большей помехозащищенностью и т.о. обеспечивает лучшую сохранность информации.

|

Если же для построения такого триггера использовать интегральные SR - триггера, то схема будет иметь вид:

|

Дата добавления: 2015-08-11; просмотров: 2339;