А - на двухэмиттерных транзисторах; б - на тиристорах; в - на элементах И2Л2; г - динамического типа

Рис. 6.22. Структурная схема БИС статического ОЗУ типа ЭСЛ емкостью

Бит

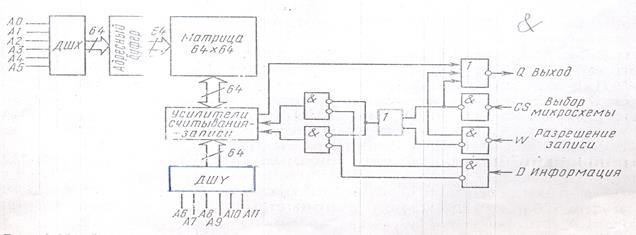

Вход разрешения записи W позволяет производить запись «0» и «1» в зависимости от состояния входа информации D. Выход ОЗУ Q нагружается на резистор сопротивлением 50 Ом, подключенный к источнику питания – 2 В.

Аналогично строятся БИС статических ОЗУ на других биполярных ЗЭ. Использование ЗЭ типа ТТЛШ направлено на повышение быстродействия БИС ОЗУ, а ЗЭ типа И2Л – на повышение информационной емкости. При этом для построения схем выборки микросхемы, дешифраторов и других схем управления используют простейшие вентили типа ЭСЛ. В буферных схемах, предназначенных для согласования внешних управляющих схем с БИС ОЗУ, используются преобразователи уровней ТТЛ→ЭСЛ и ЭСЛ→ТТЛ.

БИС статических ОЗУ на биполярных транзисторах развиваются в основном в область максимального быстродействия (tв.а=3÷10 нс для информационной емкости 64 – 16384 бит).

БИС ОЗУ на МДП-транзисторах представляет собой класс статических и динамических ОЗУ среднего быстродействия. Их разновидность и технические характеристики определяются типом ЗЭ и структурой МДП-транзисторов. БИС ОЗУ на p-МДП-транзисторах являются самыми простыми по схемотехнической и технологической реализации, но обладают низким быстродействием (tв.а=500÷1000 нс). БИС ОЗУ на n-МДП-транзисторах статического и динамического типов имеют tв.а=30÷500 нс и в настоящее время являются наиболее распространенными ОЗУ различной информационной емкости. БИС ОЗУ на КМДП-транзисторах отличаются повышенной схемотической и технологической сложностью, характеризуются средним и низким быстродействием и применяются в основном в микромощной аппаратуре.

Для построения БИС статических ОЗУ используют симметричные бистабильные ЗЭ на одноканальных или КДМП-транзисторах, а БИС динамических ОЗУ — трехтранзисторные или однотранзисторные ЗЭ на n-МДП-структурах (рис. 6.23). ЗЭ статических ОЗУ реализуются на 4—8 транзисторах с тремя информационными шинами (одна АШ, две РШ) и занимают относительно большую площадь (до 104 мкм2) на кристалле (рис. 6.23, а, б).

В основу работы динамических ЗЭ положено хранение информации в виде заряда на конденсаторе, включенном между информационным МДП-транзистором и общей шиной схемы (нулевой потенциал). Использование трехтранзисторных (рис. 6.23, в) и однотранзисторных (рис. 6.23, г) ЗЭ позволяет существенно повысить степень интеграции БИС и создавать динамические ОЗУ емкостью более 64 К бит. Однако при этом значительно усложняются схемы управления на кристалле, вводится схема регенерации информации, что приводит к снижению помехоустойчивости по сравнению со статическими ОЗУ.

Независимо от схемы ЗЭ информация хранится в конденсаторе Сзэ. В трехтранзисторном ЗЭ конденсатор Сзэ изолирован от разрядной шины и считывание информации происходит без ее разрушения. Однако из-за утечки тока в Сзэ требуется периодическая регенерация информации, что достигается подачей высокого потенциала на шину АШ и специальной схемой регенерации, подключенной к шинам РШ.

В однотранзисторный ЗЭ запись информации производится при подаче потенцииала РШ через открытый транзистор. Считывание производится током разрядки емкости Сзэ в шины РШ с разрушением информации.

Построение и принцип работы динамического ОЗУ рассмотрим на примере БИС динамического ОЗУ на n-МДП-транзисторах емкостью 64 К бит, структурная схема которого представлена на рис. 6.24. Накопитель в виде матрицы 128×512 выполнен на однотранзисторных ЗЭ. Такая организация обеспечивает полную регенерацию информации за 128 циклов при времени регенерации 2 мс. Два генератора тактовых сигналов управляются сигналами RAS(строб адреса строки) и CAS(строб адреса столбца). Сигналы, вырабатываемые схемой управления, и сигнал разрешения записи WE обеспечивают работу СЗУ в режимах записи, считывания, регенерации, мультипликации адресов. Для выборки ЗЭ требуется 16-разрядный адресный код, который подается на 8-разрядный адресный регистр в мультиплексном режиме (для сокращения числа выводов БИС). Сначала 8 младших разрядов кода фиксируются на регистре адреса сигналом RAS и выбирается строка. Затем 8 старших разрядов кода фиксируются сигналом CASи выбирается столбец. Сигнал CASодновременно является сигналом выбора микросхемы (в блоке ОЗУ). БИС данного ОЗУ имеет выход с тремя состояниями и совместима по логическим уровням с ИМС типа ТТЛ.

Для разработки БИС динамических ОЗУ используют и ЗЭ на И2 Л.

БИС ОЗУ на МДП-транзисторах развиваются как статические высокого быстродействия (tв.а=15÷20 нс) емкостью 1—4 К бит и динамические большой емкости (до 1 М бит).

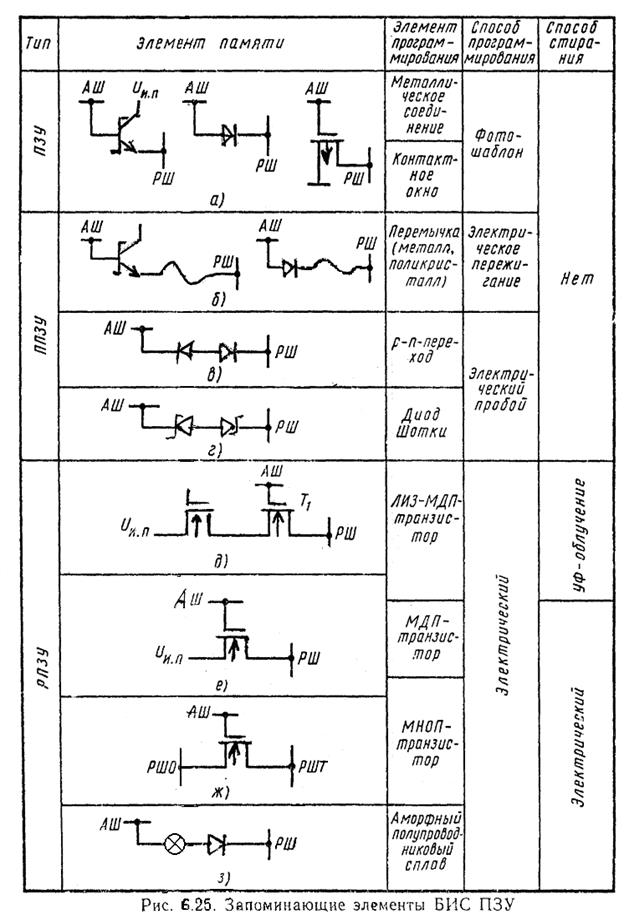

Постоянные ЗУ. Разновидность БИС постоянной памяти определяется типом ЗЭ, способами занесения и стирания информации. Элементная база и способы программирования для БИС ПЗУ, ППЗУ и РПЗУ приведена на рис. 6.25, а-з.

Состав таких БИС аналогичен БИС ОЗУ с двухкоординатной выборкой (в основном). Они содержат матричный накопитель для хранения m-разрядных двоичных слов, дешифраторы строк и столбцов, адресные формирователи, усилители считывания, селектор (разрядный формирователь) и другие схемы управления. ЗЭ располагаются в матричном накопителе в месте пересечения адресных и разрядных шин.

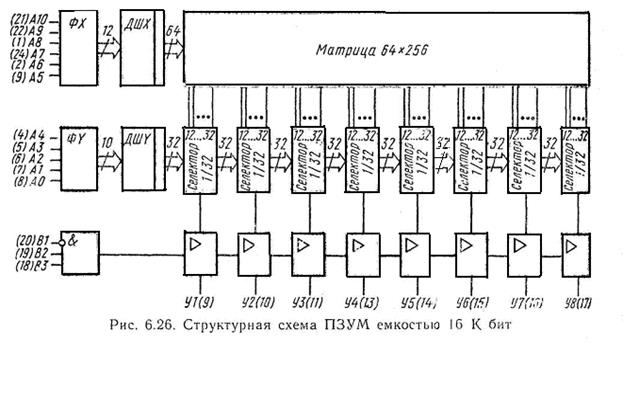

В БИС ПЗУ на ЗЭ, представленных на рис. 6.25, а, занесение информации осуществляется на этапе изготовления кристаллов с помощью сменного (заказного) фотошаблона путем изменения конфигурации металлизированной разводки или селективного вскрытия контактных окон под металлизацию. Соединение ЗЭ с шинами АШ и РШ соответствует хранению «1», отсутствие соединения — хранению «0». Такие ПЗУ называют масочными (ПЗУМ). Пример построения ПЗУМ на биполярных структурах показан на рис. 6.26, где приведена структурная схема БИС ПЗУ типа ТТЛШ КР554РЕ4 емкостью 16 К бит (2048×16). Выборка слов осуществляется 11-разрядным кодом, подаваемым на адресные входы А0–А10. Восемь выходных считывающих формирователей стробируются трехвходовым вентилем разрешения выборки. Информация проходит на выходные клеммы У1 –У8 только при коде 110 (младший разряд В1).

Масочные БИС ПЗУ выпускаются в основном на биполярных и МДП-структурах и предназначены для массового применения в качестве генераторов символов, преобразователей кодов и др.

В БИС ППЗУ информация, подлежащая хранению, заносится однократно после сборки кристалла в корпус электрическими сигналами путем пережигания перемычек, включенных последовательно с ЗЭ (рис. 6.25, б), либо пробоем р-n-перехода ЗЭ (рис. 6.25, в, г).Наибольшее распространение получило программирование пережиганием плавких перемычек из нихрома, поликристаллического кремния или алюминия (реже). В первых отечественных ИМС ППЗУ (КР556РТ4) в качестве ЗЭ использовались многоэмиттерные транзисторы, в цепи эмиттеров которых включались нихромовые перемычки. Разрабатываются БИС ППЗУ по технологии ЭСЛ, ТТЛ, ТТЛШ, И2Л, n-МДП.

На рис. 6.27 приведена структурная схема БИС ППЗУ типа ТТЛШ КР556РТ7 емкостью 16 К бит (2048×8). Матричный накопитель имеет организацию 128×128. ЗЭ состоит из диодов Шотки и нихромовой пережигаемой перемычки. До записи информации перемычки целые и во всем накопителе хранится информация «0». Программирование «1» осуществляется пережиганием нихромовых перемычек импульсом тока амплитудой 30–50 мА путем подачи электрических сигналов на внешние выводы БИС.

Характеристики БИС ЗУТаблица 6.4

| Тип (обозначение) | Функция | Информационная емкость, бит | Организация | Время выборки адреса, нс | Потребляемая мощность, мВт | Напряжение, В | Количество выводов | Схемотехника (технология) |

| К589РУ01 К155РУ7 К500РУ470 КР541РУЗ К505РУ6 К565РУ5Б К537РУ1А К155РЕ24 К596РЕ1 КР556РТ7 КР556РТ16 К500РТ416 К505РЕ3 К568РЕ1 К188РЕ1 КР1601РР3 К573РФ3 | ОЗУ ОЗУ ОЗУ ОЗУ ОЗУ ОЗУ ОЗУ ПЗУ ПЗУ ППЗУ ППЗУ ППЗУ ПЗУ ПЗУ ПЗУ РПЗУ РПЗУ | 16×4 1024×1 4096×1 16384×1 1024×1 65536×1 1024×1 256×4 8192×8 2048×8 8192×8 256×4 512×8 2048×8 1024×1 2048×8 4096×16 | -5,2 -5,2 5; -12 ±5; -12 5; -12 | ТТЛШ ТТЛ ЭСЛ И2Л-ТТЛ p-МДП n-МДП КМДП ТТЛ ТТЛ ТТЛШ ТТЛШ ЭСЛ p-МДП p-МДП КМДП МНОП ЛИЗ-МДП |

Рис. 6.27. Структурная схема БИС ППЗУ емкостью 16 К бит

(М – мультиплексор; Б – выходной буфер)

Типовые значения параметров некоторых отечественных БИС ОЗУ, ПЗУ, ППЗУ и РПЗУ приведены в табл. 6.4. Следует отметить, что БИС ПЗУ и ППЗУ на биполярных структурах обладают высоким быстродействием (tв.а.=15÷150 нс), имеет удельную потребляемую мощность P0=0,01÷0,8 мВт/бит и информационную емкость 1024–65536 бит.

Для БИС ПЗУ и ППЗУ на основе МДП-структур и их модификаций характерным является большая информационная емкость (256 К бит и более), при этом tв.а.=70÷4000 нс, а P0=0,01÷0,3 мВт/бит.

Большинство БИС РПЗУ имеет время выборки 50–1500 нс, информационную емкость 1–256 К бит и удельную потребляемую мощность менее 0,5 мВт/бит.

Дата добавления: 2015-08-26; просмотров: 2431;