ИМС запоминающих устройств

· Среди цифровых ИМС различного функционального назначения особое место занимают БИС запоминающих устройств (3У), предназначенные для приема, хранения и выдачи информации, представленной двоичным кодом.

В настоящее время разработана и серийно производится широкая номенклатура различных типов БИС ЗУ, определяемая выполняемыми ими функциями, структурой, схемотехникой построения и технологией изготовления.

Классификация и основные параметры. По выполняемым функциям, что обусловлено режимами работы, БИС ЗУ условно подразделяют на четыре класса: оперативные ЗУ, постоянные ЗУ (или ЗУ с преимущественным считыванием), ассоциативные ЗУ и ЗУ последовательного типа. Наибольшее распространение получили БИС оперативных и постоянных ЗУ.

Оперативные ЗУ (ОЗУ) осуществляют запись, хранение и считывание произвольной (переменной) двоичной информации с заданным быстродействием. БИС ОЗУ предназначены для построения основной памяти цифровых систем, в которой хранятся программы и массив данных, определяющие процесс текущей обработки информации. Отдельную группу в этом классе БИС составляют сверхоперативные ЗУ (СОЗУ), быстродействие которых соответствует скорости работы процессора системы.

Постоянные ЗУ (ПЗУ) служат для хранения информации, содержание которой не изменяется в процессе работы системы. БИС ПЗУ предназначены для хранения постоянных массивов информации: стандартных подпрограмм и микропрограмм, преобразователей кодов и, генераторов символов, констант, табличных значений различных функций и др. Применение БИС ПЗУ расширяет технические возможности ЭВМ, повышает их быстродействие и надежность, позволяет уменьшить количество необходимых БИС ОЗУ. В зависимости от способа занесения информации (программирования) различают три основные разновидности БИС ПЗУ: собственно ПЗУ с масочным программированием (ПЗУМ), электрически программируемые ПЗУ (ППЗУ) и репрограммируемые ПЗУ (РПЗУ).

БИС ЗУ (оперативных, постоянных, ассоциативных) состоят из накопителя информации и схем управления. Накопитель предназначен для хранения информации и представляет собой матрицу запоминающих элементов (ЗЭ), реализуемых на простейших логических схемах или отдельных транзисторах (иногда диодах).

В качестве схем управления в БИС ЗУ, применяют дешифраторы (ДШ), адресные формирователи, усилители считывания и записи, схемы синхронизации и местного управления. Состав схем управления зависит от типа БИС ЗУ; в них предусматривают также схемы, обеспечивающие согласование БИС ЗУ по логическим уровням с другими типами серийно выпускаемых ИМС.

По принципу построения накопителя информации БИС ЗУ строятся со словарной организацией (однокоординатной выборкой) или матричной организацией (двухкоординатной выборкой). Метод словарной организации выборки применим только в БИС с небольшим количеством ЗЭ, что обусловлено сложностью построения дешифратора с числом выходов, равным числу ЗЭ. Матричный метод предусматривает построение накопителя в виде квадратной матрицы из ЗЭ и использование двух дешифраторов для выбора столбца и строк.

По способу доступа к информации различают БИС ЗУ с произвольной и последовательной выборками. В БИС ЗУ с произвольной выборкой (ЗУПВ) в произвольный момент времени можно выполнить запись или считывание информации в любых ЗЭ. В БИС ЗУ с последовательной выборкой содержимое каждого ЗЭ может изменяться или выдаваться только через определенные интервалы времени, называемые периодом обращения (период обращения делится на отдельные такты, число которых равно количеству ЗЭ).

В зависимости от структуры БИС ЗУ организация выборки в них может быть одноразрядной (осуществляется выборка ЗЭ, хранящего один разряд информации) и словарной (одновременно выбирается слово или его часть, хранящанся в нескольких 3Э).

Для построения БИС ЗУ (накопителя и схем управления) используется различная элементная база: диоды, биполярные и МДП-транзисторы, а также простейшие логические элементы типа ТТЛ, ТТЛШ, ИЛ, ЭСЛ, МДПТЛ или КМДПТЛ, модифицированные применительно к ЗУ.

· Схемотехническое построение и элементная база БИС ЗУ определяют их основные характеристики: информационную емкость, быстродействие и потребляемую мощность.

Информационная емкость N – максимальный объем хранимой информации (бит, К бит), определяется числом ЗЭ в накопителе. При одинаковой емкости БИС ЗУ могут иметь различную организацию выборки (например для N =4096 – 4096×1, 1024×4, 512×8, 256×16).

Быстродействие БИС ЗУ характеризуется двумя основными параметрами: временем выборки адреса tв.а и временем цикла записи tц.зп (считывания tц.сч). Время tв.а – интевал времени между моментом подачи сигнала выборки и появлением информации на выходе БИС. Время цикла tц – интервал времени между началами (окончаниями) сигналов на одном из управляющих входов, в пределах которого БИС выполняет одну из функций: запись tц.зп, считывание tц.сч, запись – считывание tц.зп.сч считывание – запись tц.сч.зп. Поскольку значения tв.а и tц определяются элементной базой, используемой в накопителе и схемах управления, в ряде случаев в одной БИС для накопителя и схем управления используют различные типы элементов.

Потребляемая мощность Р,логические уровни, помехоустойчивость, нагрузочная способность и другие параметры БИС ЗУ аналогичны параметрам других типов цифровых ИМС. В отдельных случаях БИС ЗУ характеризуются удельной потребляемой мощностью Р0,т. е. мощностью, потребляемой БИС, отнесенной к ее информационной емкости, или током Iпот, потребляемым от источника питания.

Оперативные ЗУ. По принципу хранении информации в ЗЭ и способу управления ими все БИС ОЗУ подразделяются на статические, динамические, псевдостатические и квазистатические. В статических ОЗУ хранение информации в ЗЭ осуществляется постоянным источником питания. В динамических и псевдостатических ОЗУ информация хранится в ЗЭ в виде накопленных зарядов на паразитных емкостях диодов или транзисторов, а регенерация зарядов (восстановление информации) происходит периодически во время действия внешних (для псевдостатических ОЗУ) синхронизирующих сигналов. В квазистатических ОЗУ применяют статические ЗЭ и динамический способ управления периферийными схемами для снижения потребляемой мощности.

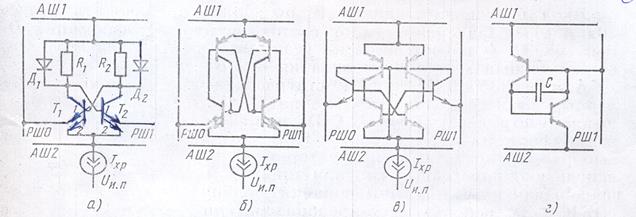

Разрабатывают БИС ОЗУ на биполярных и МДП-транзисторов и их модификаций. БИС ОЗУ на биполярных транзисторах представляют собой в основном статические ОЗУ. Они предназначены для применения в качестве регистров процессора, сверхоперативной и буферной памяти и характеризуются высоким быстродействием (tв.а=5÷50 нс). Для их построения используется схемотехника ТТЛ, ТТЛШ, ЭСЛ и И2Л. ЗЭ БИС статических ОЗУ обычно состоят из бистабильной ячейки, хранящей один заряд двоичной информации. Наибольшее применение получили биполярные ЗЭ на двухэмиттерных транзисторах, тиристорах и элементах И2Л. Схемы ЗЭ на биполярных транзисторах для БИС статических и динамических ОЗУ приведены на рис. 6.21. Типовая структура БИС статических ОЗУ состоит из матричного накопителя, дешифраторов, усилителей записи – считывания, буферных схем и схем управления.

В качестве примера на рис. 6.22 приведена структурная схема БИС быстродействующего статического ОЗУ К500РУ470 типа ЭСЛ емкостью 4К бит (4096×1). В данной БИС накопитель представляет собой матрицу 64×64, где симметричные статические ЗЭ (см. рис. 6.21, а) объединяются в строки по адресной шине АШ1 и адресной шиной АШ2, соединенной с общим источником тока хранения. По столбцам ЗЭ объединяются двумяразрядными шинами РШО и РШ1, к которым подключаются первые эмиттеры двухэмиттерных транзисторов. По этим шинам производится дифференциально запись или считывание информации. В режиме хранения на шине АШ1 пониженный потенциал, переходы транзисторов база – эмиттер 1 закрыты и триггер образован на транзисторах с эмиттерами 2, в одном из которых проходит ток хранения. При выборке строки повышается потенциал на шине АШ1 и через переход база – эмиттер 1 открытого транзистора проходит ток считывания. Необходимое значение тока считывания обеспечивают генераторы тока, подключенные к шинам РШ. Вход выбора микросхемы CS (рис 6.22) обеспечивает нужный режим выборки (считывания) или хранения (записи) информации. Выборка информации осуществляется при подаче соответствующих адресных сигналов на дешифраторы ДШХ и ДШУ, в результате адресный дешифратор ДШХ выдает сигнал выборки в адресную шину, а разрядный дешифратор ДШУ – в разрядную шину и включает соответствующие усилители записи – считывания.

Рис. 6.21. Схемы ЗЭ БИС ОЗУ на биполярных транзисторах:

Дата добавления: 2015-08-26; просмотров: 3595;