СХЕМИ НАНОЕЛЕКТРОНІКИ НА КОМПЛЕМЕНТАРНИХ ТРАНЗИСТОРАХ

Вимоги зменшення потужності, часових меж перезарядки ємностей та балістичного руху носіїв заряду призвели до створення наноелектронних схем на комплементарних транзисторах. Комплементарні одноелектронні (КОЕТ на рис. 3.7) та короткоканальні (≤50 нм) зі структурою метал-оксид-напівпровідник (КМОНТ) транзистори відповідають цим вимогам. В цих схемах комплементарні транзистори завжди використовуються парами.

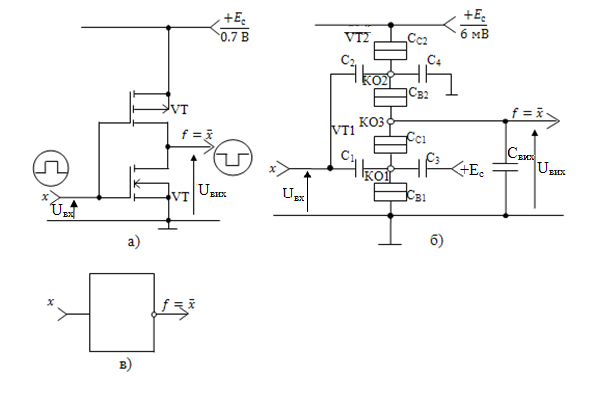

На рис. 4.1 наведені схеми інверторів, що виконують операцію логічного заперечення НІ на базі КМОНТ(а) та КОЕТ(б).

Рис. 4.1. Схеми логічних інверторів на базі КМОНТ(а), КОЕТ(б) та їх умовне позначення(в)

При нульовому сигналі на вході  в схемі на рис. 4.1, а відкривається р-КМОНТ VT2 і з'єднує вихід схеми

в схемі на рис. 4.1, а відкривається р-КМОНТ VT2 і з'єднує вихід схеми  з джерелом живлення, формуючи на виході сигнал логічної одиниці

з джерелом живлення, формуючи на виході сигнал логічної одиниці  . Навпаки, при вхідному сигналі

. Навпаки, при вхідному сигналі  , вихідний дорівнює

, вихідний дорівнює

.

.

Час перемикання КМОНТ:

tпер=Lк/V, (4.1)

де 10нм ≤ Lк ≤ 100нм– довжина каналу і V=106м/с – швидкість балістичного руху носіїв зарядів. Тобто, tпер~ 1пс дляLк ~ 100 нм.

Залежність дисипативної потужності, яку розсіює КМОНТ в динамічному режимі, від довжини каналу Pд ~ ≤ Lк2,7 , а частоти перемикання fпер ~ ≤ Lк 1,5.

В схемі з КОЕТ (рис. 4.1, б) при  транзистор VT1 закритий умовами кулонівської блокади острівців КО1 та КО3 і на виході

транзистор VT1 закритий умовами кулонівської блокади острівців КО1 та КО3 і на виході  . Якщо на вході діє

. Якщо на вході діє  , то знімається блокада з усіх кулонівських острівців, транзистор VT1 відкривається і

, то знімається блокада з усіх кулонівських острівців, транзистор VT1 відкривається і  . Для визначення параметрів схеми розраховують та будують характеристики кулонівських доменів стабільної роботи в координатах

. Для визначення параметрів схеми розраховують та будують характеристики кулонівських доменів стабільної роботи в координатах  . Для кожного з доменів знаходять потенціали 0 або 6 мВ для трьох острівців (КО1, КО2, КО3) у формі (0,0,0); (0,0, 6мВ); (0,6мВ,0); (0,6мВ,6мВ); (6мВ,0,0); (6мВ,0,6мВ); (6мВ,6мВ,0) та (6мВ,6мВ,6мВ).

. Для кожного з доменів знаходять потенціали 0 або 6 мВ для трьох острівців (КО1, КО2, КО3) у формі (0,0,0); (0,0, 6мВ); (0,6мВ,0); (0,6мВ,6мВ); (6мВ,0,0); (6мВ,0,6мВ); (6мВ,6мВ,0) та (6мВ,6мВ,6мВ).

Для переходу зі стану (6мВ,6мВ,0) до (6мВ,0,0), який є умовою перемикання інвертора на КОЕТ вхідним сигналом одиниці  , знаходять ємнісні параметри за рівняннями, аналогічними (3.12):

, знаходять ємнісні параметри за рівняннями, аналогічними (3.12):

,

,  ,

,  і

і  .

.

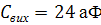

Наступні схеми на комплементарних приладах 2I-HI приведені на рис.4.2.

Рис. 4.2 Логічні елементи 2I-HI на базі КМОНТ(а), КОЕТ(б) та їх умовне позначення (в)

Тільки при подачі сигналів  р-канальні МОНТ VT3 і VT4 вимикаються, а транзистори VT1 і VT2 вмикаються і з’єднують вихід схеми з нульовим потенціалом, тому

р-канальні МОНТ VT3 і VT4 вимикаються, а транзистори VT1 і VT2 вмикаються і з’єднують вихід схеми з нульовим потенціалом, тому  .

.

За подібною схемою будуються елементи 2І-НІ на КОЕТ (рис. 4.2,б). Два нижні, послідовно з’єднані прилади накопичують («накачують») електрони на двох кулонівських острівцях КО1 та КО2, тобто реалізують логічну операцію множення 2І. Два верхні паралельно з’єднані транзистори розсмоктують («виштовхують») електрони до джерела живлення +Ес, в кінцевому рахунку, реалізуючи операцію логічного заперечення НІ. Конденсатори останньої схеми мають ємності: Cв1=С в2=С в3=С в4=1аФ, Сс1= Сс2= Сс3= Сс4=2аФ, С1= С2=3аФ, С3=С4=5аФ, С5= С6=7,7аФ, С7= С8= 7,4аФ, Свих=240аФ та опори усіх тунельних переходів  .

.

До вихідного конденсатора навантаження усієї схеми  висувають особливі вимоги: його ємність повинна суттєво (на два порядки) перевищувати середні значення ємностей тунельних переходів Св та Сс, , а добуток СвихЕс повинен бути кратним числовому значенню заряда електрона:

висувають особливі вимоги: його ємність повинна суттєво (на два порядки) перевищувати середні значення ємностей тунельних переходів Св та Сс, , а добуток СвихЕс повинен бути кратним числовому значенню заряда електрона:  , тому для n=10, Cвих=240аФі Е = +6,67мВ.

, тому для n=10, Cвих=240аФі Е = +6,67мВ.

Якщо для виконання логічної функції 2І-НІ n-канальні МОПТ

вмикають послідовно, то парні їм транзистори з  -каналами – паралельно. Тому для створення елементів 2АБО-НІ схеми їх вмикання міняють місцями (рис.4.3, а).

-каналами – паралельно. Тому для створення елементів 2АБО-НІ схеми їх вмикання міняють місцями (рис.4.3, а).

Рис. 4.3. Логічні елементи 2АБО-НІ на КМОНТ (а), КОЕТ (б) та їх

умовне позначення (в)

Аналогічно діють для реалізації схеми 2АБО-НІ на КОЕТ (рис.4.3, б).

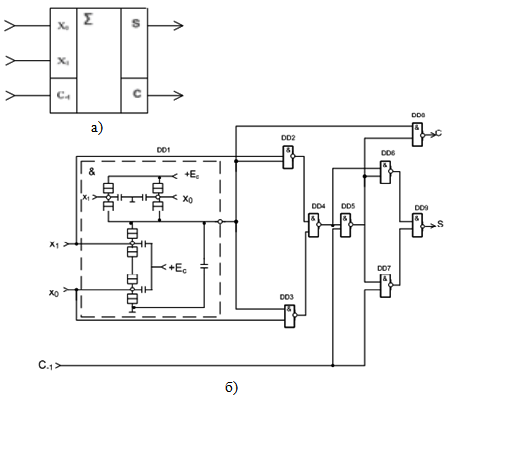

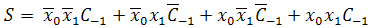

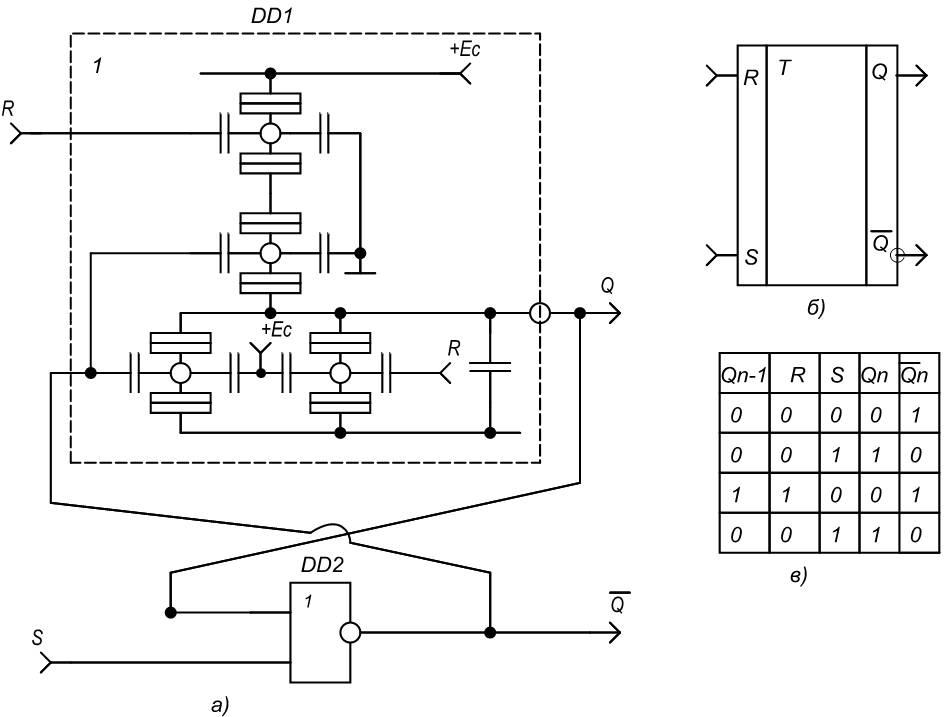

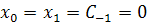

Однорозрядний суматор (рис. 4.4), що має два входи доданків х0 та х1 і один вхід переносу з молодшого розряду С-1 та по одному виходу суми S і переносу до старшого розряду С, будують на 9 одноелектронних комплементарних (рис. 4.2, б) однорідних елементах 2І – НІ DD1 – DD9 (рис.4.4, б) замість 12 різнорідних (рис. 3.15, а; 3.16, а та 3.17, а).

Рис. 4.4. Однорозрядний суматор (а) та його наносхема на базі

КОЕТ 2І – НІ (б)

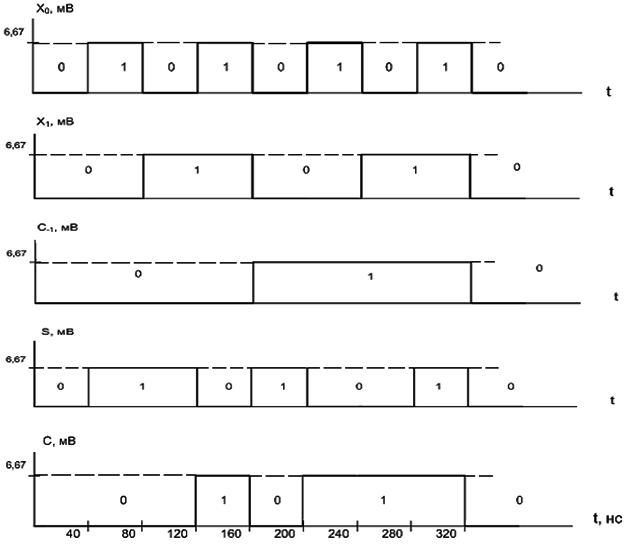

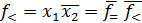

Логічні рівняння, що описують результат додавання в цій наносхемі, мають вигляд:

, (4.3)

, (4.3)

. (4.4)

. (4.4)

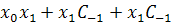

На рис. 4.5 наведені часові осцилограми моделювання за допомогою програми НSрісе роботи однорозрядного суматора на КОЕТ.

Рис.4.5. Часові діаграми роботи однорозрядного суматора на схемах з комплементарними одноелектронними транзисторами

Середній час виконання операції додавання ( рис. 4.5) складає не більше 10 нс.

При розробці складних логічних пристроїв часто стикаються з проблемою послідовного виконання однотипних операцій І-АБО-НІ над різним числом аргументів. Для спрощення технічної реалізації та зменшення кількості зовнішніх з'єднань між корпусами мікросхем, що в свою чергу, підвищує надійність пристроїв, випускають серійні ІС, які виконують ці набори операцій. На основі нанорозмірних КМОНТ створюють ІС, яка здійснює складну логічну операцію 2-2І-2АБО-НІ (рис. 4.6, а) і підтверджує справедливість принципів подвійності де-Моргана:

Рис. 4.6. Логічна схема 2-2І-2АБО-НІ (а), її позначення (б) і таблиця дійсності (в)

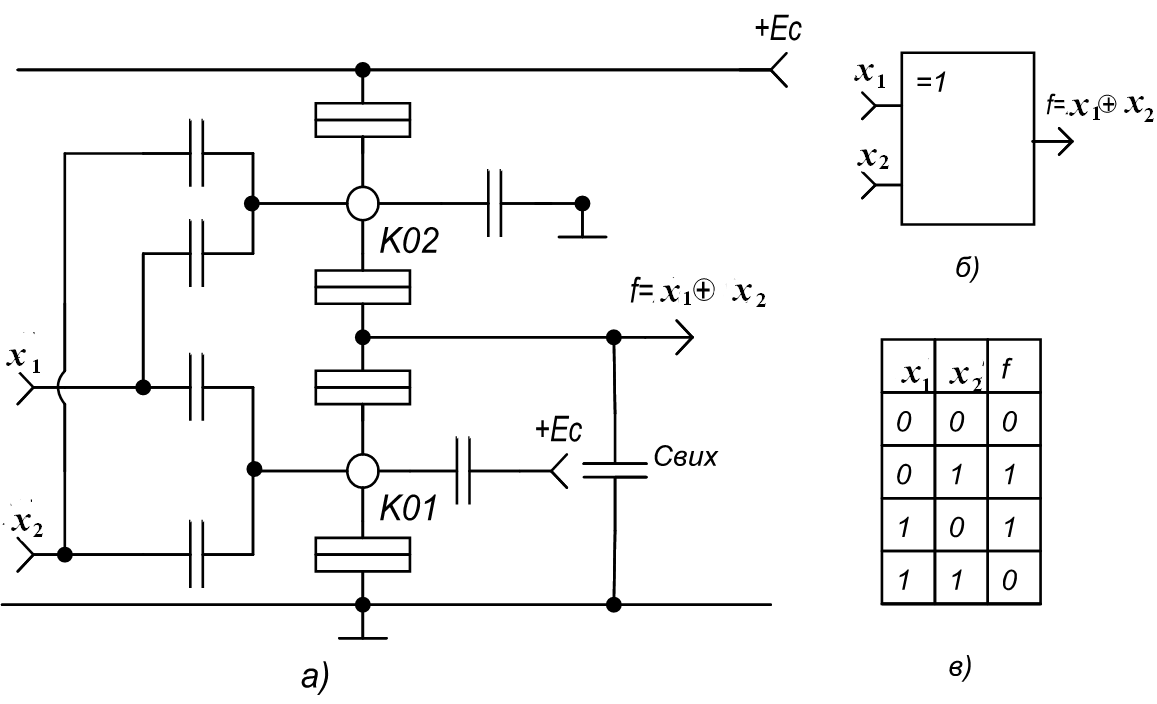

На одній парі КОЕТ створено логічний елемент Виключне АБО (рис.4.7, а).

Рис. 4.7. Логічний наноелемент Виключне АБО на КОЕТ (а), умовне

позначення (б) та таблиця дійсності (в)

Якщо x1=x2=0, то на кулонівських острівцях К01 і К02 не накопичуються електрони і на виході f=x1+x2=0. Коли хоча б на одному острівці буде знята кулонівська блокада через подачу сигналу x1 або x2 , що дорівнює 1, то на виході f=1. При x1=x2=1 обидва КОЕТ відкриті, протікає струм виток - сток і напруга на виході дорівнює нулю f=0.

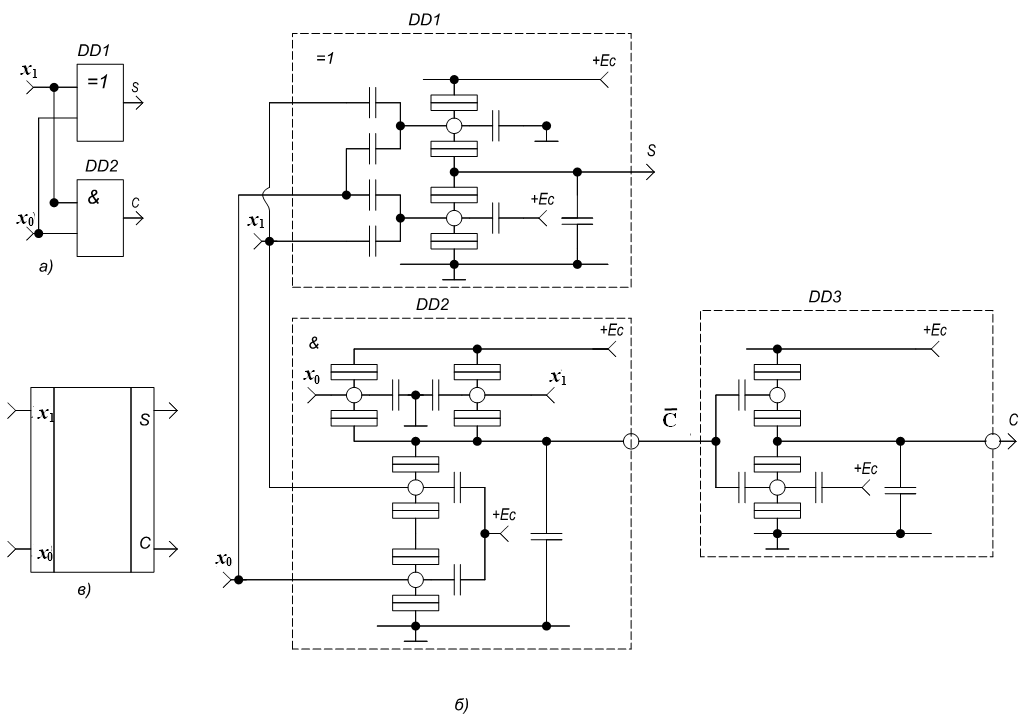

Якщо використати схему Виключне АБО на КОЕТ для побудови півсуматора, то вдається скоротити кількість логічних елементів з шести одноелектронних (рис. 3.15, а та 3.16, а) до трьох, як показано на рис 4.8.

|

| ∑ |

Рис. 4.8. Логічна (а), електрична (б) наносхеми півсуматора та його умовне позначення (в)

Логічні дії півсуматора описуються наступними рівняннями :

, (4.6)

, (4.6)

. (4.7)

. (4.7)

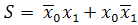

Функцію запам’ятовування логічних станів в цифрових послідовностних схемах виконують тригери. Найпростішим є RS-тригер, який може бути

сформовано на двох паралельно з’єднаних схемах 2 АБО-НІ DD1 та DD2 з комплементарною елементною базою. На рис. 4.9, а для цього вибрані КОЕТ (рис.4.3, б)

Рис. 4.9. Наносхема RS-тригера на комплементарних одноелектронних транзисторах (а), його умовне позначення (б) та таблиця станів входів й виходів

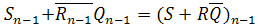

Функціонування RS-тригера визначається рівняннями :

=

=  , (4.8)

, (4.8)

. (4.9)

. (4.9)

Отже тригери, виконуючи функцію пам’яті, використовуються в схемах лічильників, запам’ятовуючих пристроїв, регістрів, тощо.

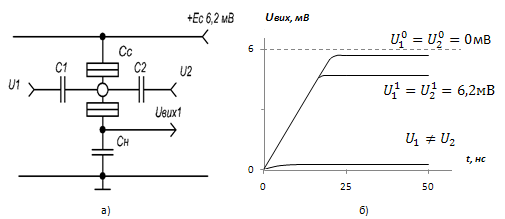

На базі двозатворного одноелектронного транзистора (рис. 3.7) створено наносхему бінарного компаратора, яка наведена на рис 4.10, а.

Рис. 4.10. Одноелектронна насхема числового компаратора (а) і його часові характеристики (б)

При обох високих (  ) або низьких

) або низьких  вхідних напругах ОЕТ відкритий. Електрони тунелюють через переходи СВ та СС і заряджають конденсатор навантаження СН приблизно до

вхідних напругах ОЕТ відкритий. Електрони тунелюють через переходи СВ та СС і заряджають конденсатор навантаження СН приблизно до

.

.

У ситуації, коли  ,

,  чи

чи  ,

,  , тобто,

, тобто,  конденсатор практично повністю розряджений і

конденсатор практично повністю розряджений і  . Ця схема виконує операції перевірки рівнозначності (еквівалентності) і за принципом дії схожа на логічну схему Виключне АБО (рис. 4.7), але із запереченням. Проте одноелектронний компаратор чисел не можна вважати логічним елементом, оскільки він не запам’ятовує вихідний електричний стан після виконання операції порівняння, а його вихідна напруга менша за вхідні

. Ця схема виконує операції перевірки рівнозначності (еквівалентності) і за принципом дії схожа на логічну схему Виключне АБО (рис. 4.7), але із запереченням. Проте одноелектронний компаратор чисел не можна вважати логічним елементом, оскільки він не запам’ятовує вихідний електричний стан після виконання операції порівняння, а його вихідна напруга менша за вхідні  .

.

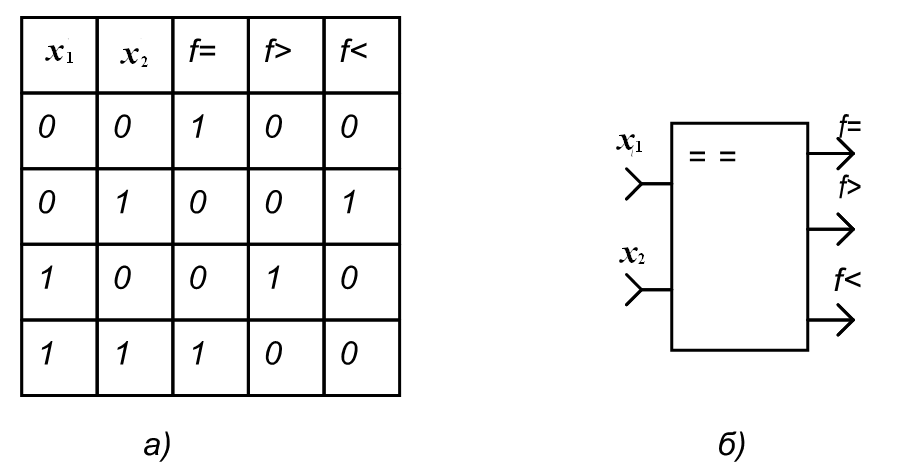

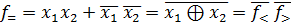

На виході компаратора зазвичай формуються три сигнали : f= – рівності кодів, f> та f<, якщо перше число більше чи менше за друге. Таблиця дійсності для однорозрядного компаратора наведена на рис. 4.11, а.

Рис.4.11. Таблиця дійсності (а) та умовне позначення (б) схеми однорозрядного порівняння

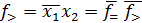

Цій таблиці дійсності відповідають система логічних рівнянь :

, (4.10)

, (4.10)

, (4.11)

, (4.11)

, (4.12)

, (4.12)

де функція (4.10) має назву Виключне АБО-НІ.

Аналіз таблиці (рис.4.1, а) та системи рівнянь (4.10) - (4.12) показує, що за будь-якої комбінації вхідних сигналів на виходах компаратора формується один активний сигнал логічної одиниці. Тому для довільної розрядності вхідних кодів достатньо сформувати довільні два вихідні сигнали. Третій завжди можна отримати по двом відомим.

На базі однорозрядних створюють багаторівневі і багаторозрядні компаратори слів і образів. Наприклад, їх використовують у асоціативних нейронних мережах у якості детектора дикторів, тобто, для інтелектуальної обробки інформації.

Контрольні завдання до глави 4

4.1. Розрахувати час та частоту перемикання КМОН-транзисторів [рис. 4.1 та формула (4.1)] з довжиною каналу Lк=100 нм, 10 нм і 1 нм.

4.2. Побудувати імпульсні діаграми роботи інверторів на КМОНТ (рис. 4.1,а) та КОЕТ (рис 4.1,б).

4.3. Побудувати таблиці дійсності одноелектронних компле-ментарних елементів 2І-НІ (рис. 4.2, б) та 2АБО-НІ (рис. 4.3, б).

4.4. Розрахувати напругу живлення елемента 2І-НІ на КОЕТ (рис.4.2, б), якщо вихідна ємність Свих=200 аФ, а кількість накопичених електронів на кулонівському острівці n=5 [див. ф-лу (4.2)].

4.5. Довести, що схема однорозрядного суматора на КОЕТ (рис. 4.4,а) описується логічним рівнянням для суми (4.3) та для переносу в старший розряд (4.4).

4.6. Створити однорозрядний суматор на логічній схемі Виключне АБО на КОЕТ (рис.4.7,а та рис.3.16, а).

4.7. Навести таблиці дійсності для елемента 2І-НІ на базі КМОНТ (рис.4.2, б).

4.8. Навести таблиці дійсності для елемента 2АБО-НІ на базі КМОНТ (рис4.3, а).

4.9. Побудувати часові діаграми однорозрядного суматора (рис.4.4 та 4.5), якщо С-1=0 на періоді часу від 40 нс до 320 нс.

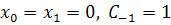

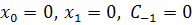

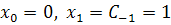

Побудувати часові діаграми однорозрядного суматора (рис. 4.4. та 4.5) за варіантами:

4.10. Період часу (0 – 40 )нс,  .

.

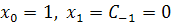

4.11. Період часу (40 – 80 )нс,  .

.

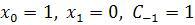

4.12. Період часу (80 – 120 )нс,  .

.

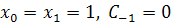

4.13. Період часу (120 – 160 )нс,  .

.

4.14. Період часу (160 – 200 )нс,  .

.

4.15. Період часу (200 – 240 )нс,  .

.

4.16. Період часу (240 –280 )нс,  .

.

4.17. Період часу (280 – 320 )нс,  .

.

4.18. Період часу (0 – 160 )нс,  .

.

4.19. Період часу (160 – 320 )нс,  .

.

4.20. Заповнити таблицю дійсності для подвійного інвертора 2-2І-2АБО-НІ (рис.4.6, а, в).

4.21. Реалізувати логічну функцію двох аргументів Виключне АБО (  ) на базі подвійного інвертора (рис.4.6, а) з урахуванням теореми подвійності (4.5) і пояснити принцип дії схеми.

) на базі подвійного інвертора (рис.4.6, а) з урахуванням теореми подвійності (4.5) і пояснити принцип дії схеми.

4.22. Реалізувати логічну функцію двох аргументів Виключне АБО-НІ  на базі подвійного інвертора (рис.4.6, а) з урахуванням теореми подвійності (4.5) і пояснити принцип дії схеми.

на базі подвійного інвертора (рис.4.6, а) з урахуванням теореми подвійності (4.5) і пояснити принцип дії схеми.

4.23. Реалізувати логічну функцію множення із запереченням двох аргументів  на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

4.24. Реалізувати логічну функцію додавання із запереченням двох аргументів (  ) на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

) на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

4.25. Реалізувати логічну функцію трьох аргументів  на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

4.26. Реалізувати логічну функцію трьох аргументів  на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

на базі подвійного інвертора (рис.4.6, а) і пояснити принцип дії схеми.

4.27. На базі КОЕТ-елемента Виключне АБО (рис.4.7, а) побудувати елемент, який реалізує функцію Виключне АБО-НІ  .

.

4.28. Створити схему RS-тригера (рис.4.9, б) на базі елементів 2І-НІ.

4.29. Побудувати повну таблицю дійсності для однорозрядного суматора (рис.4.4, а), використавши рівняння (4.3) та (4.4).

4.30. Побудувати наносхему на КОЕТ для реалізації функцій однорозрядного порівняння (4.10), (4.11) та (4.12).

Дата добавления: 2016-11-02; просмотров: 1340;