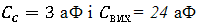

СХЕМОТЕХНІКА ОДНОЕЛЕКТРОНІКИ

В одноелектронних приладах контролюється переміщення малої кількості носіїв заряду, навіть одного електрона. В цифровій одноелектроніці один біт інформації подається одним електроном. В таких схемах електрони переміщуються за рахунок тунелювання крізь потенційні бар’єри. Тунельний перехід формується з двох металічних або напівпровідникових тонких (1…100нм) шарів, розділених діелектриком товщиною ~5нм.

3.1. Параметри одноелектронних переходів

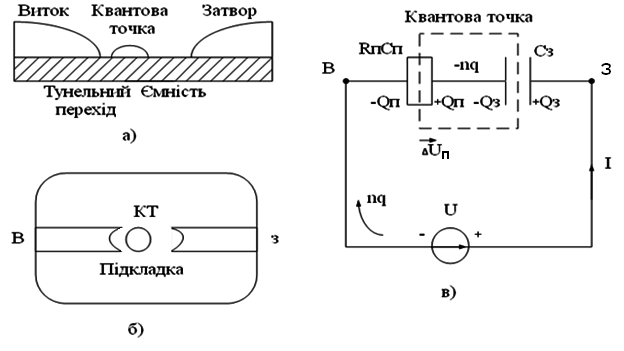

Одноелектронний прилад створюють на поверхні напівпровідникової або діелектричної підкладки (рис. 3.1 а, б).

Рис 3.1. Одноелектронний прилад з тунельним переходом (а, б) та його електрична схема (в)

Він має два металевих електроди витоку та затвору. Ближче до витоку розміщена квантова точка, яка часто зветься кулонівським острівцем. Між витоком та острівцем можуть практично безінерційно тунелювати одиночні електрони в обидва боки. На більш віддалений керуючий затвор електрони не тунелюють. Так електрони інжектуються з витоку на квантову точку і там накопичуються при позитивній напрузі на затворі. При зменшенні або зміні знаку напруги на затворі електрони ежектуються з квантової точки до витоку. При цьому змінюється напруга на ємності переходу:

, (3.1)

, (3.1)

де q=1,6*10-19 Кл – заряд електрона.

В результаті перескоку з провідника на провідник електрони накопичуються на кулонівському острівці і створюють на тунельному переході напругу  , яка перешкоджає рухові наступних зарядів. Цей ефект зветься кулонівською блокадою.

, яка перешкоджає рухові наступних зарядів. Цей ефект зветься кулонівською блокадою.

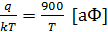

Згідно з умовами електростатики та квантування заряду наступний електрон подолає кулонівську блокаду при напрузі:

, (3.2)

, (3.2)

а наступні n електронів при :

(3.3)

(3.3)

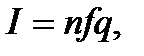

Частота одноелектронних коливань струму I в схемі дорівнює:

. (3.4)

. (3.4)

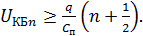

На рис.3.2 наведена залежність кількості накопичених на кулонівському острівці електронів n від напруги, що має назву кулонівських сходів.

Рис. 3.2. Залежність накопичених електронів від напруги

Початковий заряд на тунельному переході може відрізнятись від нуля та, навіть, приймати дробове число заряду електрона. Це пояснюється явищем поляризації сусідніх зарядових домішок, електродів тощо. Між сусідніми сходами опір переходу різко зменшується і один електрон тунелює крізь бар’єр. Плато сходів відповідає часовій фіксації цілого числа електронів у провіднику, що означає кулонівську блокаду. У середній частині сходів число електронів з рівною ймовірністю складає n чи (n+1), тому блокада знімається і тунелювання продовжується.

Згідно з умовами завадостійкості енергія електронів  повинна значно перевищувати термодинамічні флуктації (шуми) :

повинна значно перевищувати термодинамічні флуктації (шуми) :

>> kT, (3.5)

>> kT, (3.5)

де k=1,38 10-23 Дж К-1 – стала Больцмана і T – абсолютна температура.

Тому стійко функціонуючі одноелектронні прилади на сьогоднішній день існують лише при температурах від 1 мК до температури кипіння рідинного гелію 4,2 К.

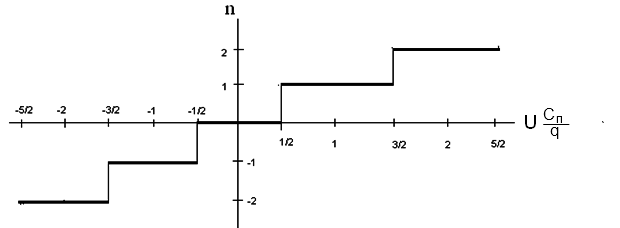

Об’єднуючи рівняння (3.1) та (3.5), знаходимо:

<<

<<  , (3.6)

, (3.6)

тобто з запасом на 1 порядок для Т=4,2 К маємо СП  , а для кімнатної температури Т = 300 К – СП = 0,3 аФ. Таким чином, кулонівська блокада існує для ємностей тунельних переходів, які на 6 порядків менші ніж ємності реальних мікросхем (

, а для кімнатної температури Т = 300 К – СП = 0,3 аФ. Таким чином, кулонівська блокада існує для ємностей тунельних переходів, які на 6 порядків менші ніж ємності реальних мікросхем (  1пФ).

1пФ).

Ємність кулеподібного кулонівського острівця:

,

,

де  =8,86 10-12 Ф м-1 – діелектричні проникності діелектрика та вакууму, тобто:

=8,86 10-12 Ф м-1 – діелектричні проникності діелектрика та вакууму, тобто:

. (3.7)

. (3.7)

Отже, для забезпечення умов кулонівської блокади при температурах 4,2 К та при кімнатній радіус кулонівського острівця не повинен перевищувати 70 нм та 1 нм, відповідно.

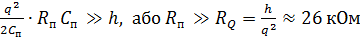

Визначеність заряду конденсатора означає, що слід нехтувати малими квантовими флуктуаціями, пов’язаними з переходом електрона крізь тунельний бар’єр з опором  та ємністю

та ємністю  . Вочевидь, співвідношення Гейзенберга для невизначеності зарядової енергії

. Вочевидь, співвідношення Гейзенберга для невизначеності зарядової енергії  та сталої часу

та сталої часу  повинно виконуватись з великим запасом:

повинно виконуватись з великим запасом:

, (3.8)

, (3.8)

де  = 6,63 10-34 Дж с – стала Планка та

= 6,63 10-34 Дж с – стала Планка та  – квантований опір.

– квантований опір.

Таким чином, для спостереження квантоворозмірних ефектів тунелювання та кулонівської блокади одноелектронні пристрої повинні мати розміри у декілька одиниць або десятків нанометрів, ємності – одиниці та десяті долі аттофарад, опори – сотні кілоомів, і функціонувати при температурах, близьких до абсолютного нуля.

3.2. Одноелектронні транзистори

Одноелектронні транзистори (ОЕТ) звичайно виготовляють, як і багато МОН-транзисторних структур, за технологією «кремній на ізоляторі (сапфірі)».

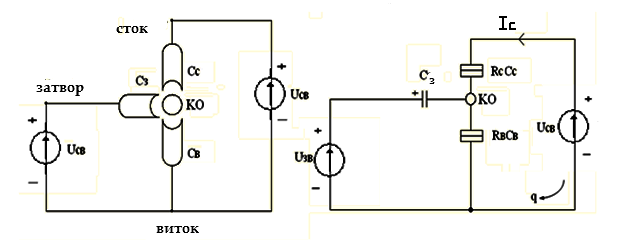

а) б)

Рис.3.3. Одноелектронний транзистор (а) та його еквівалентна схема(б)

Контакти витоку, стоку та затвору, а також нанорозмірний кулонівський острівець (КО на рис.3.3, а) промальовують за допомогою еліонної літографії. Потім за допомогою селективної іонної імплантації створюють потенційні бар’єри до КО, тобто регулюють величини ємностей тунельних переходів витоку та стоку . Через звичайний конденсатор затвору  стає можливим польове керування накопиченням електронів на КО, які тунелюють через переходи витоку

стає можливим польове керування накопиченням електронів на КО, які тунелюють через переходи витоку  та стоку

та стоку  .

.

Випадкові флуктуації реального зарядового оточення у вигляді поверхневих станів або неконтрольованих пасток можуть впливати на КО транзистора навіть суттєвіше ніж напруга на затворі  . Це найсерйозніша проблема керування ефектом кулонівської блокади в ОЕТ.

. Це найсерйозніша проблема керування ефектом кулонівської блокади в ОЕТ.

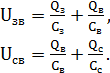

Для вхідного та вихідного контурів еквівалентної схеми транзистора (рис.3.3, б) справедлива наступна система рівнянь:

(3.9)

(3.9)

Запасена електрична енергія цієї структури дорівнює:

Е =  , (3.10)

, (3.10)

де

, та

, та  – заряди відповідних конденсаторів ОЕТ,

– заряди відповідних конденсаторів ОЕТ,  та

та  – напруги сток-виток та затвор-виток.

– напруги сток-виток та затвор-виток.

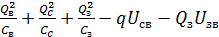

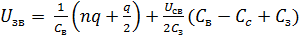

Після перетворень рівнянь (3.9) та (3.10), отримуємо залежність двох напруг ОЕТ при тунелюванні n електронів на КО через переходи витоку та стоку:

, (3.11)

, (3.11)

тобто для подолання порогової напруги кулонівської блокади (3.3) та переходу електронів з КО на один з контактів слід, щоб виконувались умови:

. (3.12)

. (3.12)

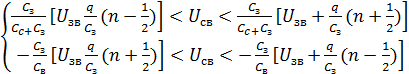

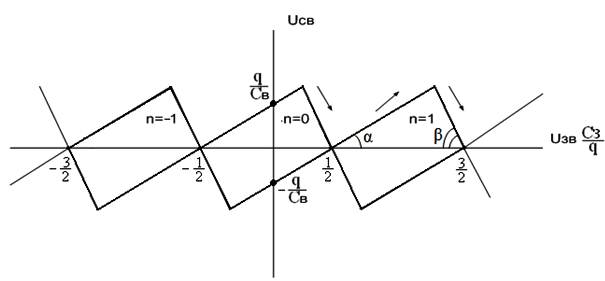

З урахуванням нерівностей (3.12) на рис.3.4 побудований графік з ромбоподібними фігурами, що обмежують області стабільної роботи транзистора. У ціх областях (доменах) виконуються умови кулонівської блокади. Після зміни керуючої напруги на затворі КО поповнюється одним електроном (n+1) або втрачає його (n-1). Отже, керуюча польова дія затвору практично така сама, як і у польового МОН-транзистора.

Рис.3.4. Польові характеристики ОЕТ з кулонівськими ромбами

Рис.3.4. Польові характеристики ОЕТ з кулонівськими ромбами

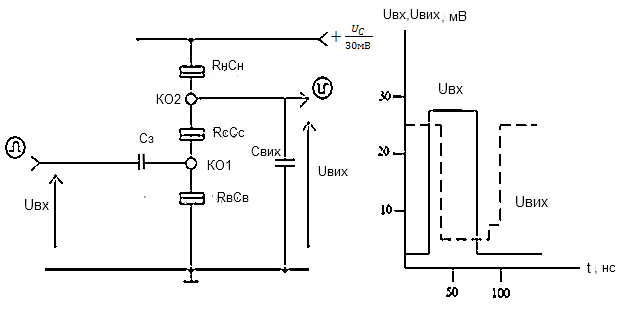

Коли, наприклад, напруга на затворі змінюється від  до

до  і один електрон (n=1) долає кулонівську блокаду на КО, то кути нахилу ліній перемикання ОЕТ, що відмічені стрілками на рис.3.4, складають:

і один електрон (n=1) долає кулонівську блокаду на КО, то кути нахилу ліній перемикання ОЕТ, що відмічені стрілками на рис.3.4, складають:

При проектуванні цифрових одноелектронних схем обов’язково розраховують та будують багатомірні порогові характеристики кулонівських доменів стабільної роботи схеми в цілому. Цей етап є найвідповідальнішим при розрахунку ємностей та нанорозмірних параметрів транзисторних елементів схеми.

Якщо ОЕТ використовувати у якості інвертора, що виконує операцію логічного заперечення НІ, то при значенні вхідної напруги на затворі, що відповідає логічному нулю, ефект кулонівської блокади закриває транзистор. На виході (стоці) встановлюється висока напруга логічної одиниці. При зростанні вхідної напруги до рівня логічної одиниці кулонівська блокада знімається, через переходи тунелюють електрони, зростає струм виток-сток, вихідна напруга зменшується та встановлюється логічний нуль на виході.

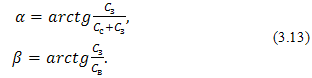

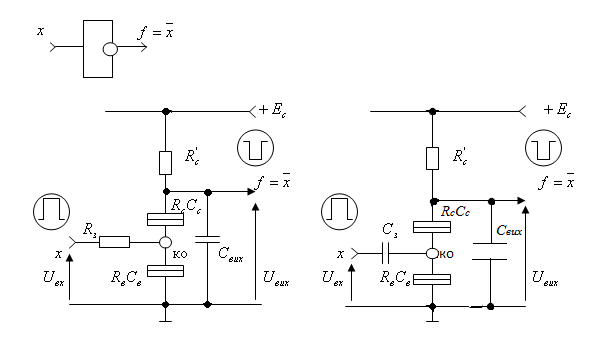

Одна з можливих схем одноелектронного логічного інвертора з навантаженням у вигляді туннельного перехода  та вихідного конденсатора

та вихідного конденсатора  наведена на рис.3.5, а.

наведена на рис.3.5, а.

а) б)

Рис.3.5. Одноелектронний інвертор(а) та діаграми його перемикання(б)

Внутрішній стан схеми залежить від кількості електронів на кулонівських острівцях КО1 та КО2. Карта доменів стабільності цієї схеми має складну тривимірну шарувату структуру, за якою знаходять величини параметрів елементів:  ,

,

. Кожен домен відповідає зарядовому стану острівців КО1 та КО2: (0,0); (0,q); (q,0); (q,q). Вочевидь, переходи між станами (q,0)

. Кожен домен відповідає зарядовому стану острівців КО1 та КО2: (0,0); (0,q); (q,0); (q,q). Вочевидь, переходи між станами (q,0)  (0,0) є умовами перемикання інвертора. Імпульсні часові характеристики перемикання схеми показані на рис.3.5, б.

(0,0) є умовами перемикання інвертора. Імпульсні часові характеристики перемикання схеми показані на рис.3.5, б.

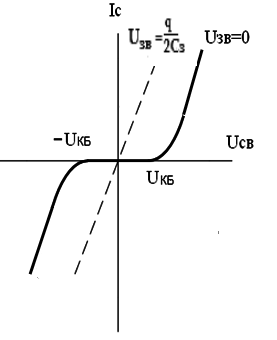

Повертаючись до рис.3.4, бачимо, що при послідовній зміні затворної напруги  періодично виникає кулонівська блокада, тому ця залежність струму через КО буде мати характер наноамперної осциляції. Слід підкреслити, що струм при цьому змінюється практично безперервно і пропорційно напрузі на затворі та на стоці. На рис.3.6 показана вольт-амперна характеристика (ВАХ) ОЕТ.

періодично виникає кулонівська блокада, тому ця залежність струму через КО буде мати характер наноамперної осциляції. Слід підкреслити, що струм при цьому змінюється практично безперервно і пропорційно напрузі на затворі та на стоці. На рис.3.6 показана вольт-амперна характеристика (ВАХ) ОЕТ.

Рис.3.6. ВАХ одноелектронного транзистора

Отже, ОЕТ являє собою пороговий елемент при  = 0, струм якого залежить від напруги кулонівської блокади

= 0, струм якого залежить від напруги кулонівської блокади  =

=

. При подоланні блокади

. При подоланні блокади  струм виток-сток зростає за приблизним законом

струм виток-сток зростає за приблизним законом  . Кулонівська блокада, звісно, може бути усунена за рахунок збільшення напруги на затворі

. Кулонівська блокада, звісно, може бути усунена за рахунок збільшення напруги на затворі  (переривиста лінія).

(переривиста лінія).

ОЕТ має два стани: кулонівської блокади або тунельної провідності. Це дає змагу створювати на його основі логічні наноелектронні пристрої.

По аналогії з КМОН-структурами створені комплементарні пари ОЕТ (КОЕТ), у яких виток, сток та затвор виготовляють із кремнію Sipдля діркового та Sin для електронного типів транзисторів відповідно.

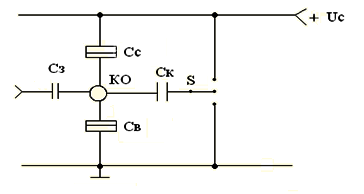

Окрім цього, створені КОЕТ з додатковими керуючими затворами (рис.3.7).

Рис.3.7. Комплементарне керування ОЕТ

Для КОЕТ, що виконує логічні операції (як n-канальний КМОН-транзистор), на додатковий керуючий затвор за допомогою перемикача S через конденсатор  подають високий потенціал живлення +

подають високий потенціал живлення +  , що зменшує порогову напругу зняття кулонівської блокади з КО. Для КОЕТ, що зєднує високий потенціал +

, що зменшує порогову напругу зняття кулонівської блокади з КО. Для КОЕТ, що зєднує високий потенціал +  з виходом схеми (як p-канальний КМОН-транзистор), другий затвор підключають до нульового потенціалу і, таким чином, в цьому випадку КОЕТ керується виключно вхідними сигналами першого затвору.

з виходом схеми (як p-канальний КМОН-транзистор), другий затвор підключають до нульового потенціалу і, таким чином, в цьому випадку КОЕТ керується виключно вхідними сигналами першого затвору.

Комплементарним режимам роботи відповідають кулонівські домени на рис.3.4, а саме позитивна напруга на затворі  керує блокадою негативно заряджених електронів, і негативна

керує блокадою негативно заряджених електронів, і негативна

– позитивно заряджених носіїв заряду (дірок).

– позитивно заряджених носіїв заряду (дірок).

3.3. Схеми на одноелектронних транзисторах

Найпростішим пристроєм, що використовує ефект дискретного одно- електронного тунелювання, може бути джерело малого постійного струму. Використовуючи рівняння (3.4), можливо записати:

(3.14)

(3.14)

де  – частота, що підводиться до тунельного переходу для синхронізації одноелектронних перескоків на кулонівський острівець. Застосовуючи доступні на цей час переходи, отримують величини струмів

– частота, що підводиться до тунельного переходу для синхронізації одноелектронних перескоків на кулонівський острівець. Застосовуючи доступні на цей час переходи, отримують величини струмів  ~ (1-10) нА при температурі 10 мК.

~ (1-10) нА при температурі 10 мК.

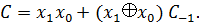

Проте, ОЕТ знайшли найбільше застосування у якості логічних елементів цифрових схем. Одними з перших практичних пристроїв були інверторні схеми із резистивним (а) та ємнісним (б) керуваннями, як зображено на рис. 3.8.

a) б)

Рис.3.8. Схеми одноелектронних логічних інверторів

Ці схеми інвертують фазу сигналу по напрузі, тому реалізують операцію HÍ, тобто, якщо на вході діє сигнал x, то на виході з’являється сигнал логічного заперечення  . Якщо вхідна напруга не перевищує напругу кулонівського блокування (3.3), тобто відповідає логічному нулю

. Якщо вхідна напруга не перевищує напругу кулонівського блокування (3.3), тобто відповідає логічному нулю  , то струм через ОЕТ не протікає, а вихідна напруга дорівнює логічній одиниці

, то струм через ОЕТ не протікає, а вихідна напруга дорівнює логічній одиниці  . При зростанні вхідної напруги знімається кулонівська блокада і при досягненні рівня логічної одиниці

. При зростанні вхідної напруги знімається кулонівська блокада і при досягненні рівня логічної одиниці  через транзистор проходить струм. Це викликає зниження вихідного потенціалу до рівня логічного нуля

через транзистор проходить струм. Це викликає зниження вихідного потенціалу до рівня логічного нуля  .

.

Резистивна схема (рис.3.8, а) має вищий коефіцієнт підсилення напруги, більшу стабільність та розділення вихід – вхід, проте має менший перепад логічних рівнів, ніж ємнісна (рис.3.8, б), що знижує завадостійкість.

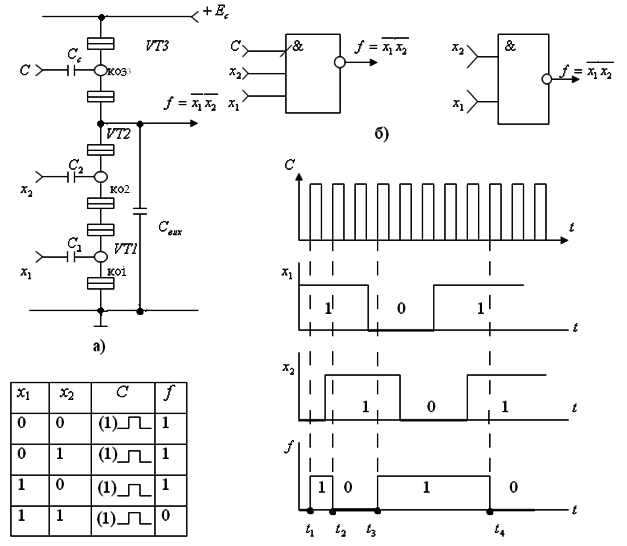

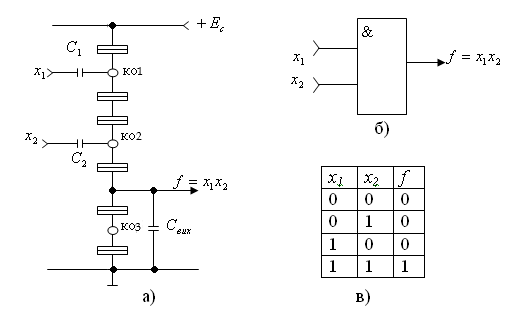

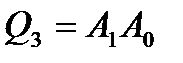

На виході логічного елементу Í сигнал одиниці з'являється тільки тоді, коли на всіх його входах діють одиничні сигнали. Логічна схема 2Í – HÍ, що зібрана на трьох ОЕТ, наведена на рис.3.9, а. Послідовно з’єднані транзистори VT1 і VT2 виконують логічну операцію множення 2Í, а VT3 – синхронізує роботу схеми. Присутність сигналу синхронізації  пришвидшує тунелювання електронів з острівців КО1 та КО2 до джерела живлення

пришвидшує тунелювання електронів з острівців КО1 та КО2 до джерела живлення  . Коса риска “/” на вході С на рис.3.9, г вказує, що імпульсний вхід керується позитивним перепадом напруги в моменти

. Коса риска “/” на вході С на рис.3.9, г вказує, що імпульсний вхід керується позитивним перепадом напруги в моменти

і

і

в) г)

Рис.3.9. Схема одноелектронного логічного елемента 2Í – HÍ (а), умовні позначення (б), таблиця станів схеми (в) та часові діаграми схеми (г)

Для створення елемента 2Í слід в схемі на рис.3.9, а поміняти місцями верхній транзистор навантаження VT3 з нижніми VT1 і VT2, тоді буде відсутня інверсія сигналу (рис.3.10). Тут і далі не показується вхід синхронізації С.

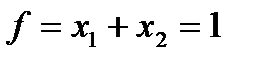

Рис.3.10. Одноелектронний логічний елемент 2Í(а), його позначення (б) і таблиця дійсності (в)

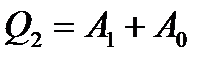

На виході логічного елемента 2АБО (рис.3.11) сигнал з’являється тоді, коли хоча б на один вхід поступає сигнал. Вона виконує функцію додавання (рис.3.11, в). Наприклад, при подачі сигналів  транзистори VT1 і VT2 вмикаються через відсутність кулонівської блокади, і на виході формується:

транзистори VT1 і VT2 вмикаються через відсутність кулонівської блокади, і на виході формується:

.

.

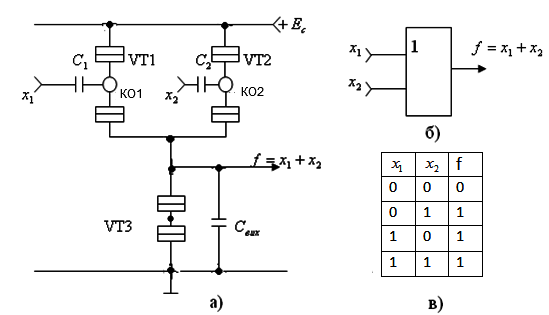

Рис.3.11. Одноелектронний логічний елемент 2АБО (а), його умовне позначення (б) та таблиця дійсності (в)

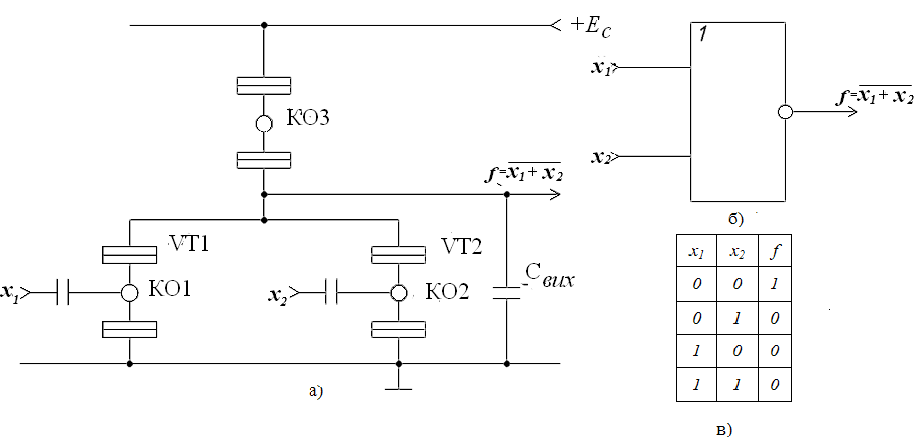

Міняючи місцями паралельно з’єднані транзистори VT1 й VT2 та OET навантаження VT3 в схемі рис.3.11, а, отримаємо логічний елемент 2АБО-НІ (рис.3.12).

Рис.3.12. Одноелектронний логічний елемент 2АБО-НІ (а), його умовне позначення (б) та таблиця дійсності (в)

Системи з двох елементів І та НІ чи АБО та НІ нарівні з системою з трьох елементів І, АБО, НІ є функціонально повними, тобто дозволяють реалізувати логічні схеми довільної складності. Для скорочення номенклатури одноелектронних елементів на практиці використовують лише два елементи І-НІ й АБО-НІ та навіть один з них.

Розглянемо деякі комбінаційні одноелектронні пристрої (автомати без пам’яті), у яких вихідні сигнали однозначно обумовлюються тільки діючою в цей час комбінацією вхідних сигналів і не залежать від вхідних сигналів, що діяли раніше.

| Х0 |

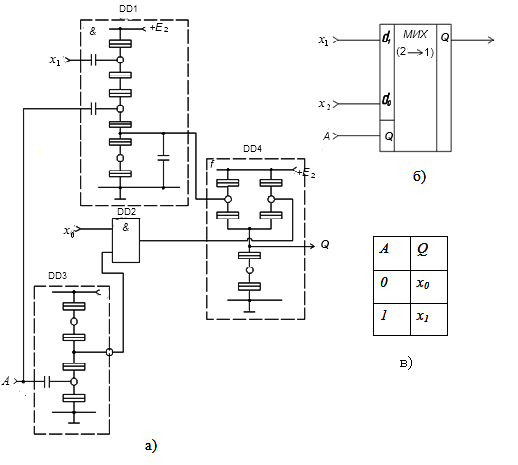

Рис.3.13. Електрична схема (а), умовне позначення (б) та таблиця станів (в) одноелектронного мультиплексора (2→1)

Мультиплексор керує передачею інформації від декількох вхідних джерел у одну вихідну лінію. Реалізацію двоходового мультиплексора (рис.3.13, а) виконують на двох логічних елементах 2І DD1 та DD2 (рис.3.10), одному НІ DD3 (рис.3.5, а) та одному 2АБО DD4 (рис.3.11, а). На рис.3.13 наведена електрична схема мультиплексора (2→1) на ОЕТ.

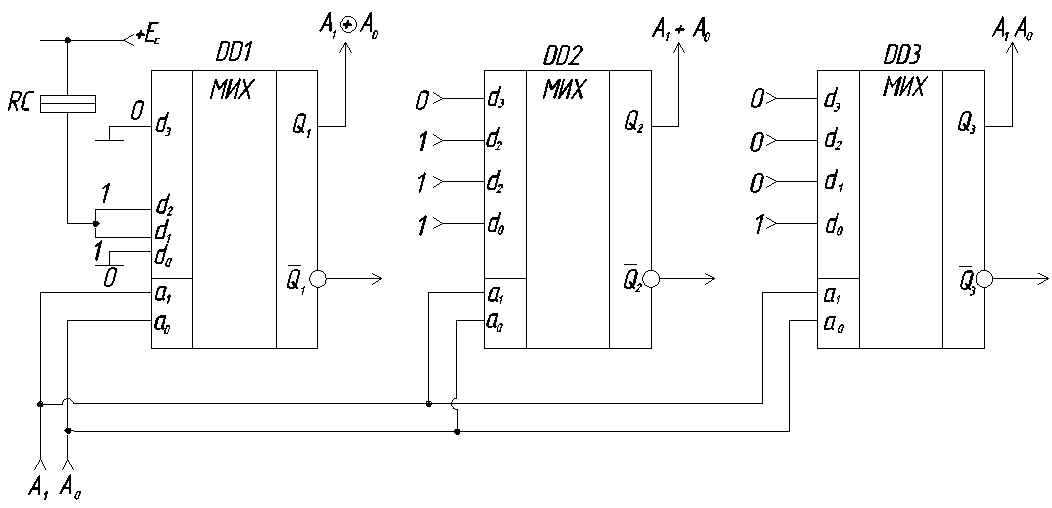

Він має два інформативних входи данних d0 та d1 ,один адресний вхід A і один прямий вихід Q. Використовуючи таблицю станів (рис.3.13, в), отримують функцію алгебри логіки дії мультиплексора (2→1):

(3.14)

(3.14)

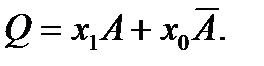

Окрім головного призначення комутацій вхідних сигналів, мультиплексори знаходять застосування у багатьох комбінаційних логічних елементах. Наприклад, за допомогою одноелектронних мультиплексорів (4→1) реалізуються різні функції алгебри логіки (рис.3.14, а). Для цього на інформаційні входи d3, d2, d1, d0 подають фіксовані значення аргументів функції.

а)

| A1 | A0 |

|

|

|

б)

Рис.3.14. Універсальні можливості застосування одноелектронних мультиплексорів (4→1) (а) та їх таблиця станів (б)

Також одноелектронні прилади використовують в арифметично

логічних пристроях (АЛП), які виконують логічні та арифметичні операції для обробки цифрової інформації. АЛП є одним з основних

комп`ютерних вузлів. До АЛП, наприклад, відносять суматори (додавачі).

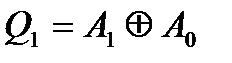

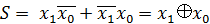

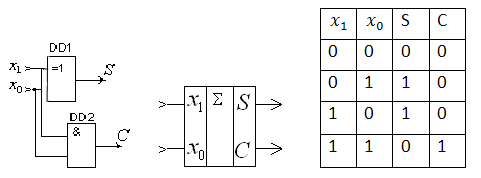

Півсуматор (півдодавач) складає коди двох однорозрядних доданків x0 та х1 і формує на виході однорозрядні сигнали суми S та переносу до старшого розряду С:

, (3.15)

, (3.15)

. (3.16)

. (3.16)

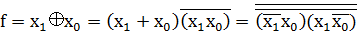

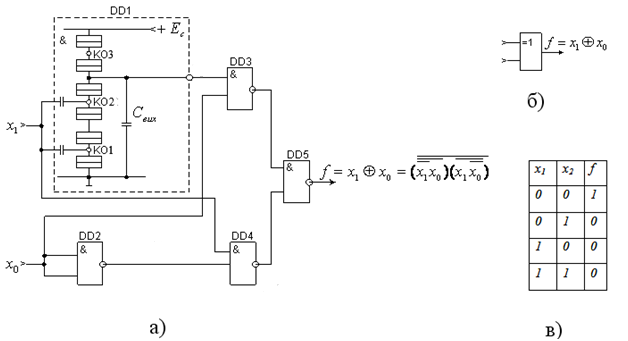

Функція рівнозначності (3.15) називається Виключне АБО чи сумою за модулем два. Її можна перетворити для різних базисних елементів:

. (3.17)

. (3.17)

Технічна реалізація останнього з отриманих рівнянь (3.17) та таблиці дійсності на базі п’яти однотипних схем 2І-НІ(DD1-DD5) (рис.3.9, а) наведена на рис. 3.15.

Рис. 3.15. Схема (а), умовне позначення (б) та таблиця дійсності (в) реалізації логічної операції Виключне АБО на одноелектронних транзисторах

З урахуванням рівнянь (3.15), (3.16), одноелектронних схем 2І (рис.3.10,а) та Виключного АБО (рис. 3.15,а) синтезуюсь схему півсуматора, як показано на рис 3.16.

Рис3.16. Одноелектронна схема півсуматора (а), його умовне позначення (б) та таблиця дійсності (в)

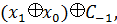

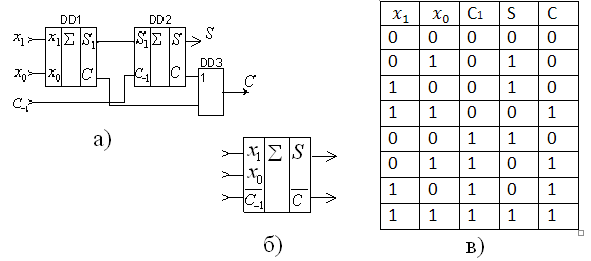

На базі одноелектронних півсуматорів будують однорозрядний суматор, який формує з вхідних сигналів двох доданків х1 і х0 та переносу з молодшого розряду С-1 два вихідних сигнали суми S та переносу до старшого розряду С (рис.3.17):

)

)  +(

+(  )

)  =

=  (3.18)

(3.18)

(3.19)

(3.19)

Для цього потрібно, як випливає з рівнянь (3.18) і (3.19), два півсуматори DD1 та DD2 (рис. 3.16, б) та елемент 2АБО DD3(рис. 3.11, а).

Рис 3.17. Однорозрядний суматор (а), умовне позначення (б) і таблиця дійсності (в)

На одноелектронних елементах І, АБО, НІ створені не тільки комбінаційні та логіко-арифметичні пристрої, а і послідовністні (автомати з пам’яттю), у яких вихідні сигнали залежать як від діючих, так і попередніх вхідних сигналів. Це, наприклад, тригери, лічильники, регістри і т.д.

Отже, на базі одноелектронних приладів реалізовані низькотемпературні (Т ≤ 4,2 K) аналогові та практично всі логічні і цифрові інтегральні схеми.

Контрольні завдання до глави 3

3.1. Розрахувати величину напруги кулонівської блокади UКБn, якщо на кулонівському острівці накопичилось n=1, 10 або 100 електронів, а його ємність СП=5 аФ.

3.2. Розрахувати частоту одноелектронних коливань струму І=1 пА, 100 пА та 1 нА.

3.3. Розрахувати ємність кулонівського острівця при температурах Т=10 мК та 4,2 К.

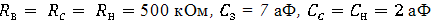

3.4. Побудувати порогові характеристики ОЕТ з кулонівськими доменами, якщо ємності транзистора складають: СЗ=7 аФ, СВ=2 аФ і СС=4аФ.

3.5. Побудувати ВАХ ОЕТ для кількості електронів n=10, а ємності СС=СВ= 5аФ, СЗ=10 аФ.

3.6. Побудувати вихідні осцилограми f (рис.3.9, г) для логічних елементів 2І, 2АБО-НІ, 2АБО та Виключне АБО

3.7. На схемі мультиплексора (рис. 3.13, а) показати всі функції, які виконують одноелектронні елементи.

3.8. В схемі мультиплексора (2→1) (рис 3.13, а, б) створити комплементарний вихід  .

.

3.9. Спроектувати одноелектронний мультиплексор (4→1) на базових логічних елементах І, НІ, АБО .

3.10. Записати функцію логіки дії одноелектронного мультиплексора (4→1).

3.11. Заповнити таблицю станів мультиплексора (4→1).

3.12. Заповнити таблицю станів  ,

,  ,

,  для одноелектронних мультиплексорів (4→1) на рис 3.14, а.

для одноелектронних мультиплексорів (4→1) на рис 3.14, а.

3.13. На рис. 3.15, а схеми х1  х0 на виходах п’яти елементів 2І-НІ надписати всі здійснюємі функції схеми та скласти таблицю станів

х0 на виходах п’яти елементів 2І-НІ надписати всі здійснюємі функції схеми та скласти таблицю станів

3.14. Реалізувати схему Виключне АБО за рівняннями (3.15) та (3.17).

3.15. Реалізувати одноелектронний RS-тригер на логічних елементах 2І-НІ.

Дата добавления: 2016-11-02; просмотров: 1325;