ГЛАВА 8 ИНТЕГРАЛЬНЫЕ СХЕМЫ 3 страница

Фильтр — микроэлектронное устройство, предназначенное для разделения электрических колебаний различных частот. По виду частотной характеристики фильтры делятся на фильтры верхних частот, пропускающие колебания с частотами выше заданной. Фильтры нижних частот пропускают колебания не выше заданной граничной частоты. Полосовые фильтры пропускают колебания в заданном интервале частот. Режекторные, или заграждающие, фильтры задерживают колебания в заданной полосе частот. В радиотехнике достаточно хорошо разработаны методы расчета фильтров и их синтеза. Микроэлектронная технология позволяет создать фильтры в виде ИС.

Модулятор — микроэлектронное устройство, осуществляющее управление заданным параметром колебательного процесса в соответствии с сигналами передаваемого сообщения. Воздействие модулирующих сигналов на параметры модулируемых колебаний осуществляется с помощью нелинейного управляющего элемента. Различают амплитудные, частотные, фазовые, импульсные и другие типы модуляторов.

Преобразователь — микроэлектронное устройство, предназначенное для преобразования электрических сигналов. Особое место в этом классе приборов занимает аналого-цифровые преобразователи (АЦП) и цифроаналоговые преобразователи (ЦАП). Эти устройства позволяют стыковать приборы, обрабатывающие информацию в аналоговой и цифровой формах. ЦАП и АЦП являются сугубо микроэлектронными устройствами, реализованными в виде ИС.

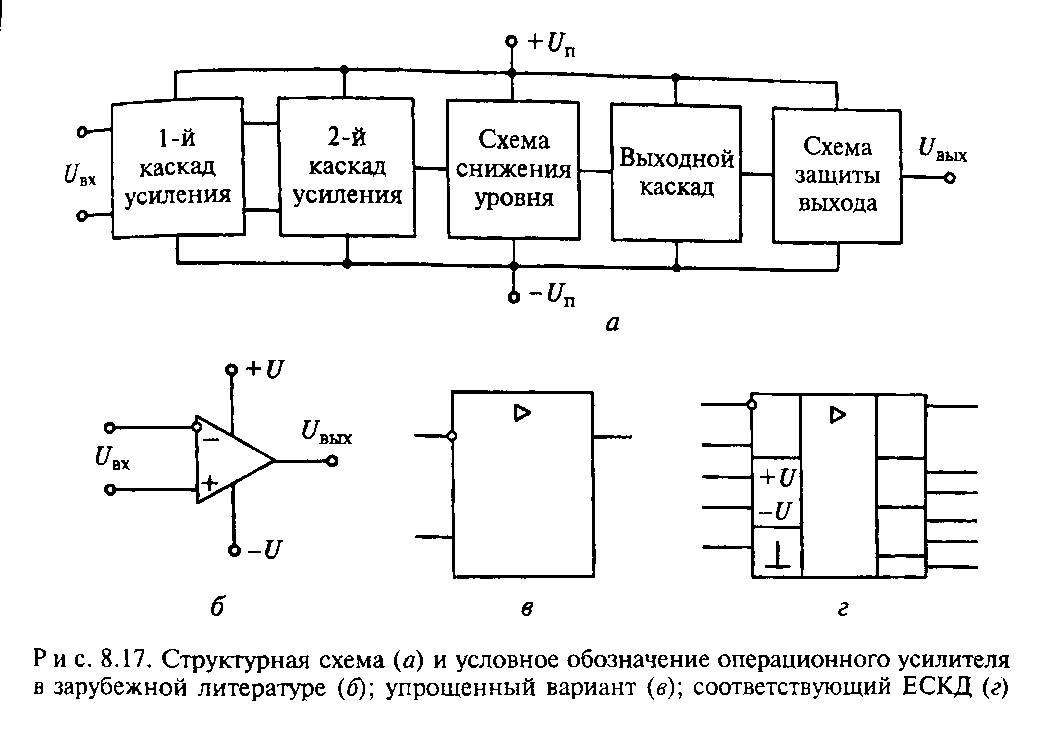

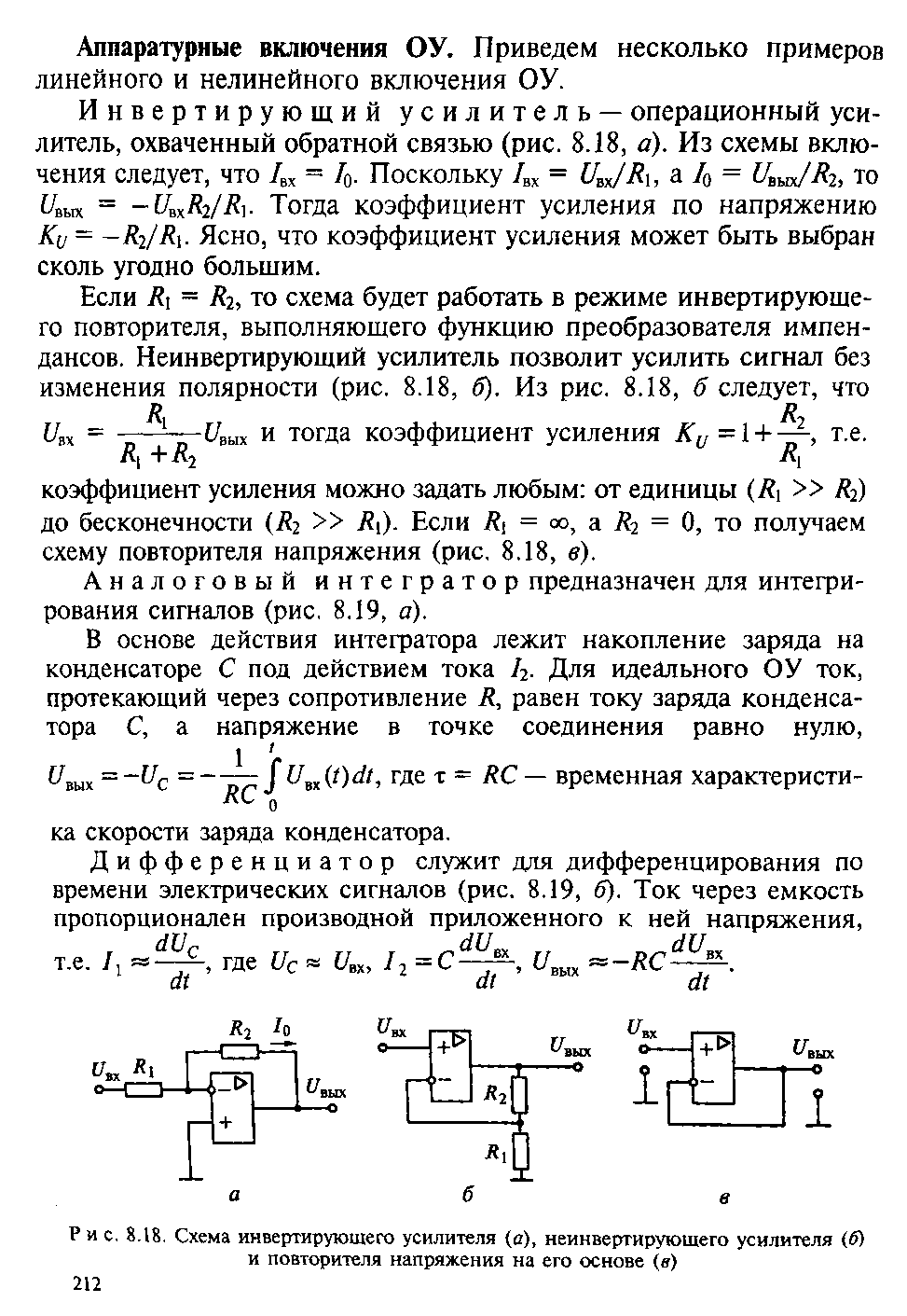

Операционный усилитель (ОУ) представляет собой микроэлектронное устройство, предназначенное для усиления как постоянного тока, так и электрических колебаний. Операционный усилитель обязательно имеет внешние цепи, предназначенные для выполнения некоторых линейных и нелинейных операций. В некотором смысле операционный усилитель является элементной базой для аналоговых преобразователей.

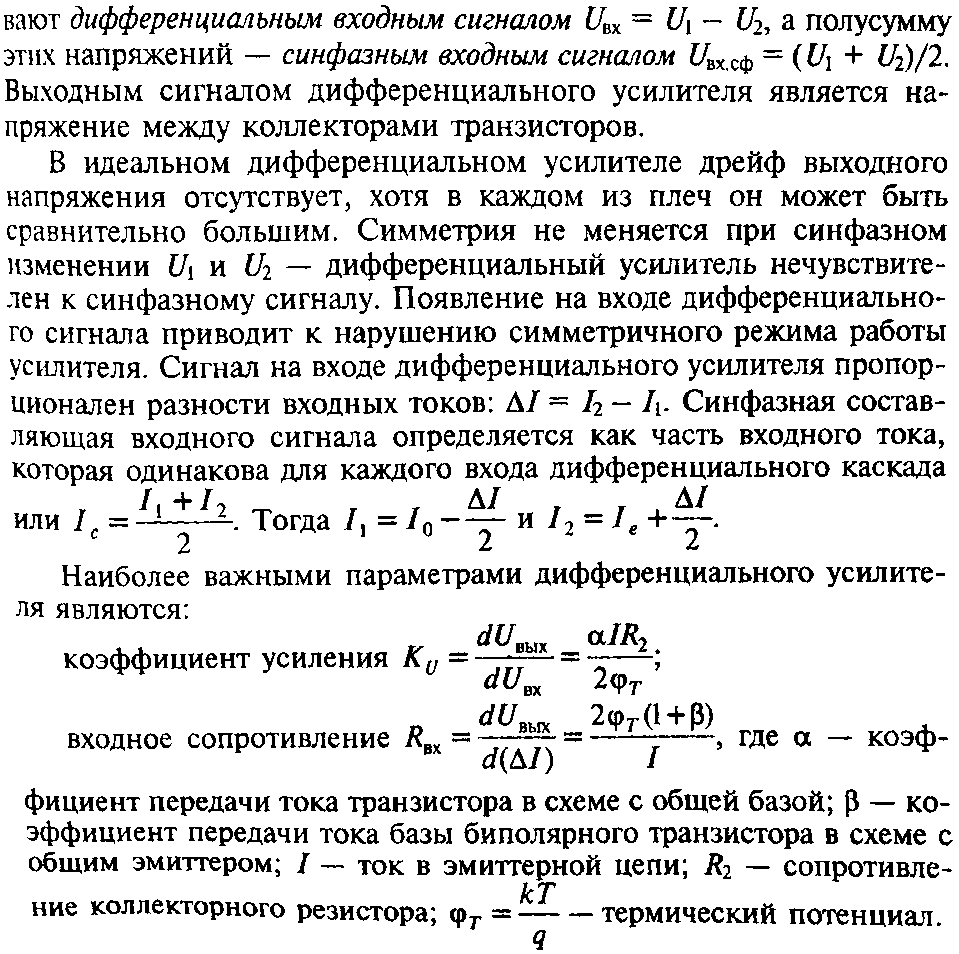

В основе схемы операционного усилителя лежит дифференциальный усилительный каскад (рис. 8.16). Два идентичных транзистора Т[ и Т2 и диффузионные резисторы и Л2 формируют два транзисторных усилителя, включенных симметрично. В дифференциальном усилителе два входа и два выхода. При передаче на входы дифференциального усилителя одинаковых (синфазных) сигналов напряжение на входах практически не меняется. Разность напряжений, формируемых на входах (базах транзисторов 7\ и Г2), назы- 208

Дифференциальный усилитель мощности можно реализовать и на полевых транзисторах, которые по сравнению МДП-транзисто- рами обладают большей стабильностью характеристик и малым уровнем собственных шумов. Схема на полевых транзисторах аналогична схеме на дифференциальном усилителе на биполярных транзисторах: подобная симметрия плеч, сохранение чувствительности усилителя к синфазному входному сигналу. Дифференциальный усилитель на полевых транзисторах имеет высокое входное сопротивление. Это позволяет во входных цепях всегда обеспечивать режим холостого хода, в котором разность потенциалов затворов полевых транзисторов совпадает с разностью напряжений источников входных сигналов.

Операционный усилитель имеет в основе дифференциальный усилитель и поэтому способен реагировать только на дифференциальный сигнал. Дифференциальный усилитель является базовой структурной единицей операционного усилителя, может быть реализован на биполярных, полевых транзисторах, а также на их соче-

_______________________ . _ _ о __ _ и и____________

тании при условии полной технологической и схемной совместимости.

Операционный усилитель будет реализовать заданную для него конкретной схемой включения функцию тем точнее, чем ближе его параметры будут приближаться к параметрам идеального операционного усилителя.

Реально идеальных ОУ не существует, например, создать усилитель с бесконечной полосой пропускания даже при конечном коэффициенте усиления невозможно. Весьма распространены так называемые ОУ общего назначения.

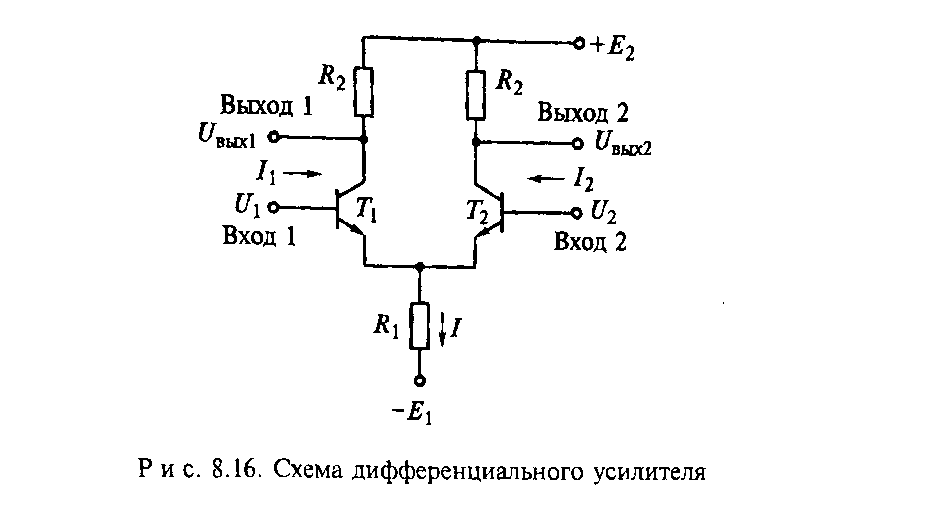

Конструкция интегральных ОУ почти всегда соответствует структурной схеме на рис. 8.17, а с небольшими отклонениями, например, может быть три каскада усиления напряжения, может не быть схемы защиты выхода от коротких замыканий. Входные выводы усилителя обозначены знаками плюс и минус. Знак плюс означает, что выходное напряжение совпадает по фазе с напряжением, поданным на данный вход, этот вход называют неинвертирующим. Знак минус говорит о том, что выходное напряжение ОУ противоположно по знаку напряжению, поданному на этот вход. Питание необходимо производить от равных разнополярных источников питания, что позволяет получить симметричное относительно нулевого уровня выходное напряжение.

На рис. 8.17, б, в, г приведены условные обозначения операционных усилителей.

Коэффициент усиления операционного усилителя К лежит в пределах 104...109, входное сопротивления достигает 100 МОм, а выходное сопротивление составляет 102 Ом. Операционный усилитель имеет малый уровень собственных шумов, сильное подавление синфазной составляющей (около 60 дБ), широкую полосу пропускания 0...10 МГц. Операционный усилитель является микроэлектронным устройством универсального применения. Операционные усилители конструктивно выполняют в виде интегральных схем средней степени интеграции.

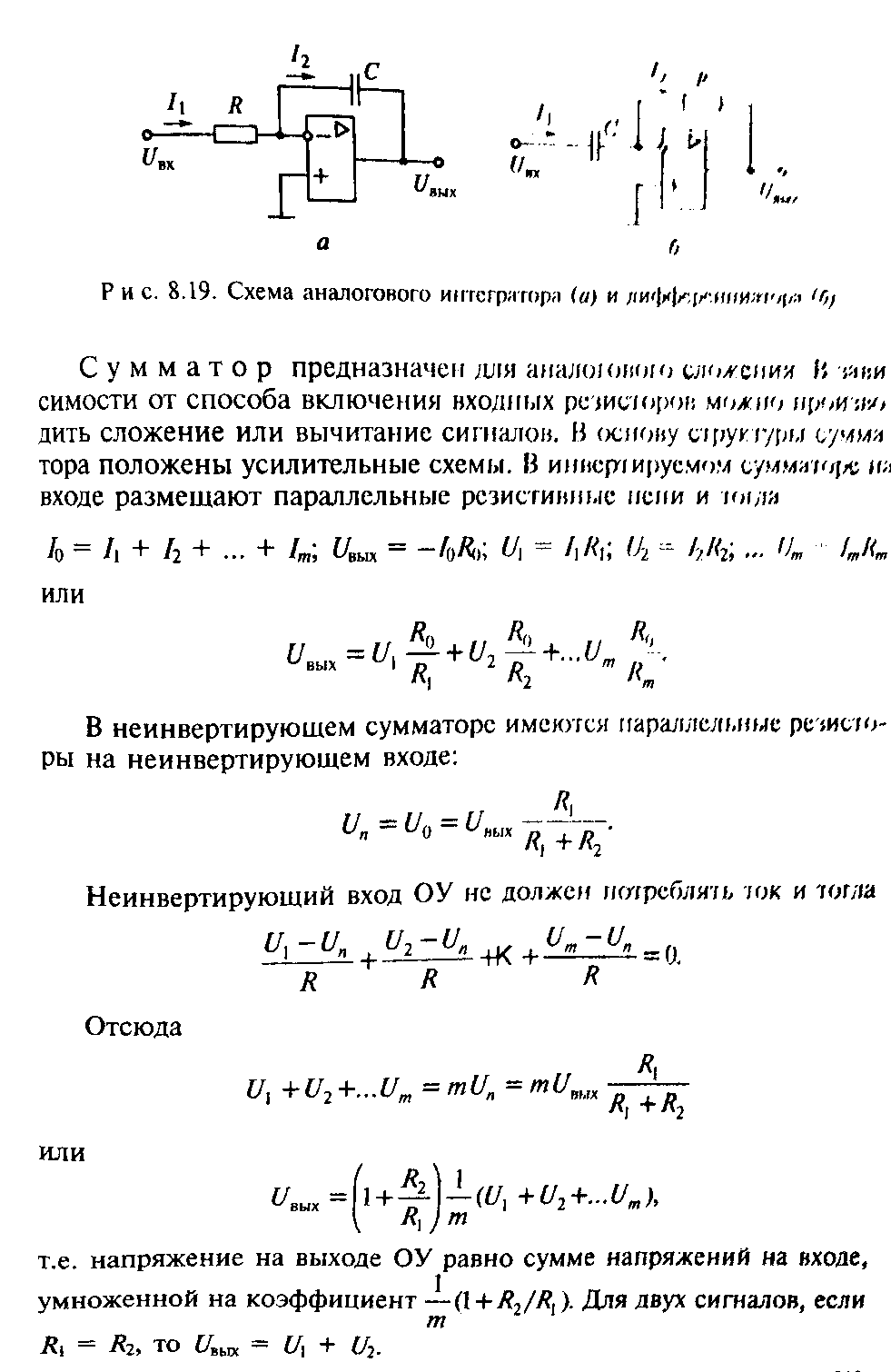

Помимо выполнения с помощью ОУ традиционных математических операций, таких как суммирование, вычитание, интегрирование и дифференцирование, на ОУ реализуют всевозможные усилители постоянного тока, усилители переменного напряжения и тока, логарифмические усилители, видеоусилители, усилители-ог- раничители, повторители напряжений, активные фильтры, модуляторы и демодуляторы, аналоговые умножители и делители, функциональные преобразователи, компараторы, генераторы гармонических колебаний, генераторы колебаний прямоугольной и треугольной форм, ждущие мультивибраторы, формирователи напряжений, схемы задержек, цифроаналоговые и аналого-цифровые преобразователи.

Вычитателъ используют для вычитания сигналов, и его схема формируется на базе инвертирующего и неинвертирующего усилителей. В стационарном режиме Щ = 1/п, а £/вых = 02 - их. Меняя значения резисторов в цепях, можно производить аналоговое вычитание с весомыми коэффициентами.

Компаратор предназначен для сравнения входных напряжений с опорным. В зависимости от входных напряжений на выходе можно получить напряжение, соответствующее логическому нулю или логической единице. На инвертирующий вход усилителя подают два сигнала на параллельные идентичные цепи. К неинвертирующему входу подключается резистор для уменьшения значения ошибки за счет входных токов ОУ.

Компаратор работает так, что

при 1/\ + и2 < 0, иъых > 0, что соответствует 1;

при 1/1 + и2 > О, £4ых < 0, что соответствует 0.

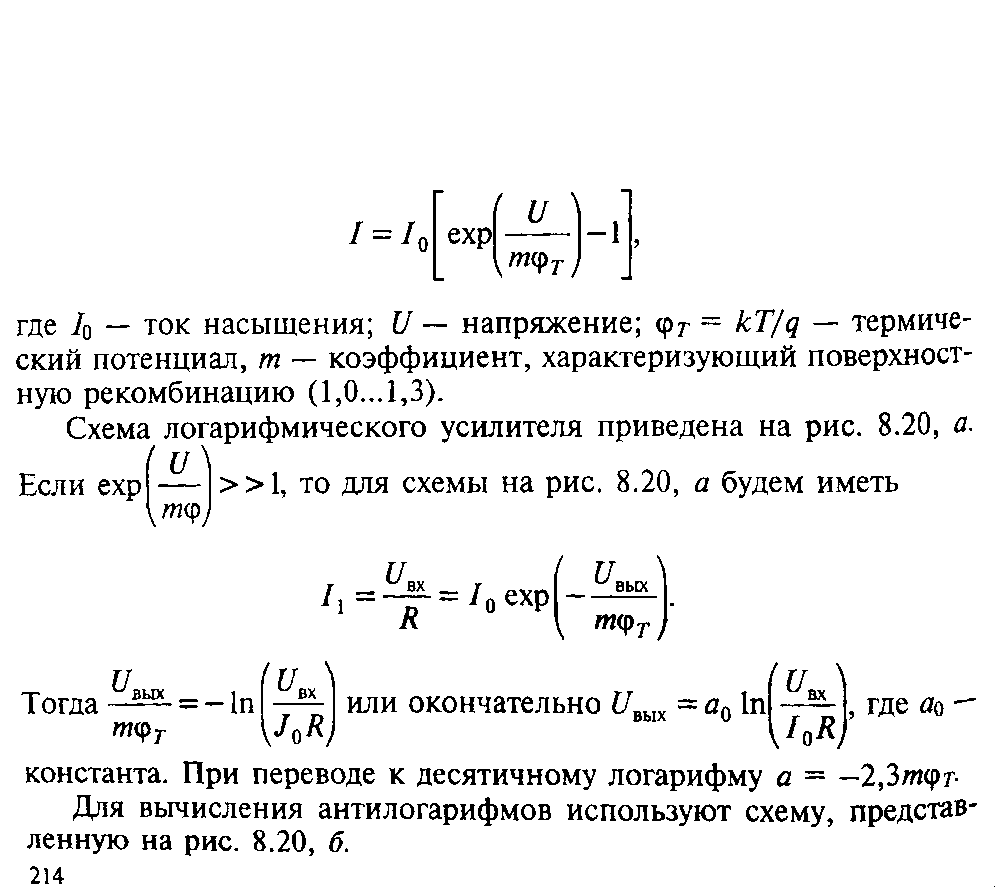

Примером нелинейного включения ОУ служит логарифмический усилитель.

Логарифмический усилитель выполняет логарифмирование входных и выходных сигналов. В процессе логарифмирования используют нелинейные свойства вольт-амперной характеристики р-я-перехода. Ток через /?-л-переход определяется зависимостью

Рис. 8.20. Схема логарифмическою усилителя (а) и вычислителя антилогарифмов (б)

Окончательный вил выражения хля выходного напряжения следующий: 1§бвых = аЪты + а, где а = 1/(2,3/жрт); Ь = \gikR).

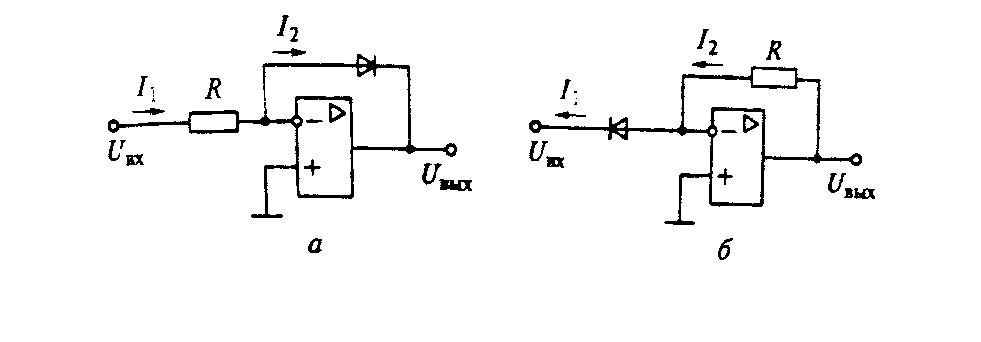

Логарифмический умножитель представляет собой устройство умножения двух или более аналоговых величин, используя сложения логарифмов этих сигналов. Логарифмический умножитель является аналогом логарифмической ячейки (рис. 8.21).

Два аналоговых сигнала вводят в параллельные логарифмические усилители, на входе которых имеются значения \&х и \%у. Прологарифмированные сигналы подаются на сумматор, на выходе которого получаем логарифм произведения этих сигналов \%{ху).

Сумматор представляет собой рассмотренную схему неинвертирующего сумматора, позволяющего получить на выход значение

+ 1|*у = \gixy). Далее этот сигнал поступает на усилитель, вычисляющий антилогарифмы. Выражение 1&(ху) потенииируется и на выходе получаем 1 — ху — произведение двух аналоговых сигналов, поступивших на вход логарифмического умножителя.

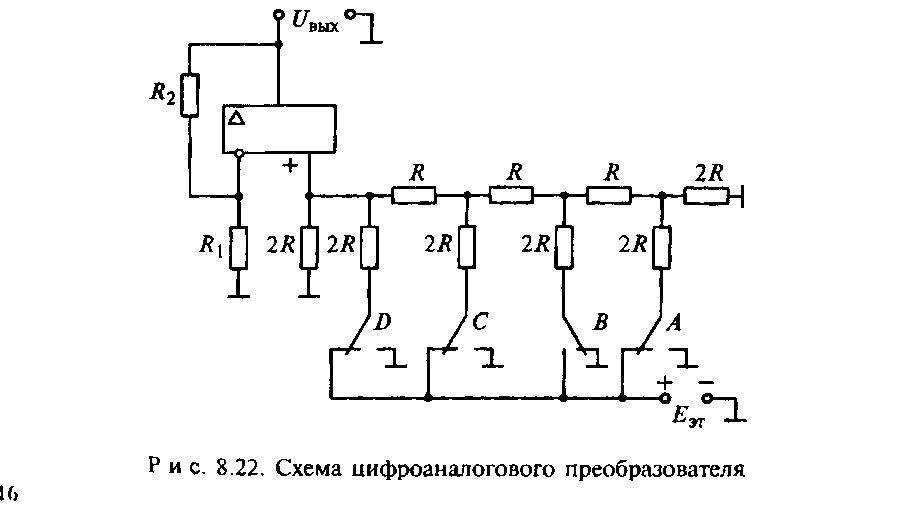

Цифроаналоговый преобразователь (ЦАП) — это микроэлектронное устройство для автоматического преобразования числовых кодов в эквивалентные им значения определенной физической величины. Коды обычно представляют в двоичной, десятичной и какой-либо другой системе исчисления. Выходные физические величины представляются в виде временных интервалов, угловых перемещений, напряжений или токов и т.п.

Существуют разнообразные конструкции ЦАП. На рис. 8.22 представлена схема ЦАП на основе делителя типа Я — 2Я и операционного усилителя. Ключи А, В, С и В подключают в нужном порядке резисторы 2Я к источнику эталонного напряжения, когда соответствующий разряд двоичного числа равен единице. Если разряд числа равен нулю, то ключ замыкается на землю. На рис. 8.22 положение ключей соответствует числу 1101. На инвертирующем входе ОУ создают напряжение, соответствующее делению эталонного напряжения. Операционный усилитель работает по схеме не- инветирующего сумматора.

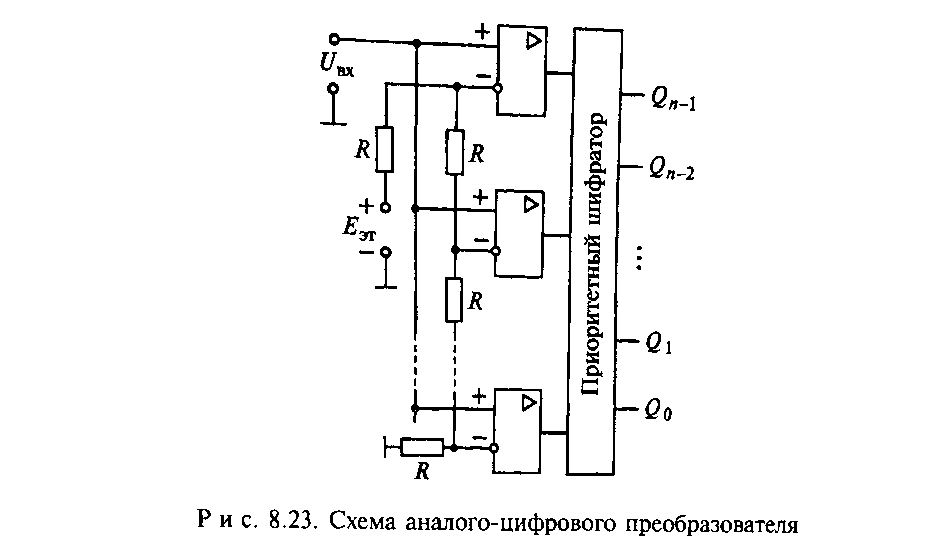

Аналого-цифровой преобразователь (АЦП) — микроэлектронные устройство, осуществляющее автоматическое преобразование непрерывно меняющегося аналогового сигнала в цифровой код. Процесс аналого-цифрового преобразования включает этапы дискретизации (квантования) непрерывного сигнала по времени, уровню или по обоим параметрам одновременно. Квантовый сигнал в дальнейшем кодируется. Часто в качестве исходной величины используют такие основные сигналы, как напряжение или ток, частота или фаза электрических колебаний. Процессы квантования и кодирования в микроэлектронных АЦП производят

с помощью аналоговых устройств в микроэлектронном исполнении. На рис. 8.23 приведена схема АЦП параллельного кодирования, позволяющая преобразовывать аналоговое напряжение в «-разрядное двоичное число. Эталонное напряжение Еэт с помощью резисторного делителя делится на 2” градаций и подается на инвертирующие входы операционных усилителей. Для 2” градаций должно быть 2й — 1 операционных усилителей. Неинвертирующие входы ОУ соединены, на них подают входное аналоговое напряжение, равное максимально возможному.

На инвертирующем входе верхнего усилителя напряжения соот-

2п -1

ветственно будет Еэт —— и т.д. Операционные усилители включе-

ны по схеме компараторов и позволяют сравнивать аналоговое напряжение с частью эталонного напряжения. Если аналоговое напряжение превышает напряжение на инвертирующем входе ОУ, то на выходе появляется положительное напряжение. Положительный сигнал интерпретируется как логическая единица. В противном случае на выходе ОУ появится отрицательное напряжение, интерпретируемое как логический нуль.

8.5. Базовые матричные кристаллы и программируемые логические интегральные схемы

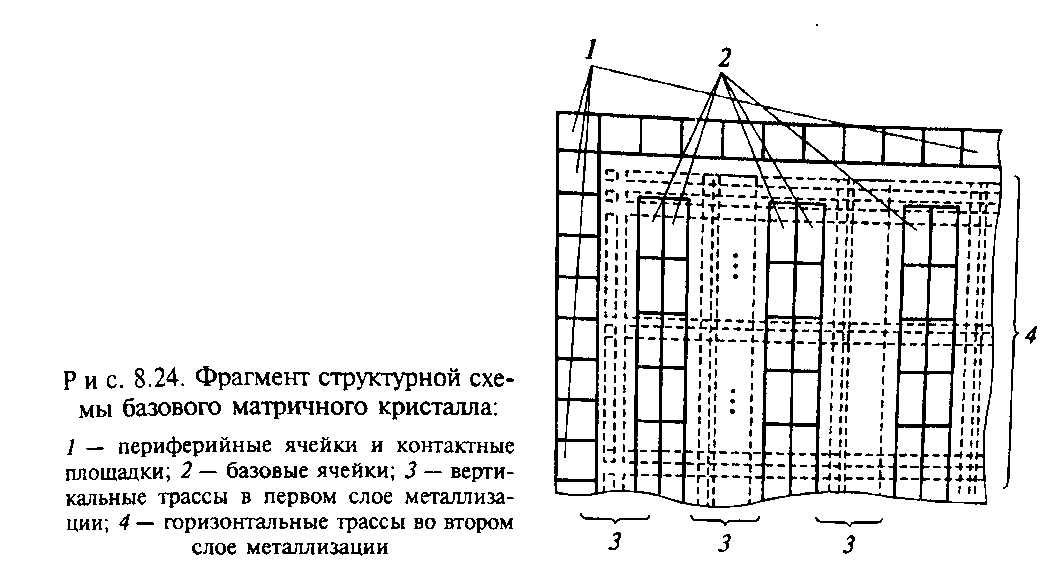

Базовые матричные кристаллы (БМК) представляют собой большие интегральные схемы, программируемые в процессе технологии с помощью формирования последнего слоя металлизации.

Развитие технологии и схемотехники СБИС сопряжено как с ростом степени интеграции и объемов производства, так и с повышением стоимости разработок, а также стоимости обработки одного бита информации. Создавали строго специализированные БИС, нацеленные на выполнение определенных функций. В настоящее время широко применяют другой подход, основанный на достоинствах программного и аппаратного подходов. Программа закладывается в архитектуру и алгоритмы обработки, а аппаратная составляющая — в параметры и архитектуру БИС. Такие БИС называют базовые матричные кристаллы. Они позволили решить ряд проблем, характерных для развития микроэлектроники. Например, увеличение сложности микросхемы делает ее более специализированной. БМК же позволяют использовать архитектуру БИС под конкретную задачу. При производстве БМК реализуется идея, высказанная еще в 1980-х гг. Гордоном Муром из фирмы «Ше1» и заключающаяся в создании «кремниевых мастерских», в соответствии с которой проектирование осуществляет потребитель, а изготовление БИС в кремниевой мастерской.

Такой подход позволяет снизить стоимость производства, создать многофункциональные схемы их типовых ячеек, решить проблему оптимизации числа внешних выводов схемы, использовать ранее разработанные и многократно используемые конструктивные схемотехнические решения.

Базовые матричные кристаллы состоят из нескольких основных элементов, расположенных на кристалле в зависимости от его конструктивно-технологического исполнения (рис. 8.24). БМК выполняется по принципу «море вентилей» и содержит порядка 105, например, четырехтранзисторных некоммутированных ячеек, предназначенных для построения функциональных узлов ИС. По периферии кристалла на фиксированных местах расположены 232 контактные площадки для подключения элементов ввода/вывода и питания.

Матрица базовых ячеек занимает большую часть площади кристалла и состоит из отдельных ячеек, выполняющих определенные функции. Различают конструктивно однородную матрицу, состоящую из функционально однородных или неоднородных ячеек. Неоднородная матрица имеет ячейки, либо фиксированные по определенной координате, либо имеющие неодинаковые размеры. Базовые ячейки представляют собой определенные конструктивно-технологические варианты логических ячеек, ячеек памяти и т.п. Базовые ячейки группируются в макроячейки в виде группы из четырех симметрично расположенных ячеек либо в линейку ячеек. 218

2.1?

Выбор конфигурации оптимален в том случае, если все выводы сосредотачиваются на границах.

Большинство выводов ячеек имеет эквипотенциальные пары на противоположных сторонах ячейки, что существенно облегчает последующую трассировку. В матрице могут быть размещены специальные буферные ячейки, микроячейки, реализующие типовые функциональные узлы, например запоминающие устройства, регистры, аналоговые блоки и т.п.

Многослойную систему металлических проводников, соединяющую базовые ячейки в соответствующие функциональные структуры и подключающую их к шинам электрического питания, называют трассой, которая располагается на нескольких уровнях. Вертикальные трассы располагаются в первом слое металлизации, горизонтальные — во втором. В ряде разработок трассировка может быть и в большем числе слоев.

Трассы межсоединений могут различаться емкостью каналов, а также конструктивным исполнением. Помимо алюминиевых тонкопленочных шин используют поликремниевые шины. В конструкциях БМК на МОП-транзисторах с молибденовыми затворами используют молибденовые шины. Наиболее низкоомные электрические соединения формируют в наружном слое.

Электрические контакты между шинами различных технологических слоев создают в местах пересечения вертикальных и горизонтальных отрезков трасс. Подключение источника питания к ячейкам матрицы может быть как индивидуальным, так и групповым. Вспомогательные схемы (схемы обрамления) и контактные площадки, расположенные по периферии кристалла, представляют

собой схемы контроля и диагностики, источники опорного напряжения, трансляторы уровней и т.п. Все схемы связаны с контактными площадками и через них осуществляется ввод-вывод информации.

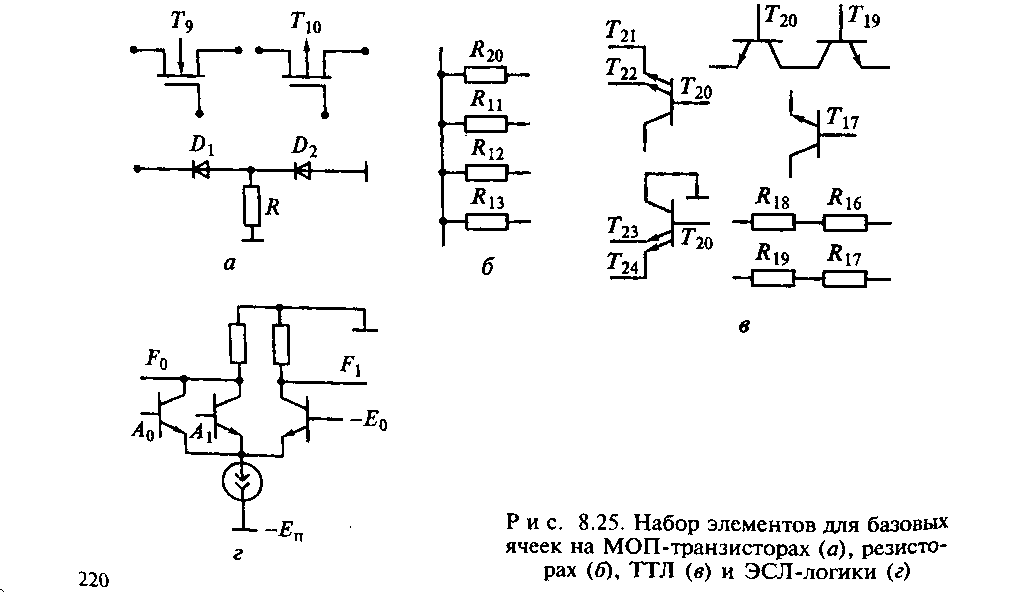

Элементной базой БМК являются различные логические схемы, ячейки памяти, расположенные в одном или двух ярусах. Существует большое число конструктивно-технологических решений схем базовых ячеек (рис. 8.25).

Развитие технологии изготовления микросхем стимулировало работы по объединению в одном кристалле биполярных и МОП-транзисторных структур. Это направление получило название БиМОЛ-технологии, а при использовании комплементарных транзисторов — БиКМОП-технологии.

Главным достоинством этих приборов микроэлектроники является соединение воедино преимуществ МОП- и биполярных транзисторных структур. Действительно, высокая плотность интеграции, низкая рассеиваемая мощность, высокая помехоустойчивость, характерные для МОП-структур, сочетаются с хорошей выходной нагрузочной способностью и высоким быстродействием биполярных структур. Концепция построения базовой ячейки вентиля на БиКМОП-структурах основана на дополнении к стандартному КМОП-вентилю усилителя формирователя тока на биполярных

транзисторах. Аналогично можно сформировать БиКМОП-инвер- тор. На основе таких элементов формируют схемы вентилей, применяемых в матричных кристаллах. В БиКМОП снижение тока стока МОП-транзисторов может быть компенсировано улучшением коэффициента усиления биполярных транзисторов, т.е. основой для всех базовых ячеек являются вентили различных конструкций.

Достоинства вентильных матриц: конкретная схема может быть реализована с использованием небольшого числа технологических операций, регулярность структуры позволяет потребителю быстро разработать свою конкретную подсистему с высокой вероятностью функционирования (95 %). Таким образом, вентильные матрицы представляют собой некоторые полуфабрикаты изделий микроэлектроники, на которые нужно нанести разводку в соответствии с требованиями заказчика.

Программируемые логические матрицы представляют собой готовые изделия, конструктивно содержащие две вентильные матрицы, например, матрицу элементов типа И, матрицу элементов типа ИЛИ, все узловые точки которых соединены диодами. В ходе программирования по заданию заказчика каждое такое соединение либо размыкается, либо остается без изменения. Итогом коммутации является нужная логическая структура типа И/ИЛИ. Это позволяет получить заданную комбинаторную булеву логику.

Специализированные БИС придают изделиям уникальные свойства, решают конкретные целевые функции.

Полузаказная интегральная схема — класс ИС, имеющих постоянную (заранее спроектированную схему) и переменную (определяется требованиями заказчика) части.

Заказная интегральная схема — класс ИС, содержащих стандартные или специально созданные элементы или узлы по заранее заданной функциональной схеме.

Проектирование схем на стандартных элементах заключается в подборе оптимизированных функциональных блоков или стандартных ячеек, их размещении и коммутации. Стандартные элементы выбирают из заранее спроектированной библиотеки элементов. Процесс изготовления схем на стандартных элементах идентичен процессу изготовления схем, проектируемых вручную. Стандартные ячейки выполняют в виде аналогов соответствующих устройств малой и средней степени интеграции. Это могут быть арифметиче- ско-логические устройства, регистры и т.п., называемые иногда макроэлементами. В качестве макроэлементов можно интегрировать стандартные БИС. В этом случае на одном кристалле можно размес

тить систему на основе микропроцессора. Такой метод называют методом процессорного ядра, или методом суперинтеграции.

Микросхемы, относящиеся к заказным, могут разрабатываться также по ячеечному принципу, которые представляют собой своеобразный гибрид из стандартных ячеек. Они конструируются одновременно с разработкой микросхемы. Этот тип БМК занимает промежуточное положение между полностью заказными схемами и схемами на стандартных ячейках. Иногда отождествляется проектирование микросхем на стандартных ячейках и ячеечное проектирование, а соответствующие микросхемы называют ячеечными.

К недостаткам матричных кристаллов следует отнести значительные сроки и затраты на проектирование специализированных ИС на основе БМК. Эта негативная особенность послужила предпосылкой для появления нового класса специализированных полу- заказных микросхем (СПИС) — программируемых логических ИС (ПЛИС).

Программируемые логические интегральные схемы — ПЛИС (Programmable Logic Devices — PLD) представляют собой сверхбольшие интегральные схемы, содержащие от нескольких десятков до нескольких сотен ИС, которые могут быть соединены пользователем произвольным образом. Программированная логика обладает возможностью внутрисистемной репрограммируемости, что в сочетании с высоким быстродействием и уровнем интеграции, а также с малой потребляемой мощностью и низкой стоимостью, что способствует широкому применению. Другими словами, ПЛИС — это интегральные микросхемы, содержащие программируемую матрицу элементов логического И (конъюнкторов), программируемую или фиксируемую матрицу элементов логического ИЛИ (дизъюнк- торов) и так называемые макроячейки (macrocells). Макроячейки, как правило, включают в себя триггер, тристабильный буфер и вентиль исключающее ИЛИ, управляющий уровнем активности сигнала. Размерность матриц и конфигурация макроячеек определяют степень интеграции и логическую мощность ПЛИС.

Программируемые логические интегральные схемы родились в жесткой конкурентной борьбе, когда в микроэлектронике существовали две противоречивые тенденции. С одной стороны, необходимо сократить жизненный цикл изделия микроэлектроники, чтобы удовлетворить быстро меняющиеся требования заказчика. С другой стороны, необходимо постоянно повышать требования к сложности, быстродействию, потребляемой мощности, надежности и стоимости изделий микроэлектроники. Требуется сокращение цикла проектирования с тем, чтобы на рынке появились новые из- 222

Zif

лелия, соответствующие требованиям времени и прогресса. Эти факторы способствуют формированию завершенной автоматной структуры. ориентированной на реализацию как комбинационных (дешифраторов, мультиплексоров, сумматоров), так и последовательностных схем (управляющих автоматов, контроллеров, счетчиков).

Возможности, заложенные в ПЛИС, позволяют превратить ее в ИС с любой функцией цифровой логики. Проектирование сводится к выявлению программируемых элементов (перемычек или запоминающих ячеек), после удаления которых в структуре схемы остаются только те связи, которые необходимы для выполнения требуемых функций.

Наибольшее распространение получили МОП ПЛИС, имеющие более 100 тысяч вентилей, а также встроенную память и ядро *системы-на-чипе»: процессор, контроллер, сигнальный процессор. Эти схемы можно быстро переконфигурировать. Логическая емкость определяется числом эквивалентных вентилей типа 2И - НЕ.

Функциональная схема вычислительных структур и систем требует использования сложных СБИС, проектирование которых не всегда экономически оправдано. Зачастую «приспосабливают» готовую схему в нужную СБИС. Это сопряжено с риском неточной адаптации схемы. Когда речь идет о цифровых схемах, то такая проблема может быть решена с помощью программируемых пользователем логических интегральных схем. Технология изготовления ПЛИС позволяет обеспечить высокую степень интеграции С105... 106 элементов/кристалл), высокое быстродействие (108 оп./с) возможность реализации в одном корпусе комбинационных И/ИЛИ последовательных схем.

ПЛИС характеризуются высоким быстродействием (единицы наносекунд), многократностью перепрограммирования и низкой потребляемой мощностью.

Программируемость ПЛИС обеспечивают наличием в них множества элементов программирования (ЭП), выполняющих функции ключей. В состав ЭП входят управляемые двухполюсники, проводимость которых может быть задана пользователем либо очень малой (замкнуто), либо достаточно большой (разомкнуто). Состояния элементов программирования задают конфигурацию (схему) цифрового устройства, формируемого на кристалле.

В ПЛИС применяют следующие типы элементов программирования PROM; EPROM; FLASH; SRAM. Быстрый процесс оперативного программирования можно производить неограниченное число раз.

Репрограммирование ПЛИС с памятью копфшурш/ии SRAM производится в рабочем режиме, путем записи кодовой последовательности в цепочку триггеров ОЗУ-конфшурапии. (лившие информации как специфический процесс воздействия на «лноминаю- щие элементы требует относительно длительных операций и поэтому устранено. Несмотря на повышенную сложность упоминающего элемента, ПЛИС с памятью конфигурации SRAM занимают важнейшее место в устройствах с высокой логической емкостью.

По способам коммутации элементов логических матриц различают несколько классов ПЛИС.

Программируемые логические матрицы (FPLA. Field Programmable Array) состоят из базовых ячеек типа И и ИЛИ. Такая архитектура недостаточно полно использует программируемую матрицу ИЛИ.

Программируемая матричная логика (PAL, Programmable Array Logic) содержит программируемую матрицу И и фиксированную матрицу ИЛИ. К этому типу относится большинство ПЛИС небольшой степени интеграции.

Программируемые коммутируемые матрицы (CPLD, Complex Programmable Logic Divieces) содержат матричные логические блоки, объединенные коммутационной матрицей. Это ИС высокой степени интеграции с программируемой матрицей И и фиксированной матрицей ИЛИ.

Программируемые матрицы логических элементов (FPGA, Field Programmable Gâte Array) состоят из логических блоков (Л Б) и коммутирующих соединений блока ввода/вывода информации.

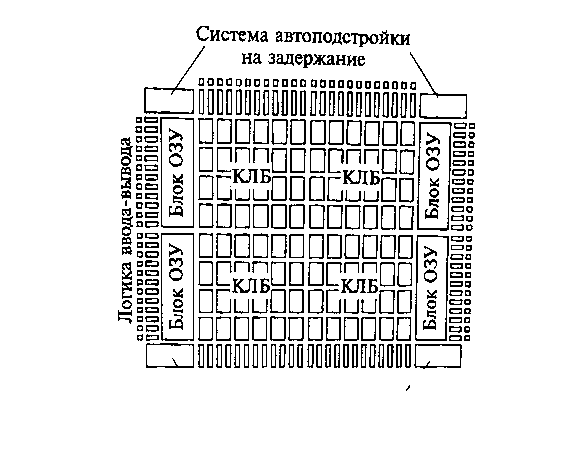

Конфигурируемый логический блок КЛБ (CLB, Configured Logic Block) представляет собой комбинацию таких элементов, как ОЗУ, регистры, функциональные генераторы (рис. 8.26).

Для программирования логического устройства используют СОЗУ, ОЗУ базового блока, размещенные вблизи логических ячеек, осуществляющие конфигурацию системы и функции управления. ПЛИС имеют свою архитектуру, основными элементами которой являются конфигурируемый логический блок, блоки ОЗУ, блоки ввода-вывода информации и т.д.

Стремительное развитие архитектурных решений ПЛИС вызвало к жизни новые их разновидности, связанные с расширением их функциональных возможностей. В ПЛИС встраивают специализированные блоки программируемых логических ядер. Они представляют собой программируемые устройства, содержащие ячейки специализированных ИС и блоки программируемой логики. Такое ядро называют soft-ядром. Это виртуальный компонент, не имеющий строгих геометрических границ. Для выполнения soft-ядром

^ооооопопоппоооааоаоааооо/

Система автоподстройки на задержание

Рис. 8.26. Вариант базового блока ПЛИС типа /УС4

логических функций не существует физических атрибутов. Встроенное программируемое аппаратное ядро (кагё-ядро) позволяет реализовать различные функции по требованию заказчика. Нагё-ядро является виртуальным компонентом с заданными параметрами, которые описаны на физическом уровне. По уровню характеристик 5о/?-ядро уступает аппаратным Ад«/-ядрам.

Развитие ПЛИС позволяет сократить цикл проектирования современных цифровых систем, сохранить гибкость конструкции и использовать новейшие технологические решения. Эти вопросы решаются благодаря способности ПЛИС вносить изменения в конструкцию системы на любом этапе процесса проектирования. При этом ПЛИС отвечает сочетанию таких характеристик, как быстродействие, минимальная потребляемая мощность, уровень интеграции и стоимость.

8.6. Интегральные схемы СВЧ-диапазона

Твердотельная СВЧ-электроника начала интенсивно развиваться с появлением кремниевых, а затем и арсенид-галлиевых СВЧ-транзисторов. Большая номенклатура, многофункциональность, сложность реализации технических характеристик при небольшой потребности в основном для военной техники стимулировали развитие твердотельной СВЧ-электроники по пути гибридной технологии интегральных схем (ГИС). В рамках этой технологии

15 225

отдельные активные и пассивные компоненты — транзисторы конденсаторы, линии задержки, ключи и другие элементы и компоненты объединяют в ГИС. Гибридная технология на первых этапах развития твердотельной СВЧ-электроники за счет несложных технологических приемов — разварки, пайки, склеивания — при резком увеличении функциональных возможностей СВЧ-аппарату- ры обеспечила высокие технические характеристики, приемлемую надежность, резкое снижение массы и габаритных размеров и низкую цену аппаратуры за счет использования компонентов высокого качества.

Техника СВЧ широко используется в научных исследованиях, радиосвязи, системах обработки информации, особенно специального применения, а также в быту. Широкое использование СВЧ-устройств связано прежде всего с возможностью концентрации высокочастотного излучения в узкий луч. В перспективе это позволит создавать экономичные системы связи, радиолокационные станции обнаружения и сопровождения цели. Большая информативная емкость СВЧ-диапазона позволяет уплотнить число каналов связи, организовать многоканальную передачу телевизионных каналов.

В последнее время существенно повысился интерес к твердотельной электронике СВЧ вообще и к монолитным ИМС СВЧ-диапазона в частности. Этот интерес вызван потребностью в развитии электронного оборудования спутникового вещания и связи, бортовой электроники самолетов и ракет (как гражданского, так и специального применения), радиолинейных линий, оборудования связи, подвижных объектов и т. д. Одним из серьезных стимулов для развития монолитной микроволновой микроэлектроники является повышенный интерес к развитию техники фазированных антенных решеток (ФАР), для создания которых необходимо большое количество (тысячи и десятки тысяч) однотипных дешевых приемопередающих модулей.

Дата добавления: 2016-06-13; просмотров: 2965;