ГЛАВА 8 ИНТЕГРАЛЬНЫЕ СХЕМЫ 2 страница

Для сохранения минимальной площади маски необходимо больше использовать параллельные цепи и меньше последовательные соединения. Схемы на МОП-транзисторах имеют в интегральном исполнении простую конфигурацию прежде всего из-за высокого импеданса транзисторов и малого тока через их затвор.

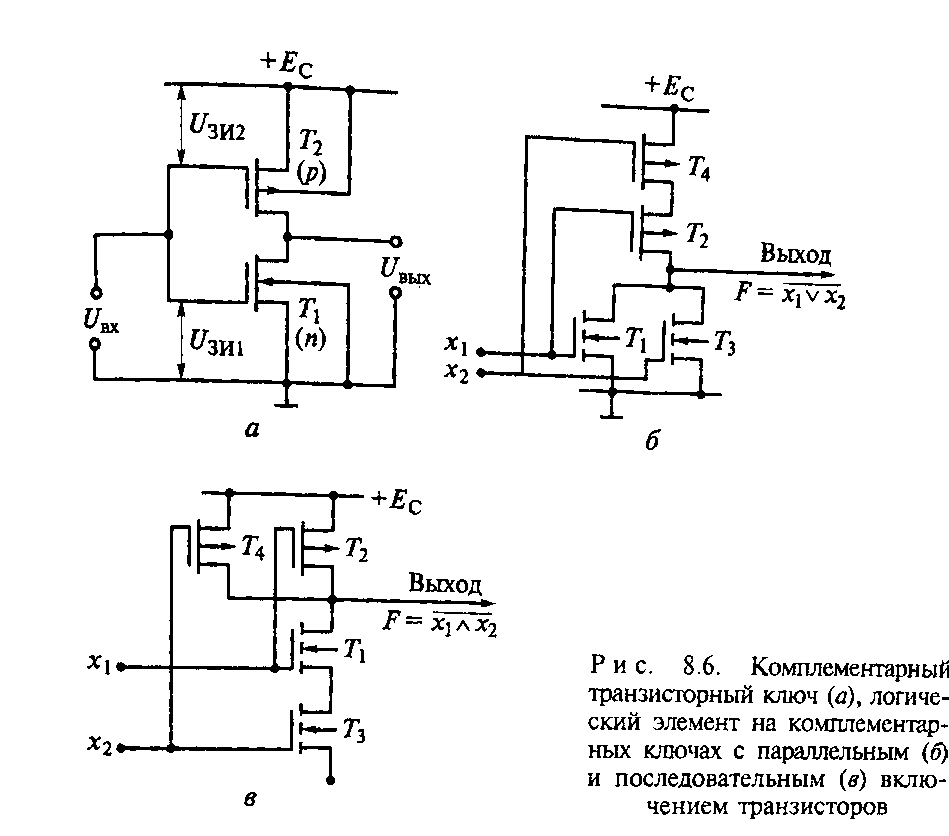

Элементы на комплементарных ключах. Простейшей схемой, реализованной на комплементарных транзисторах, является комплементарный транзисторный ключ (рис. 8.6, а). Если £4х = 0, то С/Зи1 = 0, а С/зИ2 = — Ес и «-канальный транзистор Т\ закрыт, а /¿-канальный Т2 открыт. Ток через транзисторы будет незначительный, так как сопротивление закрытого транзистора велико.

Если входное напряжение £/вх > 0, то С/ЗИ1 = Ес, иШ2 = 0. В этом случае «-канальный транзистор Т\ открыт, а /¿-канальный транзистор Тг закрыт. При этом ток в общей цепи будет по-прежнему мал, потому что уже закрыт /¿-канальный транзистор.

Важнейшей особенностью комплементарных ключей является тот факт, что они практически не потребляют мощность в обоих состояниях.

Наиболее перспективными микросхемами логики являются интегральные элементы на КМОП-транзисторах. Они отличаются ма-

лой мощностью потребления в статическом режиме (примерно 1 • 10-9 Вт), высоким быстродействием (примерно 109Гц), большой помехоустойчивостью, высокой эффективностью использования источников питания.

В ИС на КМОП-транзисторах логические операции реализуют последовательно, включая входные транзисторы для выполнения Функции И — НЕ или параллельно для реализации функции ИЛИ — НЕ. На каждый вход при этом включают два транзистора, образующих ключевой элемент (рис. 8.6, б, в).

Следует подчеркнуть закономерность структуры КМОП логических схем, заключающуюся в том, что параллельное соединение одного типа транзисторов сопровождается последовательным соединением другого типа. Помимо высокой экономичности КМОП-схемы имеют малые рабочие напряжения (2£/0) и высокое быстродействие.

Основные недостатки КМОП — усложненность производственного процесса, несколько меньшая, по сравнению со схемами на биполярных транзисторах, производительность и тенденция к возникновению тиристорного эффекта, или защелкивания. Этот эффект заключается в том, что паразитная тиристорная область р-п-р-п может переходить в открытое состояние. В этом случае возникает большой ток, который разрушает схему.

Преимуществами КМОП-схем являются интеграция большего числа функций и меньшая рассеиваемая мощность. Благодаря последнему фактору стала возможной большая плотность упаковки элементов интегральных схем. Были разрешены проблемы обработки, за счет современных схемотехнических решений была обойдена проблема запирания. При высокой степени интеграции функции, обычно требовавшие нескольких микросхем и сложных системных соединений, можно было реализовать на одном КМОП-кристалле. Результирующим эффектом стало повышение производительности микросхем и значительное снижение ее стоимости. В настоящее время благодаря высокому уровню интеграции технология КМОП достигла большей общей производительности, несмотря на использование более медленных транзисторов.

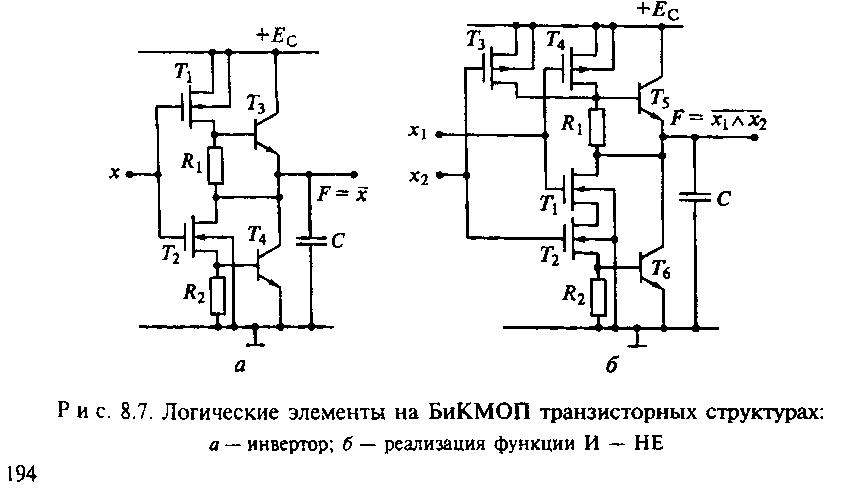

Логические элементы на биполярных и КМОП-транзисторах. Разработанная технология совмещения биполярных и КМОП транзисторных структур позволила создать варианты БиКМОП логических устройств. На рис. 8.7, а приведена схема инвертора, реализованная на КМОП- и биполярных транзисторах. Транзисторы Т\ и Тг формируют КМОП-инвертор с той разницей, что параллельно их каналам включены сопротивления Я\ и Т?2. Эти сопротивления по значению сопоставимы с сопротивлением каналов транзисторов в открытом состоянии. Выходной каскад сформирован на базе биполярных транзисторов Т3 и Г4, эмиттерные переходы которых подсоединены к резисторам.

В статическом состоянии токи через транзисторы Т\ и Т2 и соответственно через резисторы и Т?2 малы и поэтому транзисторы Тг и Тб, закрыты.

Если на входе х напряжение низкого логического уровня, то ¿¿-канальный транзистор Т\ открыт. На выходе инвертора будет высокий логический уровень, и конденсатор Сн будет заряжен.

Если на вход подать высокий логический уровень, откроется «-канальный транзистор Т2 и начнется разряд емкости через резистор /?2 и эмиттерный переход биполярного транзистора Г4. Часть разрядного тока откроет транзистор Г4, будет происходить перезарядка емкости нагрузки. Аналогично происходит процесс переключения при изменении входного напряжения от высокого логического уровня к низкому.

На рис. 8.7, б приведена схема логического элемента И — НЕ. На входе традиционно расположены последовательно соединенные транзисторы, характерные для схем типа И. Транзисторы Г3 и Т4 комплементарны к 7\ и Т2 и выполняют роль нагрузочных резисторов. Биполярные транзисторы Т5 и 7б на выходе позволяют усилить сигналы, а также нейтрализовать влияние емкостной нагрузки. Именно емкостная нагрузка является фактором ограничения быстродействия КМОП-структур.

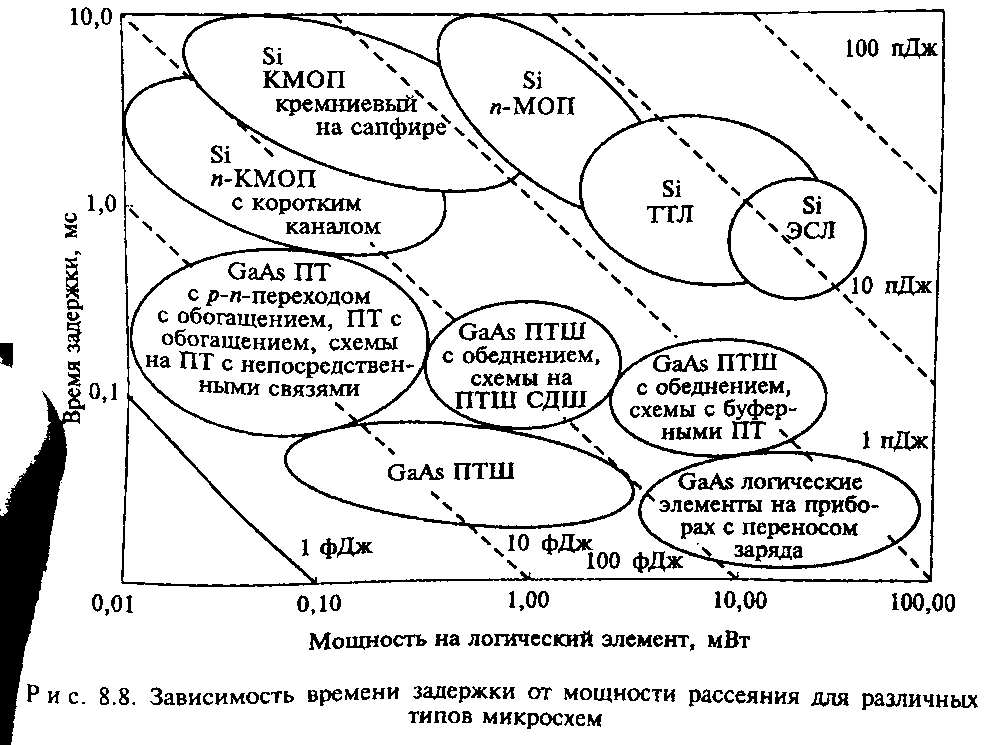

На диаграмме (рис. 8.8) приведена зависимость времени задержки от мощности рассеяния для микросхем различных типов. Наиболее перспективными по фактору качества являются арсе- нид-галлиевые схемы.

8.3. Микросхемы памяти

Организация запоминающих устройств. В вычислительных системах запоминающее устройство (ЗУ) предназначено для записи, хранения и считывания информации, является важнейшим элементом цифровой обработки и хранения сигналов и характеризуется емкостью памяти. По функциональному назначению основными видами памяти являются оперативные, постоянные и перепрограммируемые ЗУ.

Оперативные запоминающие устройства (ОЗУ) предназначены для быстрого ввода и вывода (записи и считывания) информации в любом, заранее заданном месте памяти. Синонимом ОЗУ является термин «память с произвольной выборкой». Международное обозначение — RAM (Random Access Memory).

Постоянные запоминающие устройства (ПЗУ) используют в основном для считывания ранее записанной в них информации. Запись в этом виде ЗУ производят однократно для постоянного хранения часто используемых данных. Этот класс называют также памятью только для считывания и классифицируют как ROM (Read-Only Memory).

Перепрограммируемые запоминающие устройства (ППЗУ) предназначены для частичного и многократного изменения информации в ПЗУ, внесения необходимых корректив в постоянную память. К этому классу относят и перепрограммируемое потребителем запоминающее устройство — PROM (Programable Read-Onli Memori).

Репрограммируемые ПЗУ (РПЗУ) применяют для изменения записанной информации. Технология РПЗУ основана на использовании транзисторов с плавающим затвором. К этому типу памяти относят РПЗУ с УФ-стиранием EPROM (Erasable PROM), электрически стираемая EEPROM (Electrical Erasable PROM), флэш-память (FLASH).

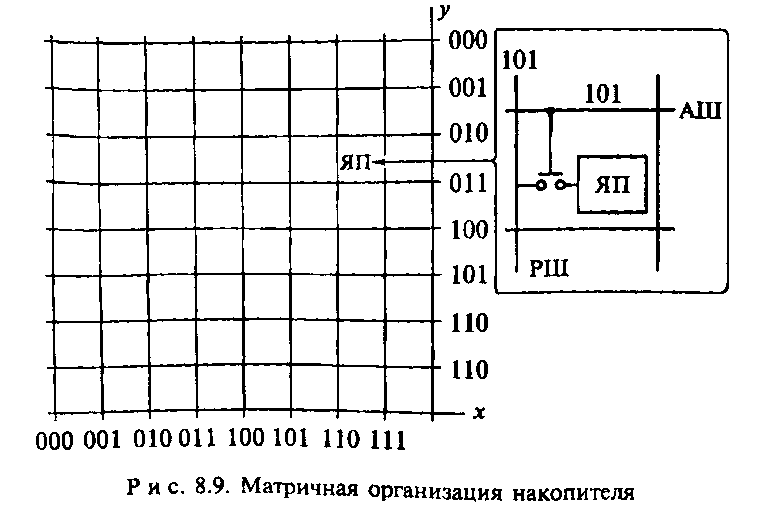

Структура ЗУ, реализованного по полупроводниковой технологии, состоит из накопителя и схем управления. Накопитель является центральной частью полупроводникового ЗУ и представляет собой матрицу, состоящую из запоминающих ячеек, вертикальных и горизонтальных, адресных и разрядных шин. Накопитель является основой ЗУ, в котором хранится информация в виде двоичных кодов.

Периферия, или схемы управления, предназначены для ввода и вывода данных. Схемы управления, как правило, состоят из дешифраторов, усилителей, регистров, коммутаторов и других схем, реализованных по совмещенной полупроводниковой технологии.

Рассмотрим организацию ЗУ и способ его реализации на различных транзисторных структурах.

Накопитель имеет форму матрицы, в узлах которой находятся ячейки памяти (ЯП), соединенные с адресной и разрядной шинами с помощью некоторого ключа (рис. 8.9). В качестве ключа может быть использован транзистор. Каждая ячейка памяти имеет свой адрес и может хранить 1 бит информации. Это одноразрядная память. В таком ОЗУ имеется один информационный вход и выход. Многоразрядные ОЗУ имеют несколько информационных входов и выходов, что позволяет записывать и считывать информацию словами. Емкость ЗУ определяется числом ячеек памяти. Каждая ячейка связана с одной или двумя адресными (АШ) и разрядными шинами (РШ). Если используется одна адресная и одна разрядная шины, то речь идет о динамическом типе памяти. Если каждая ячейка связана с двумя адресными и разрядными шинами, то речь идет о памяти статического типа. В первом способе информацию нужно периодически (во время действия импульсов питания) регистрировать. Во втором способе она хранится постоянно на период подключения источника питания.

Если на определенную адресную шину подать сигнал, то произойдет коммутация по разрядной шине, можно будет записать бит информации или его считать, если он уже записан. Разрядная

шина может записать О (РШ0) или 1 (PIUi). Адресные и разрядные шины первоначально подключены ко всем ячейкам памяти.

В зависимости от конструкции ячейки памяти, способов ее коммутации с адресными и разрядными шинами, используемых транзисторных структур, различают различные типы ЗУ.

ЗУ на биполярных транзисторах. Простейшие ячейки памяти на биполярных транзисторных структурах можно реализовать различными способами. Во всех используется емкость /ья-перехода для хранения заряда, соответствующего логическому нулю или единице. В качестве диодов могут быть использованы транзисторные структуры.

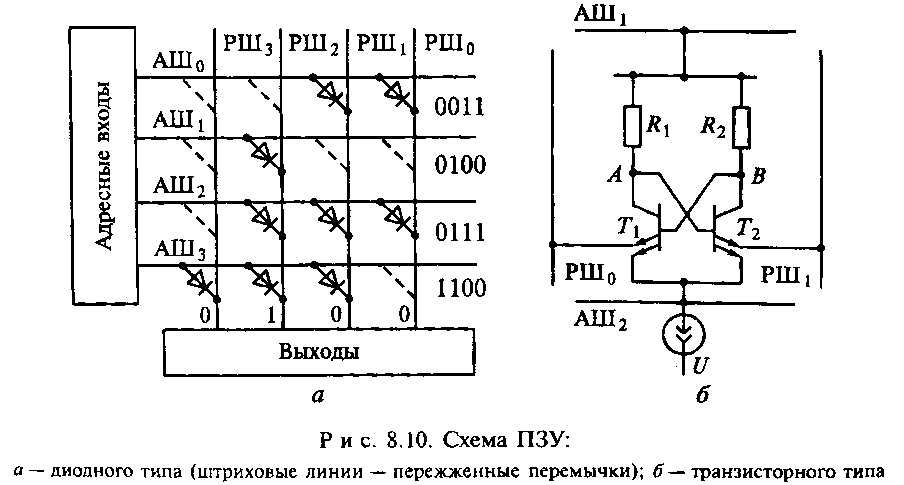

На рис. 8.10, а представлена типичная схема ЗУ, реализованная на диодах. Она состоит из накопителя, адресных входов и выходов. Каждая адресная шина предназначена для ввода определенного кода: 0011, 0100, 0111, 1100 и т.д. Запись информационного кода осуществляется с помощью диодов, которые присоединены между адресными шинами и теми разрядными шинами, на которых должна храниться логическая единица. Например, подадим на адресную шину AIUi логическую единицу в виде соответствующего напряжения в выбранной строке. Напряжение с этой адресной шины поступит только на разрядную шину РШ2. На других шинах РШо, PIlIi и РШ3 будет отсутствовать напряжение. На выход пойдет только код 0100. Пережигание встречно включенных диодов или плавких перемычек, расположенных рядом с диодом, и является процессом программирования ЗУ. Программирование производят

Накопитель

в ячейках матриц, соответствующих расположению логических нулей, для чего разработаны специальные устройства.

Такие ОЗУ ненадежны вследствие рассасывания заряда токами утечки. Поэтому наибольшее распространение получили ЗУ, ячейки которых способны хранить один заряд двоичной информации. Такие бистабильные ячейки могут быть реализованы на триггерных схемах и различных типах биполярных транзисторных структур: ТТЛ, ТТЛШ, ЭСЛ, И2Л. Многоэмиттерные транзисторы удобно использовать в конструкции ячейки памяти ЗУ статического типа.

Типовая структура накопителя интегральной схемы ЗУ, реализованная на двух эмиттерных транзисторах Т\ и Т2, приведена на рис. 8.10, б. Ячейка памяти состоит из двух транзисторов с перекрестными связями. Вторые эмиттеры соединены с шиной питания. Первые эмиттеры соединены соответственно с разрядными шинами РШ0 и РШ1 и используются для записи и считывания информации. Коллекторы транзисторов соединены через резистор с плюсовой массой питания, выполняющей также функции адресной шины АШь В одном устойчивом состоянии транзистор Т\ открыт, а Т2 закрыт. В другом устойчивом состоянии, наоборот, Т{ закрыт, а Т2 открыт.

В режиме хранения на разрядной шине РШ1 устанавливается напряжение хранения, положительное относительно общей шины микросхемы. В режиме считывания повышается напряжение как на шине АШ2, так и на шине АШь Если транзистор Т\ открыт, а транзистор Т2 закрыт, то ток в управляющем эмиттере равен нулю, напряжение на шине РШ1 не меняется. В управляющем эмиттере транзистора Т\ появится ток считывания. Напряжение на шине РШ0 повысится. На шинах РШо и РШ[ возникнет разность напряжений, которая считывается усилителем.

Постоянное запоминающее устройство имеет аналогичную с ОЗУ матрицу памяти запоминающих ячеек. ЗУ называют постоянным, потому что в каждой ячейке раз и навсегда записаны логические нули. Чтобы получить нули в нужных ячейках памяти, необходимо закрыть доступ в нужную ячейку. Это делается, например, с помощью так называемых пережигаемых перемычек. А нуль он всегда нуль. Единицы же нужно регенерировать. Этот процесс зависит от типа памяти.

ЗУ на МДП-транзисторах. Наиболее распространенным типом ЗУ являются схемы памяти на МДП-структурах. Их основными преимуществами перед ЗУ на биполярных структурах являются: малая потребляемая мощность; высокая степень интеграции; сравнительная простота технологии (число технологических операций

на 30 % меньше); низкая стоимость при больших объемах производства; высокий запас помехоустойчивости; энергонезависимость ЗУ.

В зависимости от работы накопительной матрицы ЗУ ИС памяти могут быть:

динамические ЗУ, в которых информация сохраняется в накопителе в виде зарядов на емкостях, входящих в состав элементов памяти, а регенерация зарядов происходит периодически от источника питания;

статические ЗУ, в которых сохранение информации в накопителе обеспечивается с помощью источников питания;

квазистатические, в которых информация в накопителе сохраняется в виде зарядов, а их регенерация осуществляется в определенные периоды, в течение которых происходит считывание и повторная запись считанной информации в каждом элементе накопителя.

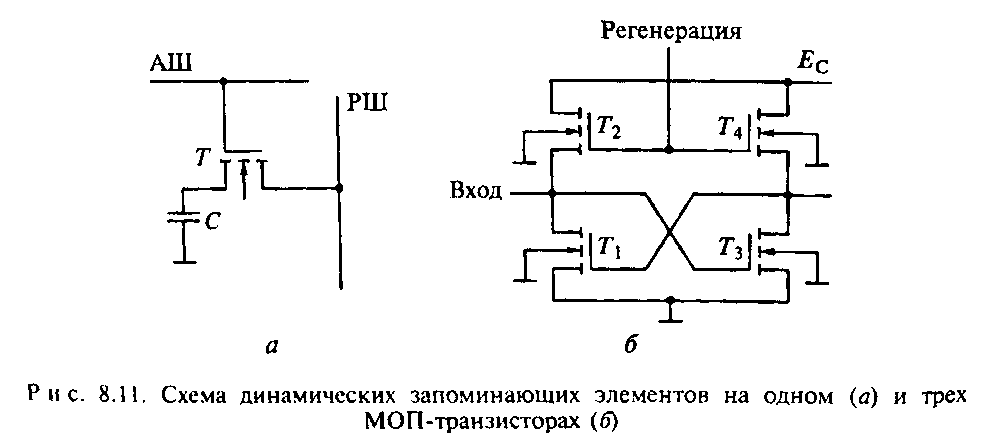

Наиболее распространены однотранзисторные ячейки памяти (рис. 8.11, а). Схема состоит из транзистора Т и накопителя заряда в виде конденсатора С. В режиме хранения напряжение на АШ близко к нулю. Транзистор Т закрыт. Конденсатор С отключен от разрядной шины. В конденсаторе хранится информация в виде разряда 0 = Си. В случае хранения логической единицы заряд

подложку. При хранении логического нуля заряд 0 = СЦ° и конденсатор будет слегка заряжаться предпороговым током транзистора от положительно заряженной РШ.

Имеются также токи утечки, способствующие уменьшению заряда. Поэтому для таких ЗУ требуется регулярный процесс регенерации для всех элементов строк. В режиме записи на разрядной

Q1 = CU[ будет постепенно уменьшаться за счет токов утечки в

шине устанавливают напряжение U1 или £/°, а затем подают положительный импульс на АШ. Транзистор отпирается и на обкладках конденсатора устанавливается нужное напряжение U1 или U0.

В режиме считывания РШ подключена к входу усилителя считывания с высоким входным сопротивлением. При поступлении импульса выборки на АШ транзистор элемента памяти открывается и происходит считывание с разрушением информации. И в этом случае необходима регенерация записанных единиц информации.

Для избежания разрушения информации во время считывания разработана схема регенерирующего каскада динамического ЗУ (рис. 8.11, б). Схема каскада реализована на триггере, включенным между линиями записи/считывания. За счет положительной обратной связи восстанавливается первоначальное значения напряжения в запоминающем элементе, т.е. при считывании информации производится регенерация хранящегося заряда.

ЗУ большого объема строят на основе этих ячеек, и они носят название ЗУ динамического типа — ДОЗУ или DRAM (Dynamic RAM).

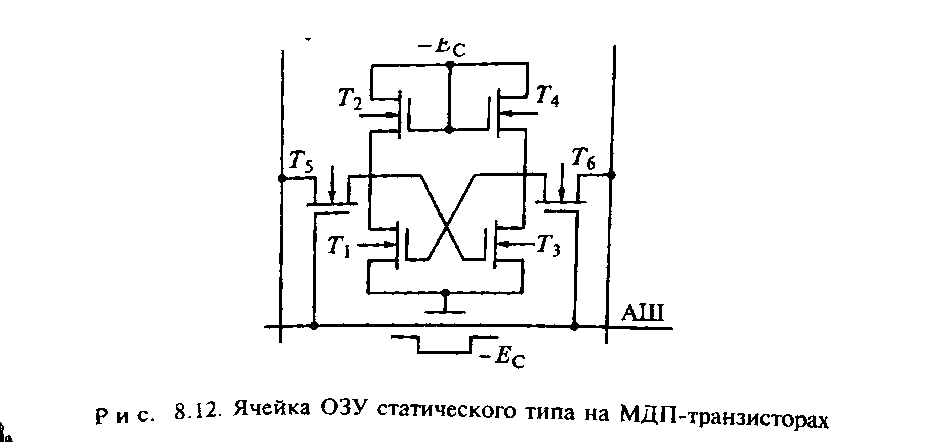

БИС ОЗУ на МДП-транзисторах статического типа SRAM (Static RAM) приведена на рис. 8.12. Конструкция ячейки на однотипных МОП-транзисторах с /ьканалом имеет классическую структуру /^-триггера с управляющими ключами Т5 и Т6, которые заперты в нормальном состоянии, и ячейки отключены от разрядных Шин РШ. При поступлении отрицательного импульса — Ес на адресную шину ключи Т5 или 7б открываются и подключают ячейку к разрядным шинам. На разрядные шины поступают уровни Q и (Г, записанные в ячейке. В режиме записи на адресную шину так- же подают импульс, в то время как на разрядные шины подаются взаимно противоположные уровни. Другими словами, роль такто-

РШп _ РШ,

»ого импульса играет импульс на адресной шине в обоих режимах. Это самые простые по схемотехнической и технологической реализации схемы ОЗУ. Однако они обладают низким быстродействием и малой степенью интеграции.

Использование КМОП-транзисторов в схемах ячеек памяти позволяет существенно повысить быстродействие, получить практически нулевую рассеивающую мощность в статическом режиме и повышенную помехоустойчивость.

Разновидность БИС ПЗУ определяется типом ячейки памяти, способом записи и стирания информации. Состав этих устройств памяти аналогичен БИС ПЗУ с двухкоординатной выборкой. Обрамление матричного накопителя, как правило, состоит из дешифраторов строк и столбцов, адресных формирователей, усилителей считывания и других схем управления. Запись информации в ПЗУ осуществляют на этапе изготовления кристаллов с помощью заказного последнего фотошаблона, формируя нужную конфигурацию металлизированной разводки. Такой тип ПЗУ называют масочным, потому что программирование осуществляется маской — последним фотошаблоном. Это широко известный технологический процесс.

В программируемые ИС ПЗУ (или ППЗУ) нужную информацию записывают электрическим способом, путем пережигания перемычек, либо пробоем /¿-«-перехода. Перемычки изготавливают из нихрома, поликристаллического кремния или алюминия. ППЗУ на основе МДП-транзисторов обладает достаточно большой информационной емкостью и низкой потребляемой мощностью.

Для широкого использования БИС ЗУ необходимо создать память, способную многократно перепрограммироваться и сохранять информацию при отключенном питании. На основе МДП-структур разработаны репрограммируемые постоянные запоминающие устройства (РПЗУ), допускающие многократную перезапись и хранение информации при отключенном питании. В основе лежит идея создания бистабильных МДП-транзисторов, которые могут находиться в одном из двух состояний, соответствующих хранению логической единицы или нуля. РПЗУ в зависимости от физического принципа работы подразделяют на два класса.

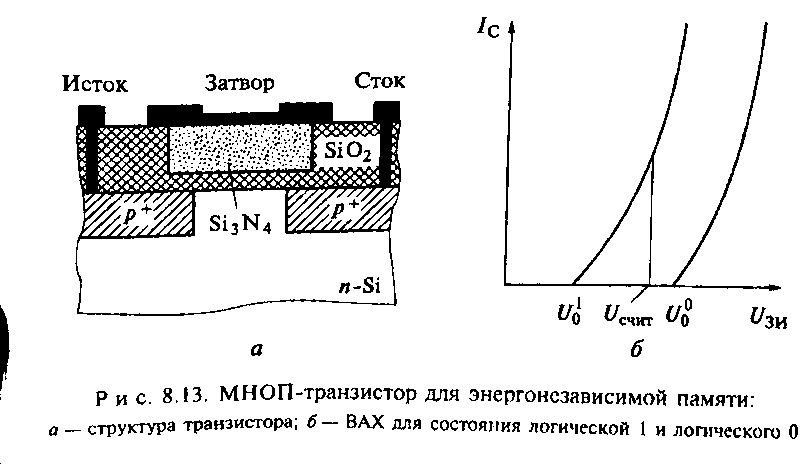

Первый класс — это устройства на транзисторных структурах, в которых используется захват заряда на естественной границе раздела двух диэлектриков. В основе работы МНОП-транзистора лежит явление накопления заряда на границе нитридного и оксидного слоев. Накопление происходит из-за неодинаковых токов проводимости в слоях. При определенном напряжении на затворе на гра-

ниие накапливается положительный заряд йО/Ж = ко2 - При большом положительном напряжении на затворе на границе накапливается отрицательный заряд, что приводит к уменьшению порогового напряжения. Благодаря зависимости порогового напряжения от напряжения на затворе, МНОП-транзистор с помощью управляющих импульсов напряжения считывания £/счит можно переводить из рабочего состояния в запертое и обратно (рис. 8.13).

Второй класс РПЗУ — это устройства на транзисторных структурах с плавающим затвором. В этих конструкциях управляющий заряд хранится в тонком проводящем слое — плавающем затворе, расположенном в диэлектрике в затворной части МДП-структуры. Заряд, аккумулированный на плавающем затворе, позволяет изменять пороговое напряжение, необходимое для открывания затвора.

На рис. 8.14 приведена схема МОП-транзистора с плавающим затвором, выполненным из поликремния. Если на затвор МОП-транзистора подать высокое напряжение и3 ~ 25 В, то формируется канал. Под воздействием поля, формируемого напряжением стока, в канале образуются горячие электроны. Они проникают сквозь туннельно-тонкий диэлектрик на плавающий затвор. На затворе формируется отрицательный заряд, способный перекрыть канал исток — сток, и транзистор закрывается (рис. 8.14, а).

Если транзистор осветить ультрафиолетовым светом, энергия квантов которого больше ширины запрещенной зоны полупроводника /ту > Ег, то плавающий затвор будет очищен от электронов, осевших там. Электроны, получив энергию излучения, способны преодолеть потенциальный барьер между плавающим затвором и каналом. Канал транзистора будет восстановлен, и транзистор бу-

Рис. 8.14. Электрически программируемое ЗУ (а) со стиранием информации

УФ-излучением (б)

дет открыт (рис. 8.14, б). Заметим, что при УФ-облучении стирается вся информация, накопленная в ЗУ.

Такая технология получения РПЗУ получила название FAMOS (Floating gate avalanche injection MOS) или МОП-транзистор с плавающим затвором и лавинной инжекцией заряда.

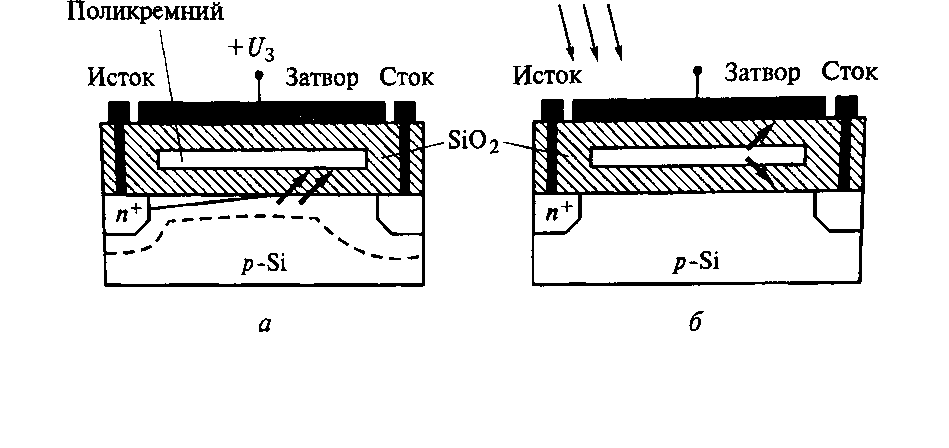

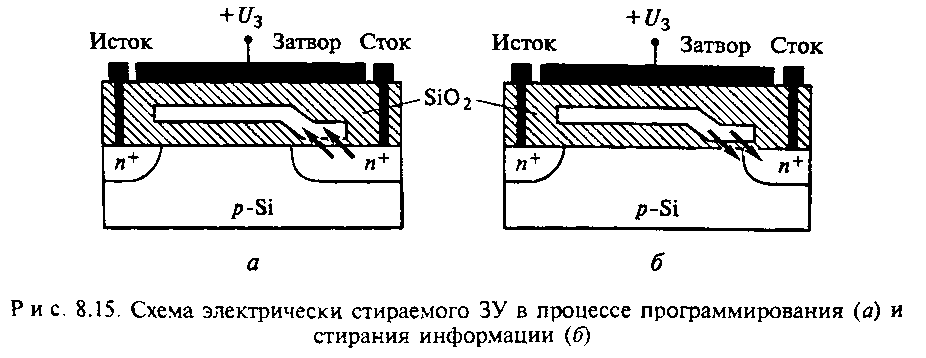

Другой конструкцией электрически репрограммируемых ЗУ является ЭСППЗУ — электрически стираемые программируемые ПЗУ. Технологию их производства называют FLOTOX (Floating gate tunnel-oxide), или плавающий затвор с туннелированием в оксиде. В транзисторной структуре этого типа (рис. 8.15) плавающий поли- кремневый затвор отделен от диффузионной области «-типа тонким слоем диэлектрика (около 200 Â). Если на затвор подать высокое напряжение (20 В), то на плавающий затвор начнут дрейфовать туннельные электроны из стока. На плавающем затворе сформируется статический заряд (рис. 8.15, а). Если на затвор подать низкое напряжение, а на сток высокое, то произойдет обратное туннелирование электронов с плавающего затвора. Произойдет процесс

стирания информации (рис. S.b. б). Процессы программирования и стирания информации имеют одинаковую скорость и отличаются только местом приложения напряжения и направлением движения

электронов.

Анализ разработок БИС ППЗУ и РПЗУ на МДП-транзисторах показывает, что разнообразие схемного построения БИС зависит от элементной базы накопителя, другими словами, от конструктивного решения ячейки памяти. Именно выбор ячейки памяти определяет напряжение программирования, время хранения информации. число циклов перезаписи информации и возможность использования одного или нескольких источников питания. Максимальным временем хранения информации после отключения источника питания обладают РПЗУ. в основе конструкции которых лежат транзисторные структуры с плавающим затвором.

К этому типу ЗУ относится популярная ф.гэш-память (FLASH). Такое название этот тип памяти получил потому, что по быстроте процесс стирания информации напоминает вспышку света. Флеш-память (Flash-Memory) — разновидность твердотельной полупроводниковой энергонезависимой перезаписываемой памяти. Она может быть прочитана сколько угодно раз, но писать в такую память можно лишь ограниченное число раз (максимально около миллиона циклов). Распространена флэш-память, выдерживающая около 100 тысяч циклов перезаписи. Это намного больше, чем способна выдержать дискета или CD-RW. В основе этого типа флеш-памяти лежит ИЛИ — НЕ элемент (NOR), потому что в транзисторе с плавающим затвором низкое напряжение на затворе обозначает единицу'. Транзистор имеет два затвора: управляющий и плавающий (см. рис. 8.15). Последний полностью изолирован и способен удерживать электроны до 10 лет. В ячейке имеются также сток и исток. При программировании напряжением на управляющем затворе создается электрическое поле и возникает туннельный эффект. Некоторые электроны туннелируют через слой изолятора и попадают на плавающий затвор, где и будут пребывать. Заряд на плавающем затворе изменяет ширину канала сток — исток и его проводимость, что используется при чтении информации.

Процессы программирование и чтение ячеек имеют разное энергопотребление: устройства флеш-памяти потребляют достаточно большой ток при записи, тогда как при чтении затраты энергии малы. Для стирания информации на управляющий затвор подается высокое отрицательное напряжение, и электроны с плавающего затвора переходят (туннелируют) на исток. В М?Я-архитектуре к каждому транзистору необходимо подвести индивидуальный контакт,

что увеличивает размеры схем. Эта проблема решается с помощью /УЛЛФ-архитектуры. В основе NAN D-тит. лежит элемент И — НЕ. Прииции работы такой же, от NOR-mn'd отличается только размещением ячеек и их контактами. В результате уже не требуется подводить индивидуальный контакт к каждой ячейке, так что размер и стоимость /УЛ/VD-ч и па может быть существенно меньше. Так же запись и стирание происходят быстрее. Однако эта архитектура не позволяет обращаться к произвольной ячейке. NAND- и МЭД-архи- текгуры сейчас существуют параллельно и не конкурируют друг с другом, поскольку находят применение в разных областях хранения данных.

Скорость некоторых устройств с флеш-памятью может доходить до 100 Мб/с. В основном объем чипа флеш-памяти измеряется от килобайт до нескольких гигабайт. Рынок флэш-памяти растет ежегодно на 15 %, что превышает суммарный рост всей остальной полупроводниковой индустрии.

Память FLASH подходит для хранения голоса, изображений, программного кода и данных, особенно там, где требуется малое энергопотребление. А также может использоваться для замены памяти программ, памяти данных пользователя и конфигурационной памяти данных для хранения идентификационных данных, калибровочной информации и других параметров системы. При этом существенно снижается общая стоимость, размер, уровень шумов, сложность производства и улучшается надежность, уменьшается энергопотребление и себестоимость.

Спрос на флэш-память постоянно растет, увеличивается число производящих компаний, цена быстро падает. Ближайшие годы пройдут под знаком расцвета флэш-памяти, что способствует ее широкому внедрению в бытовую аппаратуру.

8.4. Аналоговые интегральные схемы

Номенклатура аналоговых ИС. Аналоговые интегральные схемы предназначены для преобразования сигналов, заданных в виде непрерывной функции. Номенклатура аналоговых ИС включает различные генераторы сигналов, усилители, детекторы, задержки сигналов, модуляторы и т.д. В аппаратуре широко используют стандартные ИС, в основе конструкций которых лежат различные схематические решения, заимствованные из радиотехники дискретных элементов. Технология аналоговых микросхем как самостоятельное направление микроэлектроники развивалось с определенным отставанием от технологии цифровых ИС. Среди причин такого от- 206

ставания явился более ограниченный набор элементов полупроводниковых микросхем. В частности, в микроэлектронике не используют индуктивные элементы.

Однако особенности технологии микроэлектроники, позволяющей получать групповым способом на одной подложке совокупность элементов с взаимосогласованными характеристиками, позволяли создать широкую номенклатуру аналоговых И С. Были разработаны типовые структуры, подобные интегральным логическим элементам в цифровых ИС, позволявшие унифицировать аналоговую микросхемотехнику. Рассмотрим некоторые классы аналоговых схем.

Генератор — микроэлектронное устройство, предназначенное для создания электрических колебаний заданной формы и частоты. В зависимости от формы формируемых колебаний различают генераторы гармоничных и релаксационных (импульсных) колебаний.

В зависимости от функционального назначения генераторы формируются в соответствующие интегральные схемы. Генераторы могут быть сформированы не только схемотехническими методами, но и с использованием приборов функциональной электроники. Так на диодах Ганна можно создать генераторы ВЧ- и СВЧ-колебаний.

Усилитель — микроэлектронное устройство, предназначенное для усиления сигналов в заданном диапазоне частот. Различают усилители постоянного тока, высокочастотные усилители, широкополосные, низкочастотные, усилители промежуточной частоты, видеоусилители, усилители считывания и воспроизведения.

Особое внимание, с точки зрения идеологии микроэлектроники, заслуживают дифференциальные и операционные усилители.

Детектор — микроэлектронное устройство, служащее для преобразования электрических колебаний, позволяющее выделять нужные составляющие амплитудно-частотных характеристик спектра сигналов. В частотном и фазовом детекторах частотно-модули- рованные и фазово-модулированные колебания преобразуются в амплитудно-модулированные колебания, которые затем детектируются.

Селектор импульсов представляет собой микроэлектронное устройство, предназначенное для выделения из множества импульсов только тех, которые обладают заданными свойствами. Например, амплитудные селекторы выделяют только те импульсы, амплитуда которых превышает заданный уровень или порог селекции. Может стоять и задача выделения импульсов, которые не достигают порога селекции. Схемы селекторов весьма разнообразны, создаются по микроэлектронной технологии в виде ИС.

Дата добавления: 2016-06-13; просмотров: 2411;