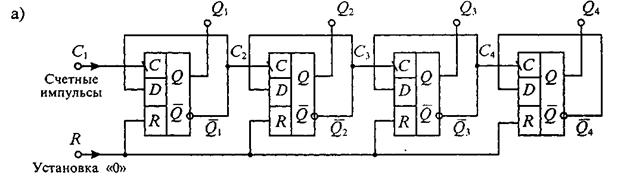

Состояния выходов четырехразрядного асинхронного двоичного счетчика

| n | Q4 | Q3 | Q2 | Q1 | n | Q4 | Q3 | Q2 | Q1 |

|

|

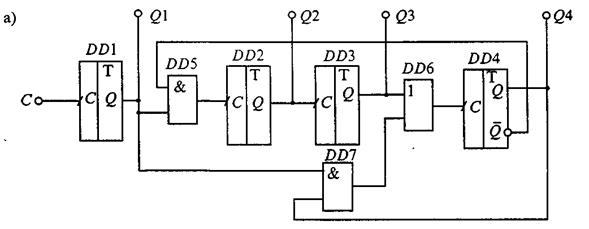

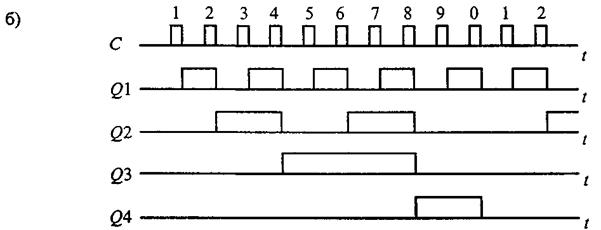

Рис. 14.2. Схема асинхронного суммирующего счетчика на D-триггерах (а), графики его выходных сигналов (б) и схема переноса (в)

переключения. Максимальную частоту имеет первый триггер, а частоты переключения каждого последующего триггера вдвое меньше. Поэтому в качестве первого триггера нужно использовать самый быстродействующий триггер, а быстродействие других триггеров может быть ниже. Для повышения быстродействия можно также использовать ускоренное формирование сигнала переноса между разрядами счетчика.

|

|

Рис. 14.3. Схемы одноразрядных синхронных счетчиков: суммирующего (а) и вычитающего (б)

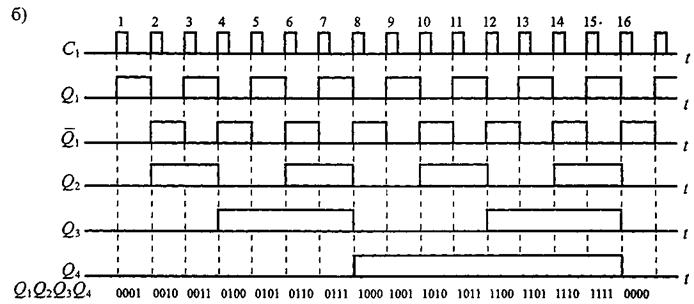

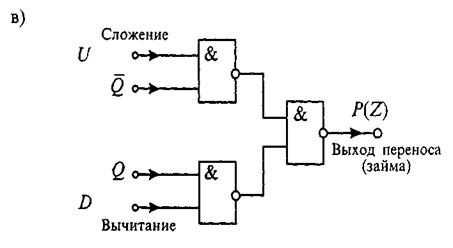

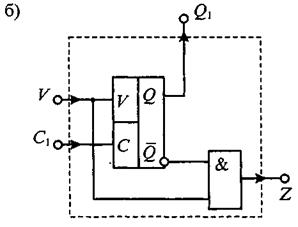

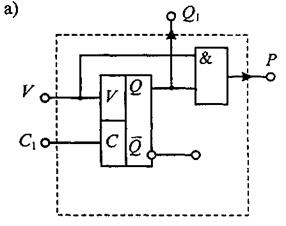

Синхронные счетчики. Для построения синхронных счетчиков используют различные типы счетных синхронных триггеров. Схемы одноразрядных синхронных счетчиков приведены на рис. 14.3. Эти схемы реализованы на синхронных счетных триггерах и логических элементах И для формирования сигналов переноса Р или займа Z. Схема одноразрядного синхронного суммирующего счетчика, приведенная на рис. 14.3 а, реализована подключением счетного входа С1 к счетному входу триггера, а для формирования сигнала переноса Р использовано логическое произведение сигнала разрешения счета V и выходного сигнала Q, т. е. Р=VQ. Переключение триггера происходит по положительному перепаду сигнала на входе С и при наличии сигнала разрешения на входе V. При этом на выходе триггера Q и выходе переноса Р устанавливаются уровни логической единицы. При отрицательном перепаде сигнала на входе С состояние триггера не изменяется. Очередное переключение триггера произойдет только по новому положительному перепаду импульса на входе С, при наличии сигнала разрешения на входе V. Таким образом, счетная ячейка обеспечивает синхронное деление на два частоты входных импульсов.

Синхронные счетчики. Для построения синхронных счетчиков используют различные типы счетных синхронных триггеров. Схемы одноразрядных синхронных счетчиков приведены на рис. 14.3. Эти схемы реализованы на синхронных счетных триггерах и логических элементах И для формирования сигналов переноса Р или займа Z. Схема одноразрядного синхронного суммирующего счетчика, приведенная на рис. 14.3 а, реализована подключением счетного входа С1 к счетному входу триггера, а для формирования сигнала переноса Р использовано логическое произведение сигнала разрешения счета V и выходного сигнала Q, т. е. Р=VQ. Переключение триггера происходит по положительному перепаду сигнала на входе С и при наличии сигнала разрешения на входе V. При этом на выходе триггера Q и выходе переноса Р устанавливаются уровни логической единицы. При отрицательном перепаде сигнала на входе С состояние триггера не изменяется. Очередное переключение триггера произойдет только по новому положительному перепаду импульса на входе С, при наличии сигнала разрешения на входе V. Таким образом, счетная ячейка обеспечивает синхронное деление на два частоты входных импульсов.

Двоичная вычитающая ячейка отличается от суммирующей тем, что прямой выход Q заменен на инверсный выход `Q. На выходе такой ячейки формируется сигнал займа Z =VQ.

Одноразрядный реверсивный счетчик реализуется по схеме, приведенной на рис. 14.4. Для изменения направления счета и формирования сигналов переноса или займа использована логическая схема 2И-ИЛИ. Для изменения направления счета введен специальный вход U/D (Up/Down): при U/`D =1 схема работает аналогично счетчику, изображенному на рис. 14.3 б, т. е.

является суммирующим счетчиком, а при U/`D = 0 она аналогична схеме, изображенной на рис. 14.3 б, т. е. переходит в режим вычитания. Использование этих ячеек позволяет реализовать многоразрядные синхронные счетчики.

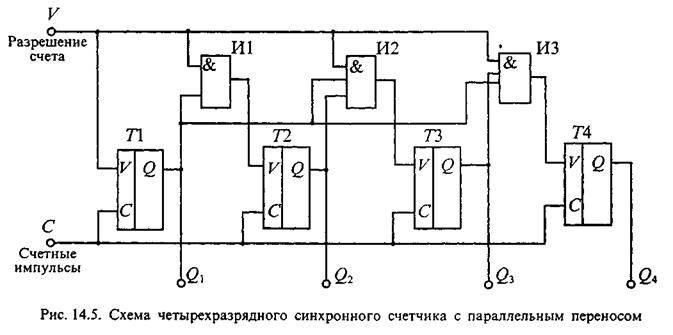

Схема четырехразрядного суммирующего двоичного синхронного счетчика с параллельным переносом приведена на рис. 14.5. Она отличается от счетчиков с каскадным соединением разрядов тем, что счетные импульсы поступают на тактовые входы С всех триггеров счетчика одновременно. При этом сигналы разрешения счета формируются в логических элементах И как произведение сигнала разрешения счета V и сигналов Q с прямых выходов всех предыдущих триггеров.

Быстродействие счетчиков с параллельным переносом выше быстродействия декадных счетчиков. Минимальный период следования синхроимпульсов определяется суммой

Tсч= tт + tл (14.2)

где tт — время задержки триггера, tл — время задержки логической схемы. По сравнению с последовательным счетчиком максимальная частота счета параллельного счетчика увеличивается примерно в (n-1) раз и не зависит от числа каскадов. В некоторых случаях функцию логических элементов можно реализовать на внутренних элементах триггера, тогда можно считать, что tл= 0 и быстродействие счетчика зависит только от задержки триггера, т. е. Tсч = tт.

Регистры сдвига. Триггерным регистром сдвига называют совокупность триггеров с определенными связями между ними, при которых они действуют как единое устройство. В регистрах сдвига организация этих связей такова, что при подаче тактового импульса, общего для всех триггеров, выходное состояние каждого триггера сдвигается в соседний. В зависимости от организации связей этот сдвиг может происходить влево или вправо:

Q2®Q1, Q3®Q2, Q4®Q3, ... , Qn®Qn-1 — сдвиг влево,

Q1®Q2, Q2®Q3, Q3®Q4, ... , Qn-1®Qn— сдвиг вправо.

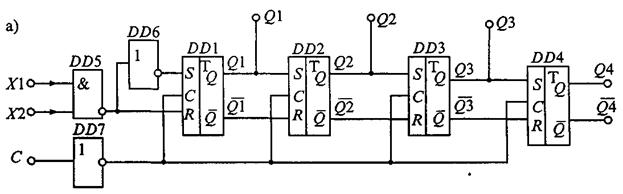

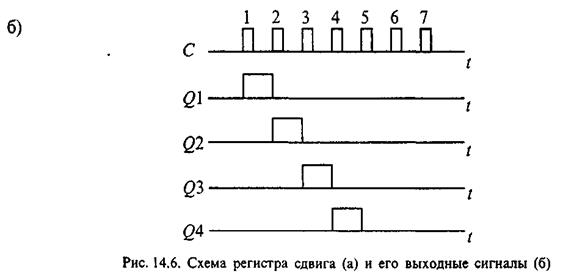

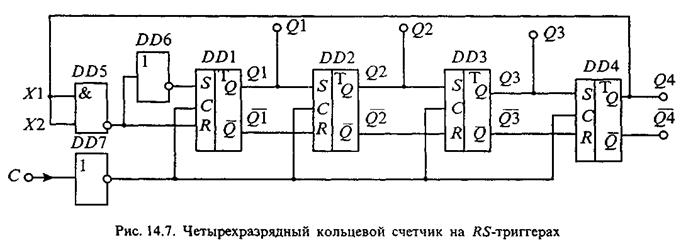

Ввод информации в регистр может выполняться различными способами, однако наиболее часто используют параллельный или последовательный ввод, при которых ввод двоичного ч исла осуществляется или одновременно во все разряды регистра, или последовательно во времени по отдельным разрядам. В счетчиках импульсов находят применение сдвигающие регистры с последовательным вводом и выводом и со сдвигом вправо. На рис. 14.6 а приведена схема четырехразрядного регистра сдвига, выполненного на RS-триггерах. В этой схеме каждый выход Q триггера соединен со входом S последующего разряда, а каждый выход`Q — с входом R. Тактовые входы всех триггеров соединены вместе, и поступление сигнала синхронизации осуществляется одним общим импульсом через логический элемент И-НЕ (DD7). Состояние первого триггера определяется входными сигналами на входах XI и X2 логического элемента И-НЕ (DD5). На вход X1 подается текущая информация, а на вход Х2 сигнал разрешения ее передачи. Логические элемент НЕ (DD6) используется для инвертирования входного сигнала, подаваемого на вход S.

На рис.14.6 б приведены временные диаграммы выходных сигналов триггеров, а в табл. 14.2 ― состояния регистра сдвига при записи в первый разряд регистра единичного сигнала. Если при поступлении первого тактового импульса на входах X1 и X2 установлены сигналы Х1=Х2=1, которые затем снимаются к приходу второго тактового импульса, то в результате в первый триггер будет записан сигнал Q1=1. С приходом второго тактового импульса в первый триггер

Таблица 14.2

Состояние выходов четырехразрядного

счетчика Джонсона

| п | Q 1 | Q2 | Q3 | Q4 |

будет записан сигнал Q1=0, а на выходе второго триггера появит-ся сигнал Q2=1, который перед этим был на выходе первого триггера. При поступлении последующих тактовых импульсов единичный сигнал перемещается последовательно в третий и четвертый триггеры, после чего все триггеры устанавливаются в нулевое состояние.

Сдвиговые регистры можно реализовать также на D-триггерах или JK-триггерах. Для всех регистров сдвига характерны следующие положения: 1) необходима предварительная установка исходного состояние и ввод единицы в первый триггер и 2) для регистра из п триггеров после поступления п входных тактовых импульсов первоначально введенная единица выводится, вследствие чего прямые выходы всех регистров оказывается в нулевом состоянии.

Интегральные микросхемы регистров сдвига бывают реверсивными, т. е. выполнящими сдвиг в любом направлении: вправо или влево. Направление сдвига определяется значением управляющего сигнала. Регистры сдвига применяют в качестве запоминающих устройств, в качестве преобразователей последовательного кода в параллельный, в качестве устройств задержки и счетчиков импульсов.

Применение регистров сдвига в качестве счетчиков очень неэкономично, так как модуль счета Кс=п, в то время как для двоичных счетчиков Кс = 2n.

Кольцевые счетчики. Распространенной разновидностью параллельных счетчиков являются кольцевые счетчики, выполненные на базе регистров сдвига. Простейшая схема кольцевого счетчика получается при замыкании прямого выхода регистра сдвига с его входом. В таком счетчике единица, записанная в регистр на первом такте, с выхода Qn счетчика снова попадает на его вход и далее весь цикл повторяется. Модуль счета такого кольцевого счетчика имеет то же значение,

|

что и регистр сдвига, т. е. Кс=п. Для увеличения модуля счета можно или увеличивать количество триггеров в кольце, или включать счетчики последовательно. Так, например, счетчик на 10 импульсов (KС=10) можно реализовать последовательным соединением одного счетного триггера и кольцевого счетчика из пяти триггеров.

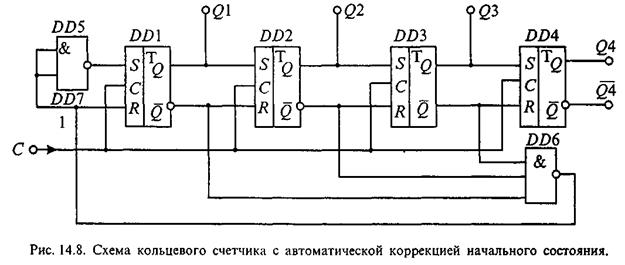

Основным недостатком кольцевых счетчиков является их низкая помехозащищенность. Например, если под действием помехи исчезнет записанная в счетчик единица, то все триггеры окажутся в нулевом состоянии и счетчик работать не сможет. Для устранения подобных сбоев используются различные способы коррекции состояния счетчика. Схема счетчика с автоматической коррекцией состояния приведена на рис. 14.8. В этой схеме независимо от того, в каком состоянии после включения окажутся триггеры, после четырех тактовых импульсов на входе С установится требуемое выходное состояние (1 0 0 0).

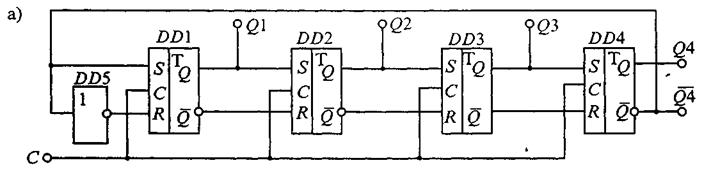

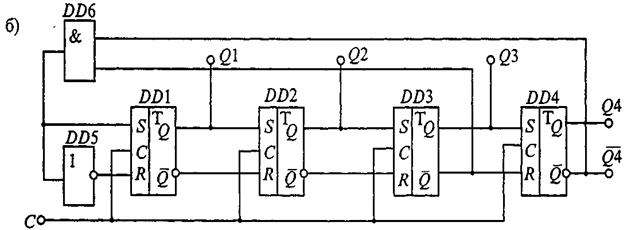

Счетчики Джонсона. Разновидностью кольцевых счетчиков являются счетчики Джонсона. В этих счетчиках вход регистра соединен не с выходом Q, а с инверсным выходом `Q . . В результате, когда на вход счетчика поступают тактовые импульсы, то вначале все разряды счетчика заполняются единицами, а затем — нулями. Схема четырехразрядного счетчика Джонсона приведена на рис. 14.9, а состояние его выходов приведено в табл. 14.3.

Таблица 14.3

Состояние выходов четырехразрядного счетчика Джонсона

| n | Q4 | Q3 | Q2 | Q1 | n | Q4 | Q3 | Q2 | Q1 |

Как следует из табл. 14.3, модуль счета счетчика Джонсона в два раза больше модуля счета простого кольцевого счетчика, т. е. Кс = 2n. В счетчике Джонсона, как и в других кольцевых счетчиках, могут быть сбои, вызванные помехами. Для коррекции нарушений, вызванных сбоями, также используются способы, с помощью которых производится переход из любой запрещенной комбинации в одну из разрешенных.

Счетчики Джонсона широко используются в делителях частоты импульсов, генераторах случайных чисел, в устройствах памяти и др. На базе счетчика Джонсона можно легко реализовать счетчики с любым четным модулем счета. При необходимости иметь нечетное значение модуля счета можно на вход первого разряда подавать вместо сигнала `Qn сигнал `Qn` Q n-1 как показано на рис. 14.9 б. При этом из набора выходных состояний счетчика Джонсона исключается одна кодовая комбинация, составленная из нулей.

Двоично-десятичные, или декадные счетчики могут быть реализованы на базе двоичных счетчиков при помощи взаимной связи между отдельными триггерами, входящими в счетчик. Схема декадного счетчика, построенная на базе рассмотренного ранее четырехразрядного двоичного счетчика (рис. 14.2), изображена на рис. 14.10 а. В этом счетчике взаимные соединения триггеров выполнены так, что первые девять счетных импульсов повторяют выходные сигналы триггеров для двоичного счетчика. Последний счетный импульс возвращает счетчик в исходное состояние. Сигналы на выходах такого триггера приведены на рис. 14.10 б.

Рис. 14.9. Схема четырехразрядного счетчика Джонсона с четным (а) и нечетным (б)

модулем счета

Рис. 14.10. Схема декадного счетчика на счетных триггерах (а) и сигналы на его выходах (б)

Как следует из временной диаграммы, сигналы на выходах счетчика для девяти импульсов совпадают с временной диаграммой, приведенной на рис. 14.2 в. Однако десятый импульс, вместо того чтобы установить счетчик в состояние 1010, как у двоичного счетчика, через дополнительные элементы и обратные связи возвращает четвертый триггер в нулевое состояние (Q4=0) и препятствует установке второго триггера в единичное состояние, сохраняя его нулевое состояние (Q2=0). В результате после десяти импульсов состояние декадного счетчика будет такое же, как и до начала счета.

Это обеспечивается блокированием второго, а значит, и третьего триггера через элемент DD5с выхода DD4 , а также переключением триггера DD4 через элементы DD6 и DD7 отрицательным перепадом с выхода Q1. Выходные состояния декадного счетчика приведены в табл. 14.4. Такой десятичный счетчик обозначают как «8 + 2», поскольку выход Q4 сохраняет нулевое состояние на протяжении первых восьми входных пульсов и переключается в единичное состояние во время действия двух последних импульсов. К таким счетчикам относятся многие интегральные десятичные счетчики, такие как К155ИЕ2 и др.

Подобным образом можно сформировать счетчик с любым модулем счета Кс. Если используется счетчик из п триггеров на 2n возможных состояний, то за счет

Таблица 14.4

Состояние выходов десятичного счетчика

| n | Q4 | Q3 | Q2 | Q1 | n | Q4 | Q3 | Q2 | Q1 |

Дата добавления: 2016-04-06; просмотров: 5513;