Состояние входов и выходов приоритетного шифратора К555ИВ1

| Е | X7 | Х6 | X5 | X4 | Х3 | Х2 | X1 | Х0 | Y2 | Y1 | Y0 | G | ЕО |

| x | x | x | x | x | x | x | x | ||||||

| x | |||||||||||||

| x | x | ||||||||||||

| x | x | x | |||||||||||

| x | x | x | x | ||||||||||

| x | x | x | x | x | |||||||||

| x | x | x | x | x | x | ||||||||

| x | x | x | x | x | x | x |

Примечание: х = 0 или 1

К555ИВ1 форматом 16x4 приведена на рис. 15.4 б. В этой схеме наивысший приоритет имеет вход X15. Первый шифратор (верхний по схеме) включается только в том случае, если не возбужден ни один вход второго (нижнего) шифратора. Сигнал G=l, если возбужден хотя бы один вход Х0...Х15.

Аналогично функционирует приоритетный шифратор К555ИВ2, отличительной особенностью которого является наличие выходов с тремя состояниями, что

Аналогично функционирует приоритетный шифратор К555ИВ2, отличительной особенностью которого является наличие выходов с тремя состояниями, что

Рис. 15.4. Условное схематичное изображение шифратора К555ИВ1 (а) и расширенный шифратор форматом 16x4 (б)

облегчает каскадирование шифраторов. Другой приоритетный шифратор К555ИВЗ имеет формат 10x4 и функционирует аналогично предыдущему.

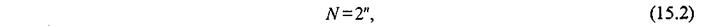

Дешифратором называют преобразователь двоичного n-разрядного кода в унитарный 2x-разрядный код, все разряды которого, за исключением одного, равны нулю. Дешифраторы бывают полные и неполные. Для полного дешифратора выполняется условие:

где п — число входов, а N — число выходов.

В неполных дешифраторах имеется п входов, но реализуется  выходов. Так, например, дешифратор, имеющий 4 входа и 10 выходов будет неполным, а дешифратор, имеющий 2 входа и 4 выхода, будет полным.

выходов. Так, например, дешифратор, имеющий 4 входа и 10 выходов будет неполным, а дешифратор, имеющий 2 входа и 4 выхода, будет полным.

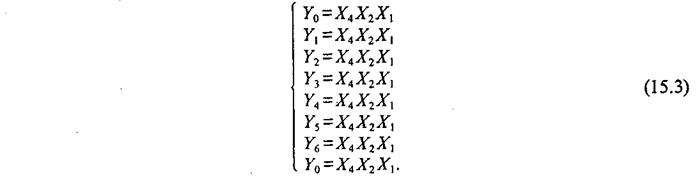

Рассмотрим принцип построения дешифратора на примере преобразования трехразрядного двоичного кода в унитарный код. Если считать, что входы и выходы упорядочены по возрастающим номерам, т. е. считать, что коду 000 соответствует выход  коду 001 — выход

коду 001 — выход  и т. д., то для полного дешифратора можно записать восемь упорядоченных уравнений:

и т. д., то для полного дешифратора можно записать восемь упорядоченных уравнений:

Реализовать восемь уравнений (15.3) можно с помощью восьми трехвходовых элементов И. Полученная схема дешифратора приведена на рис. 15.5 а, а его условное схематичное изображение приведено на рис. 15.55.

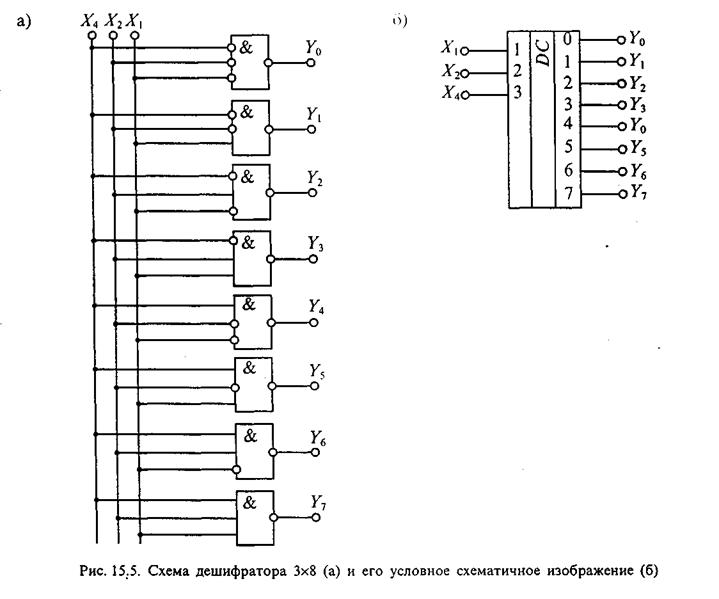

Для расширения числа входов и выходов используют каскадное включение дешифраторов. На рис. 15.6 показана группа из пяти дешифраторов, соединенних последовательно в два каскада. Все дешифраторы одинаковые. Кроме кодовых входов каждый дешифратор имеет вход стробирующего сигнала (вход С). Сигнал на выходе дешифратора появляется только при С=1. Если С=0, то на всех выходах дешифратора будут нули, т. е. дешифратор заперт.

На входы первого дешифратора DD1 подаются старшие разряды  и

и  числа, которое нужно дешифрировать. Таким образом, дешифратор DD1 определяет, какой из четырех дешифраторов DD2...DD5 из подключенных к нему будет выполнять дешифрирование младших разрядов числа. Выходные сигналы первого дешифратора подключены к стробирующим входам С остальных и разрешают их работу.

числа, которое нужно дешифрировать. Таким образом, дешифратор DD1 определяет, какой из четырех дешифраторов DD2...DD5 из подключенных к нему будет выполнять дешифрирование младших разрядов числа. Выходные сигналы первого дешифратора подключены к стробирующим входам С остальных и разрешают их работу.

Младшие разряды дешифрируемого числа  и

и  подаются на входы дешифраторов DD2...DD5. Однако выполнять дешифрирование этих разрядов будет только тот дешифратор, который включен сигналом, поданным на вход С от дешифратора старших разрядов.

подаются на входы дешифраторов DD2...DD5. Однако выполнять дешифрирование этих разрядов будет только тот дешифратор, который включен сигналом, поданным на вход С от дешифратора старших разрядов.

Так, например, при дешифрировании числа 1001 на вход поступает код 10, которым возбуждается выход 2. В этом случае включается дешифратор DD4 , на вход которого подан код 01 младших разрядов дешифрируемого числа. В результате будет возбужден выход 1 дешифратора DD4, при этом на выходе появится сигнал 79, что соответствует выбранному входному коду.

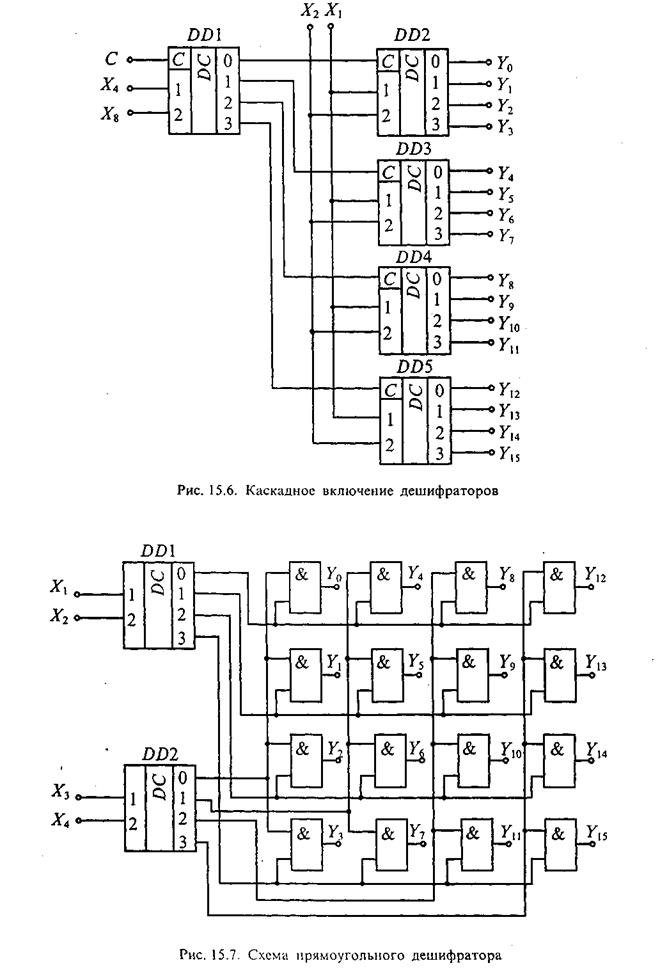

Для расширения числа входов и выходов дешифраторов можно также воспользоваться параллельным или прямоугольным дешифратором, схема которого приведена на рис. 15.7. Схема прямоугольного дешифратора состоит из двух ступеней. Первая ступень состоит из двух дешифраторов DD1 и DD2, первый из которых дешифрует младшие разряды  и Хг входного числа, а второй - старшие разряды

и Хг входного числа, а второй - старшие разряды  и Х4. Вторая ступень состоит из TV элементов 2И-НЕ. Все элементы 2И-НЕ разделены на строки и столбцы: строками управляет дешифратор первой ступени на DD1, а столбцами управляет дешифратор DD2. Схема, приведенная на рис. 15.7, соответствует полному дешифратору. Если исключить некоторые из элементов 2И-НЕ, то получим неполный дешифратор с уменьшенным числом выходов.

и Х4. Вторая ступень состоит из TV элементов 2И-НЕ. Все элементы 2И-НЕ разделены на строки и столбцы: строками управляет дешифратор первой ступени на DD1, а столбцами управляет дешифратор DD2. Схема, приведенная на рис. 15.7, соответствует полному дешифратору. Если исключить некоторые из элементов 2И-НЕ, то получим неполный дешифратор с уменьшенным числом выходов.

|

Интегральные микросхемы преобразователей кодов, шифраторов и дешифраторов.Промышленность выпускает большое количество различных микросхем преобразователей кодов, шифраторов и дешифраторов, некоторые из которых приведены в табл. 15.3.

Таблица 15.3

Дата добавления: 2016-04-06; просмотров: 2657;