Обратных связей с дополнительными логическими элементами можно получить любое значение Кс<2n.

Интегральные микросхемы счетчиков. Промышленность выпускает большое количество интегральных микросхем счетчиков, построенных на транзисторно-транзисторной логике (ТТЛ), эмиттерно-связанной логике (ЭСЛ) и комплементарных полевых транзисторах (КМОП). В табл. 14.5 приведены основные типы счетчиков различных серий интегральных микросхем. Условное обозначение интегральных микросхем счетчиков состоит из обозначения серии (трех или четырех цифр), функционального назначения (двух букв ИЕ) и порядкового номера разработки (от одной до трех цифр).

Основные параметры интегральных микросхем счетчиков можно разделить на две группы: статические и динамические. К статическим параметрам относятся входное напряжение высокого U1вх и низкого U0вх уровней, ток потребления от источника питания, напряжение питания, коэффициент разветвления Краз и модуль счета Кс. К динамическим параметрам счетчиков относятся: время t0,1 переключения из низкого уровня в высокий, время переключения t1,0 из высокого уровня в

Таблица 14.5

Параметры интегральных микросхем счетчиков импульсов

| Наименование счетчика | Тип логики | Функциональное назначение | Модуль счета Кс | Максимальная частота fмакс, МГц |

| К155ИЕ5 | ТТЛ | Асинхронный двоичный | ||

| К555ИЕ18 | ТТЛШ | Синхронный двоичный | ||

| К155ИЕ7 | ТТЛ | Реверсивный двоичный | ||

| К561ИЕ8 | КМОП | Счетчик Джонсона с дешифратором | ||

| К561ИЕ11 | КМОП | Двоичный реверсивный | ||

| К500ИЕ137 | ЭСЛ | Синхронный реверсивный десятичный |

Таблица 14.6

Параметры интегральных микросхем регистров

| Наименование регистра | Тип логики | Функциональное назначение | Максимальная тактовая частота, МГц |

| К155ИР1 | ТТЛ | Четырехразрядный сдвиговой | |

| К155ИР13 | ТТЛ | Универсальный восьмиразрядный синхронный сдвиговой | |

| К531ИР11 | ТТЛШ | Четырехразрядный сдвиговой | |

| К561ИР9 | КМОП | Четырехразрядный последовательно-параллельный | |

| К500ИР141 | ЭЛС | Универсальный четырехразрядный сдвиговой |

низкий и максимальная частота счета fмакс. Большинство перечисленных параметров определяется серией микросхем и типом применяемой логики.

Интегральные микросхемы регистров. В наименовании регистров их функциональное назначение обозначается буквами ИР. В остальном условное обозначение регистров совпадает с обозначением счетчиков. В табл. 14.6 приведены некоторые типы регистров различных серий.

Лекция 15. Преобразователи кодов, шифраторы и дешифраторы

Преобразователи кодов. Операция изменения кода числа называется его перекодированием. Интегральные микросхемы, выполняющие эти операции, называются преобразователями кодов. Преобразователи кодов бывают простые и сложные. К простым относятся преобразователи, которые выполняют стандартные операции изменения кода чисел, например, преобразований двоичного кода в одинарный или обратную операцию. Сложные преобразователи кодов выполняют нестандартные преобразования кодов и их схемы приходится разрабатывать каждый раз с помощью алгебры логики.

Будем считать, что преобразователи кодов имеют п входов и k выходов. Соотношения между п и k могут быть любыми: n = k, n<k и n>k. При преобразовании кода чисел с ними могут выполняться различные дополнительные операции, например, умножение на весовые коэффициенты. Примером невесового преобразования является преобразование двоично-десятичного кода в двоичный. Весовые преобразователи кодов используются при преобразовании числовой информации.

Интегральные микросхемы преобразователей кодов выпускаются только для наиболее распространенных операций:

· преобразователи двоично-десятичного кода в двоичный код;

· преобразователи двоичного кода в двоично-десятичный код;

· преобразователи двоичного кода в код Грея;

· преобразователи двоичного кода в код управления сегментными индикаторами;

· преобразователи двоичного или двоично-десятичного кода в код управле ния шкальными или матричными индикаторами.

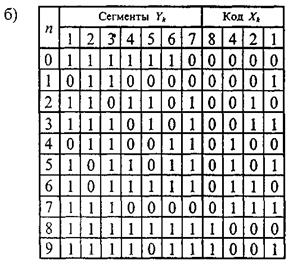

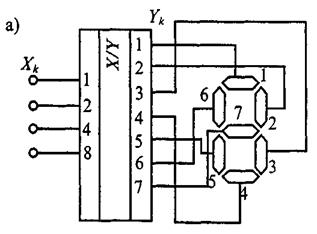

В качестве примера рассмотрим преобразователь двоичного кода в код управления семисегментным цифровым индикатором, приведенный на рис. 15.1 а. Сам индикатор представляет собой полупроводниковый прибор, в котором имеются семь сегментов, выполненных из светодиодов. Включением и выключением отдельных сегментов можно получить светящееся изображение отдельных цифр или знаков. Конфигурация и расположение сегментов индикатора показаны на рис. 15.1 а. Каждой цифре соответствует свой набор включения определенных сегментов индикатора. Соответствующая таблица приведена на рис. 15.1 б. В этой таблице также приведены двоичные коды соответствующих цифр.

Такие индикаторы позволяют получить светящееся изображение не только цифр от 0 до 9, но других знаков, используемых в 8- и 16-ричной системах счисления. Для управления такими индикаторами выпускаются интегральные микросхемы типов КР514ИД1, К514ИД2, К133ПП1, 176ИД2, 176ИДЗ, 564ИД4, 564ИД5 и др. Преобразователи кодов, выполненные по технологии КМОП, можно использовать не только со светодиодными индикаторами, но и с жидкокристаллическими или катодолюминисцентными.

Шкальные индикаторы представляют собой линейку светодиодов с одним общим анодом или катодом. Преобразователи двоичного кода в код управления

|

|

Рис. 15.1Схема преобразователя кода для семисегментного индикатора (а) и таблица соотвествия кодов (б)

шкальным индикатором обеспечивают перемещение светящегося пятна, опре деляемое двоичным кодом на адресном входе.

Матричные индикаторы представляют собой наборы светодиодов, расположенных по строкам и столбцам. Наиболее распространенными матричними индикаторами являются индикаторы, имеющие 5 столбцов и 7 строк (формат 5x7). Количество светодиодов в таких матричных индикаторах равно 35. Управление такими индикаторами производится путем выбора номера строки и номера столбца, на пересечении которых находится нужный светодиод. Примером такого матричного индикатора является прибор АЛС340А с форматом 5x7 светодиодов (рис. 15.2 а).

Для управления матричными индикаторами выпускаются микросхемы, в которых положение светодиода задается номерами столбца i и строки j, причем не все комбинации i и j используются. Такие преобразователи кодов называются неполными. К ним относятся микросхемы К155ИД8 и К155ИД9 (рис. 15.2 б).

Примерами простейших преобразователей кодов, которые широко применяются в цифровых устройствах, являются шифраторы и дешифраторы.

Шифратором называют кодовый преобразователь, который имеет п входов и k выходов, и при подаче сигнала на один из входов (обязательно только на один) на выходах появляется двоичный код возбужденного входа. Очевидно, что число выходов и входов в полном шифраторе связано соотношением

n =2k. (15.1)

Рассмотрим принцип построения шифратора на примере преобразования 8-разрядного единичного кода в двоичный код. Схема такого шифратора приведена на рис. 15.3 а, а его условное схематичное обозначение — на рис. 15.3 б. Если все входные сигналы имеют нулевое значение, то на выходе шифратора будем иметь нулевой код Y0=Y1 = Y2 = 0.

Младший выход, т. е. выход с весовым коэффициентом, равным 1, должен возбуждаться при входном сигнале на любом из нечетных входов, так как все

Рис. 15.2. Устройство матричного индикатора формата 7x5 (а) и включение микросхемы К155ИД9 неполного дешифратора матричного индикатора (б)

Рис. 15.3. Схема шифратора восьмиразрядного единичного кода (а) и его условное схематическое

бозначение (б)

нечетные номера в двоичном представлении содержат единицу в младшем разряде. Следовательно, младший выход — это выход схемы ИЛИ, к входам которой подключены все входы с нечетными номерами.

Следующий выход имеет вес два. Он должен возбуждаться при подаче сигналов на входы с номерами 2, 3, 6, 7, т. е. с номерами, имеющими в двоичном представлении единицу во втором разряде. Таким образом, входы элемента ИЛИ должны быть подключены к входным сигналам, имеющим указанные номера.

Старший разряд двоичного кода формируется из входных сигналов с номерами 4, 5, 6 и 7, т. е. из четырех старших разрядов единичного кода. Все рассмотренные состояния шифратора можно увидеть в таблице, приведенной на рис. 15.1 б.

Как следует из выполненного построения, при помощи шифратора можно сократить (сжать) информацию для передачи ее по меньшему числу линий связи, так как k<n. Обратное преобразование, т. е. восстановление информации в первоначальном виде можно выполнить с помощью дешифратора. Очевидно, что максимальное число входов шифратора не может превышать количество возможных комбинаций выходных сигналов, т. е. необходимо выполнение условия n£2k (см. уравнение (15.1) для полного шифратора).

В цифровых системах с помощью шифраторов обеспечивается связь между различными устройствами посредством ограниченного числа линий связи. Так, например, в кнопочных пультах управления ввод числовых данных обычно выполняется в унитарном коде посредством нажатия одной из десяти кнопок, а ввод

данных в микропроцессор выполняется в двоичном коде. Для преобразования кода кнопочного пульта в код микропроцессора также используется шифратор «из 10 в 4». Однако, поскольку четырехразрядный двоичный код имеет не 10, а 16 возможных комбинаций, такой шифратор будет неполным.

Состояние выходов шифратора, изображенного на рис. 15.3 а, приведено в табл. 15.1. Из этой таблицы следует, что для шифраторов должно выполняться условие xixj=0при i¹j.

Если сигналы, поступающие на вход шифратора, являются независимыми, что бывает, например, при нажатии одновременно нескольких кнопок на кнопочном пульте управления, то условие хiхj = 0не выполняется. В этом случае каждому входу xi шифратора назначают свой приоритет. Обычно считают, что чем выше номер входа, тем выше его приоритет. В этом случае шифратор должен выдавать на выходе двоичный код числа i, если хi=1, а на все входы xj, имеющие больший приоритет, поданы нули. Такие шифраторы называются приоритетными, например, если на входе шифратора установлен код 0011, то на выходе будет код 01.

В качестве примера рассмотрим функционирование приоритетного шифратора К555ИВ1. Функционирование этого шифратора описывается табл. 15.2.

Условное схематическое изображение шифратора К555ИВ1 приведено на рис. 15.4 а. Назначение сигналов на входе шифратора: Е — сигнал включения шифратора (0 — выключен, 1 — включен). Сигналы на выходе: G — сигнал, свидетельствующий о наличии хотя бы одного возбужденного входа xi при включенном состоянии шифратора (G=1 при xi= 1, хотя бы для одного i при E=1); ЕО— сигнал разрешения, свидетельствующий об отсутствии возбужденных входов xiпри включенном состоянии шифратора (ЕО = 1 при Е=1 и хi = 0 для всех i). Таким образом, трехразрядный двоичный код можно считывать с выхода шифратора только при условии, что G=1. Выходной сигнал ЕО можно использовать при каскадном включении шифраторов. Схема расширенного шифратора на ИМС

Таблица 15.1

Состояния выходов шифратора 8x3

| X7 | Х6 | Х5 | X4 | X3 | X2 | X1 | X0 | Y2 | Y1 | Y0 |

| 0. | ||||||||||

Таблица 15.2

Дата добавления: 2016-04-06; просмотров: 1299;