Основные параметры ИМС КМОП

| Серия ИМС | Потребляемая мощность, мВт | Задержка распространения, нс | Максимальная частота, МГц | Коэффициент разветвления |

| CD4000 | ||||

| CD4000A | ||||

| CD4000B | ||||

| 54НС |

· повышенное выходное сопротивление (до 1 кОм);

· значительный разброс всех параметров.

Уровни выходных сигналов зависят от напряжения питания. Уровень логической «1» равен примерно 0,8Eпит, а уровень логического «0» — от 0,3 до 2,5В. Основные характеристики различных серий ИМС КМОП приведены в табл. 12.6.

Совершенствование технологии ИМС КМОП привело в настоящее время к тому, что характеристики наиболее быстродействующих ИМС КМОП серии 54НС практически сравнялись с характеристиками ИМС ТТЛ серии SN74LS.

Лекция 13. Триггеры

Основные сведения. Триггерами называют большой класс электронных устройств, обладающих способностью длительно находиться в одном из двух или более устойчивых состояний и чередовать их под воздействием внешних сигналов. В отличие от комбинационных логических схем, триггеры — это логические устройства с памятью. Их выходные сигналы в общем случае зависят не только от сигналов, приложенных к входам в данный момент времени, но и от сигналов, воздействовавших на них ранее. В зависимости от свойств, числа и назначения входов триггеры можно разделить на несколько видов.

Виды триггеров. Триггер Т(рис. 13.1) можно представить в общем случае как устройство, состоящее из ячейки памяти ЯП и логического устройства ЛУ управления, преобразующего входную информацию в комбинацию сигналов, под воздействием которых ЯП принимает одно из двух устойчивых состояний.

Информационные сигналы поступают на входы А и В ЛУ и преобразуются в сигналы, поступающие на внутренние входы S' и R' ЯП. Процесс преобразования информационных сигналов осуществляется при воздействии сигналов, подаваемых на вход Т предустановки и вход С синхронизации. Вход Т обычно используется для разрешения приема информации, а исполнительный вход С обеспечивает тактируемый прием информации. В простейшем триггере ЛУ может отсутствовать, а информационные сигналы подаются непосредственно на входы S и R ЯП.

Информационные сигналы поступают на входы А и В ЛУ и преобразуются в сигналы, поступающие на внутренние входы S' и R' ЯП. Процесс преобразования информационных сигналов осуществляется при воздействии сигналов, подаваемых на вход Т предустановки и вход С синхронизации. Вход Т обычно используется для разрешения приема информации, а исполнительный вход С обеспечивает тактируемый прием информации. В простейшем триггере ЛУ может отсутствовать, а информационные сигналы подаются непосредственно на входы S и R ЯП.

При наличии входа С триггер называют синхронным, а при его отсутствии — асинхронным.

Изменение состояния асинхронного триггера происходит сразу же после соответствующего изменения потенциалов на его информационных входах А и В. В синхронном триггере изменение состояния может произойти только в момент присутствия соответствующего сигнала на входе С. Синхронизация может осуществляться импульсом (потенциалом) или фронтом (перепадом потенциала). В первом случае сигналы на информационных входах оказывают влияние на состояние триггера только при разрешающем потенциале на входе С. Во втором случае воздействие информационных сигналов проявляется только в момент изменения потенциала на входе С, т. е. при переходе его от 1 к 0 или от 0 к 1. Универсальные триггеры могут работать как в синхронном, так и в асинхронном режимах.

Основные типы триггеров в интегральном исполнении получили следующие названия: SR-триггер, JK-триггер, D-триггер, T-триггер.

SR-триггер имеет два информационных входа S и R. Подача на вход S сигнала 1, а на вход R сигнала 0 устанавливает на выходе Q триггера сигнал 1. Наоборот, при сигналах S=0 и R = 1 сигнал на выходе триггера Q = 0. Функционирование SR-триггера определяется уравнениями:

Qn = (S+`RQ)n -1 ; SR = 0.

Для SR-триггера комбинация S= 1 и R= 1 является запрещенной. После такой комбинации информационных сигналов состояние триггера будет неопределенным: на его выходе Q может быть 0 или 1.

Существуют разновидности SR-триггеров, называемые Е-, R- и .S-триггерами, для которых сочетание S=R=1не является запрещенным. E-триггер при S=R =1не изменяет своего состояния (Qn= Qn-1). S-триггер при S=R =1 устанавливается в состояние Q=1, а R-триггер в этом случае устанавливается в состояние Q = 0.

SR-триггеры могут быть асинхронными или синхронными (в этом случае у них имеется вход С).

JK-триггер имеет также два информационных входа J и К. Подобно SR-триггеру, в JK-триггере J и К — это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от SR-триггера, в JK-триггере наличие J=K=1 приводит к переходу выхода Q триггера в противоположное состояние. JK-триггеры синхронизируются только перепадом потенциала на входе С. Условие функционирования JK-триггера имеет вид:

Qn=(JQ + KQ)n-1

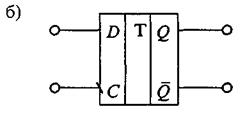

D-триггер, или триггер задержки, при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D. Уравнение функционирования. D-триггера имеет вид: Qn =Dn-1 . Это уравнение показывает, что выходной сигнал Qn изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, т. е. с задержкой на один период импульсов синхронизации (Delay — задержка).

Синхронизация D-триггера может осуществляться импульсом или фронтом.

Т-триггер, или счетный триггер, изменяет состояние выхода по фронту импульса на входе С. Кроме синхровхода С T-триггер может иметь подготовительный вход Т. Сигнал на этом входе разрешает (при T=1) или запрещает (при T=0) срабатывание триггера от фронтов импульсов на входе С. Функционирование T-триггера определяется уравнением: Qn=(`QT+`QT)n-1. Из этого уравнения

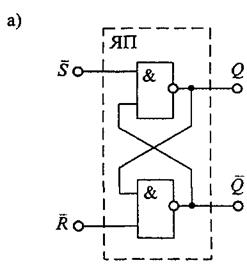

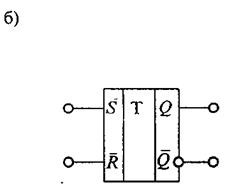

Рис. 13.2. Асинхронный SR-триггер (а) и его условное схематическое обозначение (б)

следует, что при Т=1 соответствующий фронт сигнала на входе С переводит триггер в противоположное состояние. Частота изменения потенциала на выходе T-триггера в два раза меньше частоты импульсов на входе С. Это свойство T-триггера позволяет строить на их основе двоичные счетчики. Поэтому эти триггеры и называют счетными. Счетный триггер без входа Т ведет себя так же, как и T-триггер при Т=1.

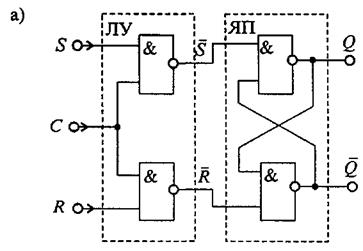

Принципы построения триггеров.Простейший асинхронный SR-триггер состоит из двух ячеек И-НЕ (или ИЛИ-НЕ), замкнутых в кольцо (рис. 13.2a), и по существу представляет ЯП без дополнительного ЛУ. Аналогичный SR-триггер в интегральном исполнении изображен на рис. 13.2 б. Переключение SR-триггеров, изображенных на рис. 13.2, производится сигналом «0», подаваемым на входы S или R . Такие простейшие триггеры входят во все типы более сложных триггеров. Простейший синхронный SR-триггер содержит кроме ЯП еще ЛУ из двух ячеек И-НЕ (рис. 13.3 а).

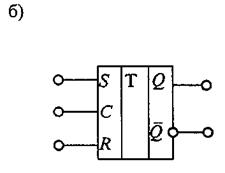

Аналогичный SR-триггер в интегральном исполнении изображен на рис. 13.3 б. Переключение SR-триггеров, изображенных на рис. 13.3,

|

|

Рис. 13.3. Синхронный SR-триггер (а) и его условное схематическое обозначение (б)

производится сигналом «1», подаваемым на входы S или R, или только при наличии синхросигнала С=1.

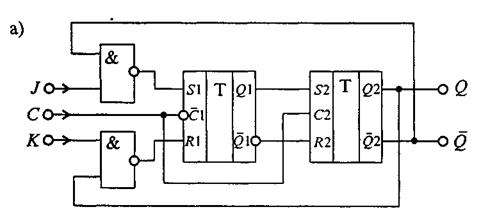

JK-триггер выполняется по двухступенчатой структуре, состоящей из двух синхронных SR-триггеров и двух логических схем И-НЕ (рис. 13.4 а) . Для этой схемы S1=JQ и R1 = KQ. Если J= 1 и К=0, то при Q = 0 получим S1 = 1, и после окончания первого тактового импульса на входе С триггер установится в состояние Q=1.

Если J= 1 и К=0, то при Q= 1 оба входных сигнала триггера первой ступени S1и R1будут равны «0» и, соответственно, весь двухступенчатый триггер не будет изменять своего состояния при приходе синхроимпульсов на вход С. Таким образом, при J=1и К=0выход триггера Qn=1, если Qn-1 = 0 или Qn-1= 1. Подобным же образом по отношению к состоянию Q = 0 действует сигнал К=1при J=0.

Если же J=K=1, то получим S1 = 1 и Rl=0 при Q = 0 или S1=0 и Rl = l при Q=l. Вследствие этого при J=K=1триггер переключится в противоположное состояние при соответствующем фронте сигнала на входе С.

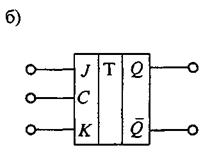

Аналогичный JK-триггер в интегральном исполнении показан на рис. 13.4 б.

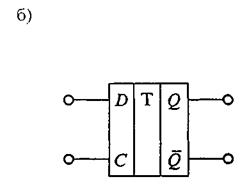

D-триггер состоит из ЯП и ЛУ на двух ячейках И-НЕ, включенных по схеме рис. 13.5 а. D-триггер, изображенный на рис. 13.5 a, устанавливается в состояние Q=D только при С=1. Аналогичный D-триггер в интегральном исполнении показан на рис. 13.5 б. D-триггер, тактируемый фронтом, построен на двух D-триггерах, тактируемых импульсом (рис. 13.6 а). На схеме рис. 13.6 а информационный вход D2 соединен с выходом Q1. Синхросигнал подается на обе ступени, но в триггере второй ступени он инвертируется. Благодаря этому при любом сигнале на входе С (С=0 или С= 1) один из двух триггеров не реагирует на сигнал, поступающий на его информационный вход. В результате как при С=0, так и при С= 1 изменение сигнала на входе D не приведет к непосредственному изменению выходного сигнала Q. И только в тот момент времени, когда потенциал С переходит из «1» в «0», возможно изменение сигнала Q. При С=1 триггер первой ступени воспринимает информацию со входа D. Когда же происходит изменение сигнала на входе С и он становится равным «0», производится прием информации триггером второй ступени с выхода триггера

|

|

Рис. 13.4. JK-триггер (а) и его условное схематическое обозначение (б)

|

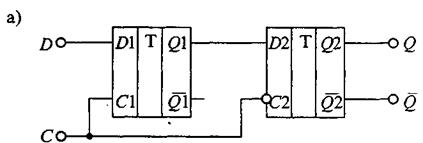

Рис. 13.5. D-триггер (а) и его условное схематическое обозначение (б)

первой ступени. Переход сигнала на входе С из «1» в «0» отражен косой чертой ( \ ) на входе С.

Счетный T-триггер можно построить на JK-триггере или на D-триггере. Для построения T-триггера на JK-триггере нужно сделать входы J=K=1(рис. 13.7 а). Тогда каждый импульс на входе С будет изменять состояние триггера на противоположное, т. е. он превратится в Т-триггер.

Для построения счетного Т-триггера на D-триггере необходимо соединить его вход D с инверсным выходом Q, т.е. сделать D=Q (рис. 13.7 б). В такой схеме каждый переход 1/0 на входе С будет приводить к переходу триггера в противоположное состояние. Например, если Qn = 1, то Qn = Dn = 0, и поэтому очередной тактовый импульс переведет триггер в новое состояние, т. е. сделает Qn+1 = Dn = 0.

Интегральные микросхемы триггеров.Промышленность выпускает большое количество интегральных микросхем триггеров, построенных на диодно-транзисторной логике (ДТЛ), транзисторно-транзисторной логике (ТТЛ), эмиттерно-связанной логике (ЭСЛ), комплементарных полевых транзисторах (КМОП). В табл. 13.1 приведены основные типы триггеров различных серий интегральных микросхем. Условное обозначение интегральных микросхем триггеров состоит из обозначения серии (трех или четырех цифр), функционального назначения (двух букв) и порядкового номера разработки (от одной до трех цифр).

|

|

Рис. 13.6. D-триггер, тактируемый фронтом (а), и его условное схематическое обозначение (б)

Рис. 13.7. Счетный T-триггер на JK-триггере (а) и на D-триггере (б)

Дата добавления: 2016-04-06; просмотров: 1903;