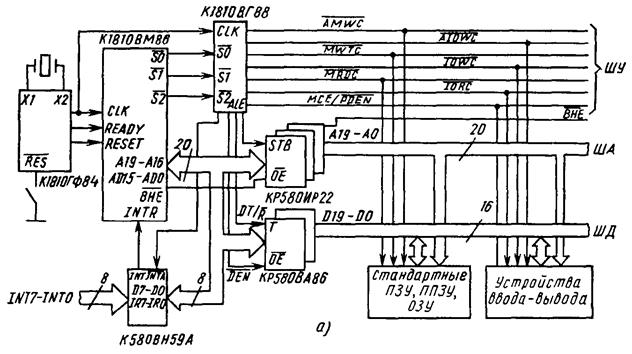

Структура системы средней сложности на базе микропроцессора К1810ВМ86

Максимальный режим отличается тем, что в нем используются дополнительные управляющие сигналы, обеспечивающие совместную работу центрального процессора с другими процессорами (сопроцессорами).

Сопроцессоры берут на себя выполнение арифметических действий (ВМ87) и реализацию обмена данными с внешними устройствами (ВМ89). Кроме того, возможно построение системы, где совместно работает несколько микропроцессоров (ВМ86).

При установке максимального режима изменяется назначение восьми выводов микропроцессора, что отражается в изменении их обозначений (таблица 5.3).

|

| Рис. 5.3 Структура системы средней сложности |

| Таблица 5.3 Назначение сигналов в минимальном и максимальном режимах | ||

| Режим | Назначение вывода в максимальном режиме | |

| Минимальный (MN/MX#=1) | Максимальный (MN/MX#=0) | |

| WR# INTA# ALE M/IO# DT/R# DEN# HOLD HLDA | LOCK# QS1 QS2 S2# S1# S0# RQ#/GT0# RQ#/GT1# | Блокировка Состояние очереди команд Состояние МП Запрос/представление |

На выводах S0#, Sl#, S2# в тактах Т1, Т2 и Т4 присутствует код состояния микропроцессора, характеризующий текущий цикл работы и определяющий способ использования шины A/D. Во время тактов ТЗ и Т4, когда шина A/D не используется, на выводах S0#, Sl#, S2# присутствует код 111. На основе этих сигналов о состоянии микропроцессора системный контроллер К1810ВГ88 формирует необходимые для управления внешними устройствами сигналы системной шины. Таким образом, в максимальном режиме микропроцессор обязательно работает совместно с контроллером системной шины.

| Таблица 5.4 Сигналы состояния микропроцессора | |||

| S2# | Sl# | S0# | Состояние МП |

| Выдача сигнала INTA# | |||

| Чтение данных из ВУ | |||

| Запись данных на В У | |||

| Останов | |||

| Выборка команды | |||

| Чтение из памяти | |||

| Запись в память | |||

| Нерабочее состояние |

Выводы RQ#/GT0# и RQ#/GT1# являются двунаправленными линиями, предназначенными для организации захвата системной шины другими устройствами. Вход запроса захвата RQ#/GT0# имеет более высокий приоритет, а в остальном эти входы функционально эквиваленты. Захват начинается с поступления на один из входов RQ#/GTi# сигнала запроса шины длительностью в один такт от внешнего устройства (если запрос приходит на оба входа, выбирается наиболее приоритетный). Во время очередного такта Т1 или Т4 на этот вывод микропроцессор подает выходной сигнал захвата, который информирует запросившее устройство о разрешении.

В следующем такте микропроцессор освобождает шину сигналом, который также подается на вывод RQ#/GTi# микропроцессора, и имеет длительность один такт. Получив этот сигнал, микропроцессор возобновляет работу. Вывод LOCK#, так же как и выводы RQ#/GTi#, служит для организации взаимодействия микропроцессора с внешними устройствами. Активный сигнал LOCK# = 0 вырабатывается с помощью специальной команды и позволяет, в случае необходимости, запретить захват шины микропроцессора внешними устройствами.

Выводы QS0, QS1 несут информацию о формировании очереди из байтов команд. Для дешифрации сигналов состояния микропроцессора (S0, SI, S2) в систему (при использовании микропроцессора в максимальном режиме) включается системный контроллер К1810ВГ88, позволяющий осуществить полную развязку управляющей, адресной и информационной шин, а также учесть различия ВУ и ЗУ при обращении к ним. Это позволяет полностью реализовать возможности адресации, предусмотренные ВМ86, т.е. возможности обращения к 1 Мбайт памяти и 64 Кбайт портов ввода-вывода.

Дата добавления: 2016-03-10; просмотров: 1377;