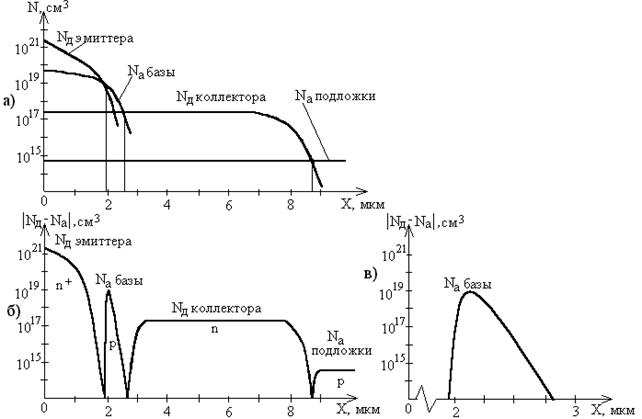

Распределение примесей.

На рисунке 4.6а показано распределение примесей в слоях, выше рассмотренного интегрального транзистора. Однако более наглядно выглядит график распределения примесей, когда по оси ординат откладывается модуль разницы между донорной и акцепторной примесями ½NД-NА½(рисунок 4.6б).

Следует обратить внимание на то, что распределение примесей в эмиттере и базе оказывается неравномерным. Представляет интерес рассмотреть распределение акцепторной примеси в базе (рисунок 4.6в). Справа от точки максимума градиент концентрации дырок отрицательный и внутреннее поле (по отношению к инжектированным электронам) является ускоряющим. Это характерно для дрейфовых транзисторов. Однако слева от точки максимума на небольшом участке градиент положительный, а, значит, электрическое поле является тормозящим. Наличие участка с тормозящим полем приводит к некоторому увеличению результирующего времени пролета носителей через базу. Однако расчеты показывают, что это увеличение составляет примерно 20% и для приближенных оценок может не учитываться.

Рисунок 4.6

Эквивалентная схема.

На рисунке 4.7а представлена четырехслойная структура биполярного транзистора совместно с подложкой. Эту структуру можно рассматривать как две трехслойных структуры (рисунок 4.7б) представляющие собой два транзистора: основной n-p-n и паразитный p-n-p (рисунок 4.7в).

| а) | б) | в) |

Рисунок 4.7

Паразитный транзистор находится в режиме отсечки, когда основной работает в режимах отсечки или активном. Но когда основной транзистор работает в режиме насыщения, т.е. его коллекторный переход включен в прямом направлении, то паразитный транзистор находится в активном режиме, так как его эмиттерный переход – это коллекторный переход основного транзистора. В этом случае, через паразитный транзистор осуществляется связь между основными транзисторами, находящимися в режиме насыщения.

Резистор rК (рисунок 4.7в) учитывает распределенное сопротивление коллектора, так как коллекторный слой имеет наименьшую концентрацию примеси. Его величина составляет примерно 100 Ом. Этот резистор совместно с ёмкостями СКП и СКБ образуют RC цепочку, которая ухудшает быстродействие транзистора и ограничивает его предельную частоту. Кроме того, в ЦИМС это приводит к тому, что возрастает уровень логического нуля U0. Для исключения выше отмеченных явлений между коллектором и подложкой формируют скрытый слой n+. Такие транзисторы будут рассмотрены ниже.

В случае диэлектрической изоляции паразитный p-n-p транзистор отсутствует, но ёмкость СКП сохраняется. Она, как уже отмечалось, меньше, чем при изоляции p-n переходом примерно в три раза.

Планарно-эпитаксиальный биполярный транзистор

Со скрытым слоем

Первыми операциями при изготовлении таких микросхем являются термическое окисление, фотолитография и диффузия донорной примесью, чтобы создать n+ - слой на месте, где будут формироваться транзисторы (рисунок 4.8а). Толщина этого слоя составляет примерно 2 мкм. Затем слой SiO2 стравливается. В последующем проводится эпитаксия и последовательно все операции, которые использовались при изготовлении планарно–эпитаксиального транзистора. Структура готового транзистора приведена на рисунке 4.8б.

| а) | б) |

Рисунок 4.8

Распределение примесей приведено на рисунке 4.9. Поскольку в коллекторе основного транзистора (этот же слой является базой паразитного транзистора) распределение примеси неравномерное, то в нем создается тормозящее электрическое поле для дырок, которые движутся из эмиттера в коллектор паразитного транзистора. Кроме того, высокая концентрация примеси в коллекторе на порядок снижает распределенное сопротивление rК основного транзистора. Это исключает недостатки планарно-эпитаксиального транзистора.

Рисунок 4.9

Дата добавления: 2015-12-16; просмотров: 2444;