Запоминающие устройства характеризуются рядом качественных показателей.

1. Емкость ЗУ определяется максимально возможным количеством битов хранимой информации.

2. Ширина выборки определяется количеством информации, записываемой в ЗУ или извлекаемой из него за одно обращение. Эта характеристика достаточно важная, так как при одинаковом времени обращения ЗУ с большей шириной выборки обладает большей информационной эффективностью.

3. Время обращения определяется с момента подачи в устройство сигнала записи или чтения до того момента, когда закончатся все действия, связанные с выполняемой операцией, и устройство будет готово принять и реализовать следующую операцию обращения к накопителю информации. Это время называется также длительностью цикла обращения к ЗУЦ в течение которого можно выбрать информацию (чтение), ввести информацию (запись), обновить или модифицировать состояние некоторого элемента ЗУ.

4. Скорость обмена информацией между ЗУ и другими устройствами является важным параметром запоминающих устройств. Она определяется числом бит (байт), передаваемых в единицу времени.

5. Показатель удельной стоимости применяется для оценки экономических характеристик ЗУ. Он определяется отношением его стоимости к информационной емкости, т. е. стоимости бита хранимой информации.

6. Надежность, а для систем специального назначения – массогабаритные показатели и потребляемая мощность являются для ЗУ существенными характеристиками.

7. Одна из характеристик ЗУ – способность сохранять информацию при отключении источников питания. В этом случае различают энергозависимую или энергонезависимую память. В энергонезависимой памяти при нарушениях в работе системы питания данные не разрушаются, а в энергозависимой — разрушаются.

ВТОРОЙ ВОПРОС

По принципу хранения информации полупроводниковые оперативные ЗУ делятся на динамические и статические.

Динамические запоминающие устройства строятся на основе запоминающего элемента, сохраняющего свое состояние только определенный промежуток времени и поэтому требующего периодического восстановления. Запоминающим элементом динамических полупроводниковых ЗУ служит конденсатор, в котором информация хранится в форме наличия или отсутствия заряда. Из-за утечек постепенно уменьшается заряд на запоминающем конденсаторе; для восстановления заряда запоминающий конденсатор периодически подключают к источнику питания.

Регенерация (восстановление данных) ячейки динамической памяти производится при каждом обращении к ней. Однако при обычной интенсивности работы памяти микропроцессорной системы такая регенерация не гарантирует сохранности всех хранившихся в ней битов информации. Микропроцессор может, например, затратить время, превышающее несколько миллисекунд, на выполнение простого цикла, предназначенного для выработки временной задержки, и использовать при этом лишь несколько ячеек памяти.

В течение всего этого временного промежутка все другие слова памяти не будут подвергаться регенерации. Поэтому устройства памяти, выполненные на динамических ЗУ, нуждаются в логической схеме регенерации, которая автоматически обращается к каждому столбцу памяти с интервалами в несколько десятых долей миллисекунды.

Динамическое запоминающее устройство построено так, что само обращение к столбцу обеспечивает регенерацию информации во всех его ячейках. Работа логической схемы регенерации должна координироваться с другими действиями микропроцессора. Если, например микропроцессор пытается обратиться к памяти в момент, когда в ней осуществляется регенерация, схема регенерации должна отдать приоритет именно микропроцессору.

Динамический принцип хранения информации обеспечивает ряд преимуществ динамических ЗУ. Динамические полупроводниковые ЗУ с произвольной выборкой имеют высокий уровень интеграции и быстродействия, низкую стоимость и поэтому находят широкое применение в микропроцессорных вычислительных системах. На динамических БИС ЗУ, являющихся функционально законченными устройствами, можно сравнительно просто строить ОЗУ различной информационной емкости.

Схемы управления ЗУ (мультиплексор, управление регенерацией) могут быть выполнены на стандартных или специализированных ИС.

Недостаток динамических ЗУ – необходимость регенерации компенсируется большей, чем в статических ЗУ, информационной емкостью.

Статические запоминающие устройства являются наиболее распространенным видом памяти микропроцессорных систем. Большинство статических запоминающих устройств реализуется на основе МОП-технологии, но существуют и статические ЗУ на биполярных схемах.

Ячейка памяти статического ЗУ представляет собой обычный триггер. Он может быть установлен либо в состояние «1», либо в состояние «0» Если триггер установлен в «1», то это состояние сохраняется до тех пор, пока не будет произведен сброс триггера или не будет выключено питание.

Подобные ячейки памяти объединяются в матричную структуру, т. е. размещаются по строкам и столбцам. При построении статических ЗУ наибольшее распространение получили БИС ЗУ с конфигурацией (n×l) бит, где п – количество ячеек, n = 256, 512, 1024, 2048, ..., 2к. Выпускаются БИС ЗУ и с другой конфигурацией. Память микроЭВМ обычно имеет разрядность, равную или кратную разрядности микропроцессора.

Необходимая длина слова памяти достигается параллельным включением т БИС памяти, где т — длина слова в битах. В 8-разрядном микропроцессоре для построения памяти с организацией n×8необходимо включить параллельно восемь БИС ОЗУ с организацией n×1. Совокупность восьми одноразрядных линий данных всех восьми БИС образует 8-разрядную шину данных запоминающего устройства. Линии адреса и чтения/записи всех БИС включаются параллельно для одновременного обращения ко всем БИС ЗУ.

Часто разрядность шины адреса микроЭВМ больше разрядности ее шины данных. Так, в 8-разрядной микроЭВМ применение 16-разрядного адреса обеспечивает адресацию 65 536 байт памяти.

Два байта называют младшим и старшим байтами адреса. Младшие разряды адреса A0...A7 называют адресом слова (байта), а старшие разряды А8... А15 называют адресом страницы.

Таким образом, можно адресовать 256 страниц по 256 слов (байт) в каждой.

Типичные БИС динамического ОЗУ: КР565РУ6 – емкость 16384×1 бит; К565РУ5 – емкость 65536×1 бит.

Типичные БИС статического ОЗУ: КР537РУ14 – емкость 4096×1 бит; КР132РУ6А – емкость 16384×1 бит; К537РУ9 – емкость 2048×8 бит;

ТРЕТИЙ ВОПРОС

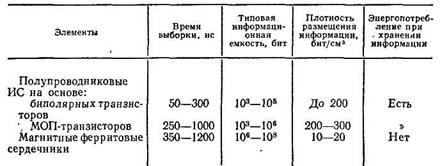

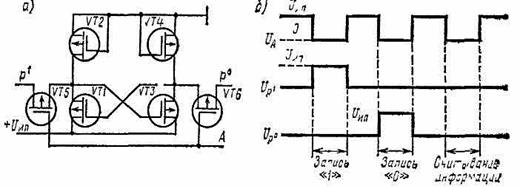

С развитием микроэлектроники появилась возможность применять в ЗУ полупроводниковые элементы. Из таблицы 3, в которой сравниваются параметры и свойства ОЗУ, выполненных на различной элементно-технологической основе, видно, что на биполярных транзисторах целесообразно конструировать скоростные ЗУ с информационной емкостью до 105 бит. Запоминающие устройства на МОП-транзисторах обладают емкостью 106 бит при умеренном быстродействии. На ферритовых сердечниках можно получать ЗУ с объемом памяти более 106 бит, обладающих невысоким быстродействием. Однако особое достоинство магнитных ЗУ – это возможность хранения информации без энергопотребления.

Таблица 3.

Применение полупроводниковых структур позволяет существенно увеличить быстродействие, уменьшить массу, габаритные размеры и увеличить надежность работы ЗУ.

В последние годы благодаря совершенствованию биполярных ИС, а также расширению серий ИС на МОП-транзисторах были созданы элементы статических ЗУ (на биполярных, а также на р-канальных и n-канальных МОП-транзисторах).

Статические ЗУ на биполярных транзисторах.Они представляют собой матрицу запоминающих элементов, каждый из которых может быть установлен в одно из двух устойчивых состояний. Таким элементом обычно является триггер. Из ЗЭ строится накопительная матрица памяти – основа ОЗУ. На одном кристалле биполярной ИС можно расположить, например, ОЗУ на 4096 бит с временем выборки менее 60 нс. Построение (организация) матрицы определяется способом выборки (опроса) ЗЭ при записи или считывании.

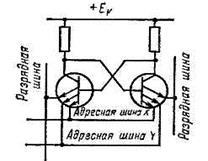

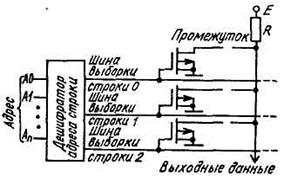

В структурной схеме матрицы с пословной выборкой и одной ступенью дешифрации (рис. 2, а) одна строка образует слово из т разрядов. На схеме символами А1, А2, ..., Аn обозначены адресные, а Р1, Р2, ..., Рт – разрядные шины.

Как видно из схемы, адресные шины связаны с каждым ЗЭ одного слова, в то время как разрядные шины имеют связь с ЗЭ одноименного разряда всех слов. При наличии в адресной шине Аi сигнала выбора i-го слова,

соответствующего высокому уровню, состояние каждого из ЗЭ в этом слове может быть считано по разрядным шинам Р1—Рт. Если необходимо записать информацию по выбранному адресу Аi на разрядные шины P1, Р2,…, Рт подаются электрические сигналы «1» или «0», которые попадут на каждый из запоминающих элементов i-й строки: ЗЭi1, ЗЭi2, ЗЭi3, .. . 3Эim.

На рис. 2, а не показаны устройства управления матрицей (дешифратор с адресными формирователями, усилители считывания и записи), которые для повышения надежности работы ОЗУ изготовляются на одном кристалле с матрицей.

Рис. 2 Структурные схемы матриц (накопителей информации):

а – с пословной выборкой и одной ступенью дешифрации;

б - двухкоординатной с двумя ступенями дешифрации.

В структурной схеме двухкоординатной матрицы информации с двумя ступенями дешифрации (рис. 2, б) ЗЭ выбирается с помощью двух адресных шин. Например, при наличии сигнала, соответствующего высокому уровню, на адресных шинах XI, Y1 будет выбран только 3Э1. Его состояние можно считывать по общей для всех элементов разрядной шине Р. Чтобы записать «1» в выбранный ЗЭ, по разрядной шине необходимо подать сигнал, соответствующий высокому уровню. Эта организация матрицы позволяет оперировать тп одноразрядными словами.

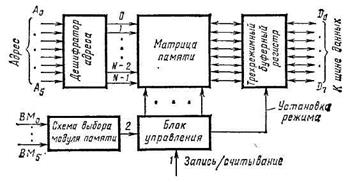

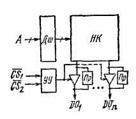

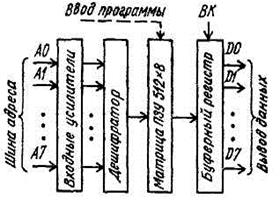

Структура и принцип построения БИС ОЗУ.Принцип построения БИС ОЗУ показан на рис. 3. Основным компонентом этой БИС служит матрица памяти – накопитель. Матрица содержит N ячеек, памяти. В каждой из них помещается одно слово длиной М бит, где М — количество разрядов ячейки. Для рассматриваемого примера матрицы памяти (128×8) соответственно N=128 и М=8; следовательно, ОЗУ может хранить 128 байт.

Порядковый номер (от 0 до N—1) ячейки памяти, содержащей один байт, определяет ее адрес. В данном примере матрицы памяти адреса ячеек представляют числа от 0 до 12710. Им соответствуют числа от 0000000 до 11111112. Подчеркнем, что адрес определяет местоположение слова (байта), а не бита.

Для обращения к конкретной ячейке памяти с целью записи или считывания слова с адресной шины на входы Ао—A6 дешифратора адреса подается адрес ячейки в форме 7-разрядного двоичного кода (предположим, 0001011). При этом на выходе дешифратора (в данном случае — одиннадцатом) появится сигнал, открывающий доступ к соответствующей ячейке (одиннадцатой).

Возможность считывания байта из ячейки и передачи его в шину данных через выводы микросхемы Do—D7 или приема байта, поступающего с шины данных на те же выводы микросхемы, и записи его в память зависят от режима работы, состояния трехрежимного буферного регистра.

Рис. 3 Принцип построения БИС ОЗУ.

В первом режиме ВЫВОД производится считывание, во втором режиме ВВОД — запись, а в третьем режиме ВЫСОКИЙ ИМПЕДАНС, НЕЙТРАЛЬНОЕ СОСТОЯНИЕ линии шины данных отключены от матрицы — разрывается цепь передачи сигналов.

Операция считывания заключается в выборке байта, хранимого в ячейке указанного адреса (содержимое ячейки при этом остается неизменным). Для выполнения операции необходимо, чтобы в трехрежимный буферный регистр поступил с выхода блока управления ОЗУ сигнал, устанавливающий режим ВЫВОД. Такой сигнал появляется тогда, когда на входы 1 и 2 блока управления поданы логические единицы. При этом буферный регистр пропускает байт из определенной адресом ячейки памяти через выходы D0—D7 в шину данных. Наличие логической единицы на входе запись — считывание блока управления обусловливает такую блокировку входов буферного регистра, что поступление числа с шин данных в память невозможно.

Операция записи предполагает введение нового байта в ячейку, определяемую адресом. Если ранее в этой ячейке был записан байт, то он стирается и его место занимает новый байт. Чтобы пропустить через трехрежимный буферный регистр байт, поступающий с шины данных на входы D0—D7, необходимо установить в регистре режим ВВОД. Для этого требуется одновременное наличие логического нуля на входе блока управления и логической единицы на его входе . 2. При такой комбинации становится возможным прием байта с шины данных в ячейку памяти по указанному адресу. Наличие логического нуля на, входе запись — считывание приводит к блокировке буферного регистра, исключающей выдачу байтов в шину данных.

Если на входе 2 блока управления — логический нуль, то при любом состоянии входа этого блока трехрежимный буферный регистр находится в третьем режиме, при котором шина данных отключена от ОЗУ, т. е. ни считывание, ни запись не могут иметь места. Наличие логического нуля или логической единицы на выходе схемы выбора модуля памяти, или, что то же самое, на входе 2 блока управления, зависит от кода (сочетания сигналов) на входах ВМ0—ВМ5 схемы выбора модуля. Эти входы используются тогда, когда оперативное запоминающее устройство составляют из нескольких БИС ОЗУ.

При наличии в составе основной памяти двух (или более) модулей ОЗУ часть кода адреса используется для указания конкретного модуля, в котором хранится требуемый байт. Она подается на входы схем выбора модуля памяти.

Рис. 4 Запоминающий элемент—триггер

на биполярных транзисторах.

Когда работает определенная БИС комплекта ОЗУ (из нее считывается или в нее записывается число), то на выходе схемы выбора модуля, входящей в состав данной БИС ОЗУ, имеется «лог. 1», а на выходах таких же схем у остальных БИС — «лог. 0»

Рассмотрим принцип построения полупроводниковых ЗЭ, на которых строятся матрицы ОЗУ.

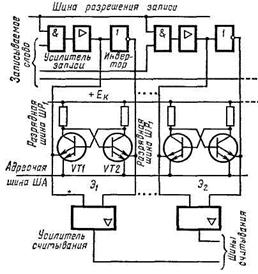

Запоминающий элемент — триггер на биполярных транзисторах с непосредственными связями представлен на рис. 4. Будем считать, что в ЗЭ записан 0, если транзистор VT1 открыт, а транзистор VT2 закрыт. От +Ек к -Ек (к «земле») через открытый транзистор триггера ток может проходить через цепи эмиттеров.

Верхние по схеме эмиттеры подключены к разрядным шинам, нижние соединены и выведены на адресную шину. При выборе ячейки, в которую входят рассматриваемые ЗЭ, данная адресная шина возбуждается — ее потенциал возрастает, и цепь тока через нижние эмиттеры обрывается.

В режиме хранения ЗЭ не выбраны — адресная шина имеет низкий потенциал, а разрядные — наиболее высокий. Поэтому ток открытого транзистора протекает через нижний эмиттер на адресную шину и по ней на «землю».

В режиме записи происходит выборка ЗЭ ячейки —данная адресная шина приобретает высокий потенциал, и ток отпертого транзистора ЗЭ может протекать только на разрядную шину. При появлении на входе двоичной переменной, записываемой в данный ЗЭ, и сигнала разрешения записи одна разрядная шина (например, ШР1 получает высокий потенциал, а другая (шина ШР1) — благодаря инвертору — низкий. Если перед этим триггер находился в состоянии 0 (VT1 отперт), то он переключается в состояние 1 (отперт VT2).

В режиме считывания вновь происходит выборка ЗЭ ячейки — адресная шина получает высокий потенциал, и ток открытого транзистора протекает по разрядной шине на один из входов усилителя считывания. На его выходе появляется «лог. 1», если отперт VT2, и «лог. О», если отперт VT1.

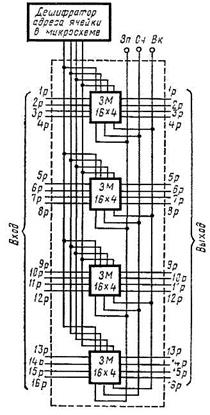

В случае необходимости микросхемы ЗУ можно объединить, увеличивая тем самым емкость памяти. Для этого они имеют специальный вывод — «Выбор корпуса» (ВК).

Рис. 5 Объединение микросхем для хранения 16-разрядных слов

Рис. 6 Запоминающий элемент для ЗУ с двухкоординатной выборкой

На рис. 5 показано объединение микросхем для хранения 16-разрядных слов (емкость накопителя — 256 бит). Здесь объединены адресные шины всех микросхем, а также шины выбора корпуса. На шинах записи кода первой микросхемы устанавливаются первые четыре разряда записываемого числа, на аналогичных шинах второй микросхемы — следующие четыре разряда и т. д. При работе ЗУ подается сигнал разрешения на объединенные шины ВК всех микросхем.

Микросхемы ЗУ объединены для получения и других вариантов распределения суммарной емкости.

Запоминающий элемент для ЗУ с двухкоординатной выборкой (рис. 6) представляет собой триггер на трехэммитерных транзисторах. Третьи эммитеры каждого транзистора соединены и выведены на вторую адресную шину.

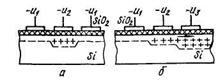

Запоминающие элементы на МОП-транзисторах.Взависимости от типа ЗЭ на основе МОП-транзисторов можно построить ЗУ статические или динамические. В первом случае в качестве ЗЭ служит статический триггер, во втором случае информация запоминается на емкости затвора МОП-транзистора. Запоминающее устройство на МОП-транзисторах, так же как и на биполярных транзисторах, может быть с пословной и двухкоординатной произвольной выборкой.

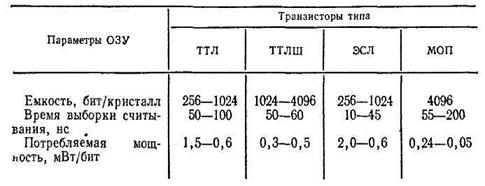

Рис. 7. Запоминающий элемент — триггер на основе МОП структуры:

а – схема; б – временная диаграмма работы.

Пример простейшей схемы ЗЭ-триггера на МОП-транзисторах для ЗУ с пословной выборкой приведен на рис. 7, а. Триггер образован транзисторами VT1—VT4. Управление триггером для записи и считывания осуществляется переключением транзисторов VT5 и VT6. Временные диаграммы работы такого ЗЭ представлены на рис. 7, б. В исходном состоянии напряжение на обеих разрядных шинах Р1 и Р° равно нулю, а на шине слова А потенциал равен напряжению питания схемы. При этом транзисторы VT5 и VT6 закрыты, так как разность потенциалов между затворами и истоками по абсолютной величине меньше порогового напряжения. Триггер находится в одном из устойчивых состояний.

Пусть, например, транзистор VT3 открыт, а транзистор VT1 закрыт. При записи «1» в шину слова подается отрицательный сигнал, изменяющий напряжение в ней до нуля, одновременно в разрядную шину Р1 подается положительный сигнал, изменяющий напряжение в ней до напряжения питания Uип. При этом транзистор VT5 открывается, так как разность потенциалов между затвором и истоком становится отрицательной. Положительный сигнал поступает на сток транзистора VT1 и на затвор транзистора VT3. Разность потенциалов между затвором и истоком транзистора VT3 становится меньше порогового напряжения, и этот транзистор закрывается. После запирания транзистора VT.3 открывается транзистор VT1 и на его стоке устанавливается положительное напряжение, что соответствует состоянию «1». Напряжение на стоке транзистора VT3 становится равным нулю.

При записи «0» в ЗЭ необходимо при нулевом напряжении на шине слова подать напряжение Uип в разрядную шину Р0. При этом через открытый транзистор VT6 положительное напряжение, попадая на затвор транзистора VT1, запирает его, что приводит к открыванию транзистора VT3. Для считывания информации, предварительно записанной в ЗЭ, необходимо подать отрицательный сигнал только на шину слова, изменяя в ней напряжение до нуля. При этом транзисторы VT5 и VT6 оказываются открытыми и через транзистор, присоединенный к точке триггера с положительным потенциалом, протекает ток, поступающий в соответствующую разрядную шину и далее на усилитель считывания.

Биполярные ЗУ наиболее эффективны, как высокоскоростные буферные ЗУ. Наиболее широко применяются биполярные ЗУ на ТТЛ- и ЭСЛ-транзисторах. Основное внимание при создании биполярных ЗУ уделяется увеличению плотности упаковки.

ЗУ на р-канальных МОП-транзисторах имеют минимальную себестоимость, но обладают более низким быстродействием; ЗУ на n-канальных МОП-транзисторах по быстродействию в ряде случаев приближаются к биполярным; ЗУ на КМОП-транзисторах имеют низкую статическую потребляемую мощность и среднее быстродействие. Технология производства КМОП ЗУ достаточно сложна, и поэтому их себестоимость выше, чем у р- и n-канальных МОП-транзисторов.

В микропроцессорных и вычислительных устройствах широко применяют следующие основные типы ЗУ: регистровую память, встраиваемую в центральный процессорный элемент (общее число регистров обычно 8—16); сверхоперативную память емкостью примерно 64 слова и временем выборки несколько десятков наносекунд; оперативную память емкостью 4—64 тыс. слов с возможностью наращивания до 128 тыс. слов.

Интегральные схемы ОЗУ.Они содержат на одном кристалле матрицу ЗЭ, дешифраторы адреса, формирователи, усилители считывания и другие схемы управления, необходимые для функционирования ОЗУ.

Оперативные запоминающие устройства можно разделить на две группы: статические и динамические. В динамических ОЗУ запоминающим элементом служит конденсатор, в котором информация хранится в форме наличия или отсутствия заряда. Преимуществом статических ОЗУ перед динамическими является отсутствие схемы регенерации информации, что значительно упрощает управление ОЗУ. Кроме того, схема статических ОЗУ имеет, как правило, одно питающее напряжение. Типовые характеристики статических ОЗУ приведены в табл. 3.

Таблица 3.

Статические ОЗУ на МОП-транзисторах, несмотря на среднее быстродействие, получили широкое распространение, что объясняется большей плотностью размещения ячеек на кристалле, чем у биполярных ОЗУ.

Основными характеристиками ИС ОЗУ являются: емкость, измеряемая числом двоичных единиц информации (бит), хранящейся в ЗУ; быстродействие, определяемое временем обращения к ЗУ (дополнительно быстродействие может быть охарактеризовано также временем записи и временем считывания); мощность, потребляемая одним ЗЭ (мВт/бит), или мощность потребления всей ИС ЗУ в целом. Важной характеристикой является степень интеграции, выраженная в числе элементов или эквивалентных вентилей на корпус.

За последние годы были расширены серии ИС ТТЛ и ЭСЛ, в состав которых введены ОЗУ на 256 бит с произвольной выборкой и схемами управления (К155РУ5), ОЗУ на 4096 бит (К500РУ410). В состав серий ИС на КМОП-транзисторах включены ОЗУ на 256 бит (564РУ2А, К176РУ2).

ЧЕТВЕРТЫЙ ВОПРОС

На современном этапе развития цифровой техники удельный вес ЗУ в составе аппаратуры непрерывно возрастает. К тому же ЗУ сами по себе относятся к числу наиболее сложных устройств цифровой техники. Тенденция постоянного увеличения уровня интеграции микросхем ЗУ приводит к соответствующему уменьшению геометрических размеров компонентов, увеличению паразитных связей между ними и, как следствие этого, к возрастанию чувствительности к различным помехам. Отметим, что даже кратковременное нарушение нормального функционирования ЗУ может привести к серьезным последствиям в работе цифровой системы. Поэтому принимается комплекс мер по обеспечению исправного функционирования ЗУ.

Он предусматривает контроль функционирования ЗУ с целью выявления фактов постоянного и кратковременного нарушения работоспособности, диагностирование с целью локализации мест нарушения и управление процессом восстановления работоспособного состояния.

Коротко рассмотрим основные причины нарушения работоспособности ЗУ. Устойчивые нарушения (отказы) вызываются дефектами в полупроводниковых кристаллах, например, из-за локального внедрения посторонних примесей, пробоя окисла статическим электричеством, а также обрывами и короткими замыканиями проводников кристаллов, корпусов микросхем и печатных плат из-за деформации, различных загрязнений и допущенных на этапе изготовления нарушений технологических режимов. Они могут проявляться, например, в неверном считывании информации из каких-либо ячеек памяти, постоянном пребывании некоторых информационных выходов в состоянии «Отключено», даже когда происходит обращение к микросхеме, и т. д.

Кратковременные нарушения (сбои) могут быть результатом действия помех по питанию, например, из-за неправильной прокладки шин «земля» и напряжения, внешних электромагнитных помех, излучения α-частиц из материала корпусов микросхем, случайного сочетания в определенные моменты значений сигналов, приводящего к неправильным действиям, и т. д. Обычно они проявляются в неверном считывании или записи информации в случайные моменты времени. Устойчивость функционирования ЗУ повышается при использовании соответствующих средств контроля, диагностирования и управления процессом восстановления работоспособного состояния. Одна часть из этих средств может быть внешней по отношению к ЗУ, другая — может входить в их состав.

Имеются довольно значительные отличия в организации работы при выявлении и устранении отказов и сбоев, поэтому будем их рассматривать отдельно друг от друга. Выявление отказов и локализация мест, в которых они возникают, выполняется путем организации тестового контроля и диагностирования. С этой целью от генератора тестов на испытуемое ЗУ подается последовательность проверочных сигналов. Выходные сигналы ЗУ, являющиеся реакцией на эти тесты, сравниваются с эталонными сигналами, которые соответствуют нормально функционирующему ЗУ (рис. 8).

Результаты сравнения затем используются для принятия решения о работоспособности всего ЗУ и его отдельных составляющих частей. Функции генератора эталонных сигналов может выполнять однотипное с испытуемым исправное ЗУ.

Рис. 8. Схема организации тестового контроля и диагностирования.

Для организации тестового контроля и диагностирования широко применяются микроЭВМ, в которых необходимые тесты, эталонные сигналы и последующие сравнения с принятием необходимых решений могут реализоваться программным путем.

Существует большое число алгоритмических тестов, начиная с простейших, предусматривающих последовательную запись информации в ячейки памяти с последующим ее считыванием, и кончая достаточно сложными вариантами комбинированных действий, по передаче информации с проверкой соответствия временных соотношений паспортным данным микросхем ЗУ.

Постоянно возрастающие возможности интеграции микросхем ставят на повестку дня разработку ремонтопригодных микросхем памяти. В этом случае на полупроводниковом кристалле формируются резервные ЗЭ и схемы обрамления, которые подключаются к определенным выводам с помощью плавких перемычек. В таких микросхемах появляется возможность после проведения соответствующего диагностирования управлять процессом восстановления работоспособности ЗУ: разрушая некоторые плавкие перемычки, заменять неисправные элементы исправными (резервными).

Для борьбы со сбоями организуется функциональный контроль, предусматривающий выявление сбоев и их устранение в процессе выполнения ЗУ своих рабочих функций. Учитывая, что сбои возникают главным образом в соединительных цепях и проявляются в форме ошибочного изменения информационного значения на противоположное в одном или нескольких разрядах слов, для обнаружения и устранения сбоев широко применяется помехоустойчивое кодирование: в каждое информационное слово включаются специальные проверочные двоичные разряды. В ЗУ вводятся элементы, выполняющие указанные операции при каждой записи информации. В процессе считывания производится контроль каждого информационного слова с выявлением и фиксацией на основе анализа проверочных разрядов возникших сбоев. В некоторых случаях может быть предусмотрено и восстановление правильных информационных значений.

Література:

1. М.В. Напрасник «Микропроцессоры и микроЭВМ», стр: 56-62.

2. Б.Я. Лихтциндер «Микропроцессоры и вычислительные устройства в радиотехнике», стр: 86-91.

3. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования», стр: 141-145, 149-156.

4. Э.В. Евреинов «Цифровая и вычислительная техника», стр: 203-213.

5. В.Н. Сысоев «Основы радиотехники», стр: 244-247.

ЗАНЯТИЕ 1.3.3 Назначение, классификация, характеристики ПЗУ. Постоянные

ЗУ на больших интегральных схемах.

ВОПРОСЫ ЗАНЯТИЯ:

1. Особенности построения и основные параметры ПЗУ.

2. Полупроводниковые постоянные запоминающие устройства.

3. Функциональные схемы ПЗУ. Организация многокристальной памяти. Программирование ПЗУ.

ПЕРВЫЙ ВОПРОС

Постоянные запоминающие устройства (ПЗУ) в микропроцессорных вычислительных системах служат для хранения программ и другой неизменяемой информации. Важное преимущество ПЗУ по сравнению с ОЗУ — сохранение информации при выключении питания. Стоимость бита хранимой в ПЗУ. информации может быть почти на порядок ниже, чем в ОЗУ. Постоянные ЗУ могут быть реализованы на основе различных физических принципов и элементов и отличаются способом занесения информации, кратностью занесения, способом стирания.

В настоящее время применяются следующие виды ПЗУ: программируемые на заводе-изготовителе или масочные ПЗУ (МПЗУ); программируемые пользователем; перепрограммируемые ПЗУ.

Первые два вида ПЗУ допускают только однократное программирование, третий вид ПЗУ позволяет изменять хранимую в нем информацию многократно.

В крупносерийном производстве изделий ВТ находят применение ПЗУ (в типах микросхем обозначаются буквами РЕ), программирование которых выполняется в процессе их изготовления. Обычно на кристалле полупроводника вначале создаются все ЗЭ, а затем на заключительных технологических операциях с помощью индивидуальных для конкретных заказчиков фотошаблонов (масок) формируется требуемая сеть соединений, определяющая записываемую информацию. При достаточно большой серийности такие ПЗУ оказываются более дешевыми по сравнению с другими разновидностями постоянных ЗУ. Их достоинством является также более простая структура и, как следствие этого, более высокая надежность. В ПЗУ достигнут наиболее высокий уровень интеграции (128 Кбит в одной микросхеме).

На этапах изготовления образцов изделий, а также в условиях мелкосерийного производства изделий ВТ широко применяются ППЗУ (в типах микросхем обозначаются буквами РТ), программирование которых осуществляется пользователем. По сравнению с ПЗУ они имеют более сложную структуру, во-первых, в связи с необходимостью введения плавких перемычек в каждый ЗЭ, во-вторых, из-за дополнительных элементов, через которые выполняется программирование. Дополнительные затраты связаны и с самим процессом программирования, который осуществляется в определенных режимах с помощью специальных программаторов. Отметим также необходимость выполнения специальных циклов термотренировки для устранения возможности восстановления некоторых перемычек после программирования, а также наличие определенной части микросхем, которую не удается запрограммировать вообще.

Рис. 1. Упрощенная схема включения элемента программирования.

С целью сокращения необходимого числа выводов корпусов для программирования используются те же выходы, по которым считывается информация из ППЗУ. К этим выводам внутри микросхемы подключаются элементы программирования, через которые обеспечивается доступ к нужным плавким перемычкам. На рис. 1 показана упрощенная структура одного из вариантов включения элементов программирования (Пр) в составе ППЗУ.

Внешний программатор подключается к выводам D0 микросхемы ППЗУ и обеспечивает подачу импульсов заданной длительности с амплитудой, существенно превышающей уровни в режиме считывания. В результате обеспечиваются отпирание элементов программирования и разрушение соответствующих плавких перемычек. Адресная шина А используется при программировании для выбора заданных ЗЭ. В приведенной структуре показаны два управляющих сигнала CS. Выбор микросхемы задается одновременной подачей разрешающих значений обоих из них. Использование нескольких таких сигналов упрощает объединение микросхем при построении памяти заданной емкости и разрядности в связи с тем, что в ППЗУ в отличие от ОЗУ отсутствуют информационные входы, менее остро стоит проблема выводов микросхем. Поэтому чаще всего в ППЗУ организуется хранение многоразрядных чисел.

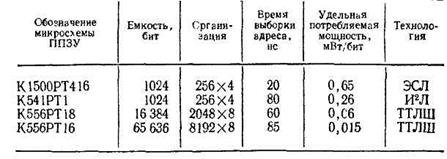

В табл. 1 приведены основные параметры некоторых широко применяемых микросхем ППЗУ. Основным временным параметром для них является время выборки адреса, определяемое с момента подачи очередного адреса на шину А до считывания числа из адресованных ячеек по выходам DO2.

Таблица 1.

Для многих применений как в условиях массового производства, так и мелкосерийного очень удобными являются репрограммируемоые постоянные ЗУ, допускающие выполнение многих циклов перепрограммирования с предшествующим стиранием ненужной информации (число циклов репрограммирования у различных типов РПЗУ колеблется от десятков до десятков тысяч). В ЗЭ таких устройств чаще всего используются МОП-транзисторы с двухслойной структурой диэлектрика или с дополнительными плавающими затворами, позволяющие за счет введения избыточного заряда при программировании изменять пороговое напряжение, при котором отпираются транзисторы. Благодаря исключительно низкой проводимости используемых диэлектриков избыточные заряды могут существовать без значительного уменьшения своей величины очень длительное время (в некоторых типах РПЗУ до десятка лет). В последнее время ведутся интенсивные разработки РПЗУ на основе аморфных полупроводников, приборов с зарядовой связью, сегнетоэлектрических МОП-структур. Сложная структура ЗЭ, необходимость введения элементов перепрограммирования, значительно повышают стоимость РПЗУ по сравнению с другими разновидностями ПЗУ. Поэтому они применяются в первую очередь там, где свойство перепрограммируемости является определяющим. Во всех РПЗУ занесение информации выполняется пользователем подачей импульсов с амплитудой порядка 20—30 В и длительностью от единиц до десятков миллисекунд. В одной из разновидностей РПЗУ (в типе микросхемы для них применяют обозначение РР) стирание информации также производится электрическим путем. Эта разновидность часто допускает возможность не только общего стирания, разрушающего информацию во всей микросхеме, но и избирательное (байтовое) стирание с последующим выполнением байтовой записи. В другой разновидности (обозначаемой в типе микросхемы буквами РФ) стирание информации производится ультрафиолетовым облучением микросхемы в течение нескольких десятков минут. В этом случае информация разрушается полностью во всей микросхеме. В большинстве типов микросхем репрограммируемых постоянных ЗУ организуется хранение многоразрядных чисел.

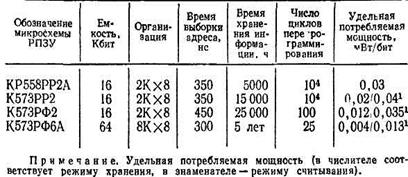

В табл. 2 приведены основные параметры некоторых широко применяемых микросхем РПЗУ.

Таблица 2.

Постоянные ЗУ можно рассматривать как универсальные элементы, позволяющие хранить произвольные записанные в них коды. Поэтому в настоящее время имеется целое направление проектирования узлов цифровой техники на базе таких ЗУ.

ВТОРОЙ ВОПРОС

Постоянное запоминающее устройство — это устройство, в котором хранится программа (и при необходимости совокупность констант). Содержимое ПЗУ используют как память программы, составленной заранее изготовителем в соответствии с требованиями пользователей. В таких случаях говорят, что программа жестко «зашита» в ЗУ. Чтобы выполнить иную программу, необходимо применить другое ПЗУ или его часть. Из ПЗУ можно только выбирать хранимые там слова, но нельзя вносить новые, стирать и заменять записанные слова другими.

Программируемые постоянные запоминающие устройства (ППЗУ) отличаются от ПЗУ тем, что пользователь может самостоятельно запрограммировать ПЗУ (ввести в него программу) с помощью специального устройства — программатора, но только один

раз (после введения программы содержимое памяти изменить нельзя).

Рис. 2. ПЗУ, состоящее из диодной матрицы и дешифратора адреса.

Репрограммируемое постоянное запоминающее устройство РППЗУ, называемое также стираемым ПЗУ, допускает неоднократное стирание информации с помощью программатора. Это облегчает исправление обнаруженных ошибок и позволяет изменять содержимое памяти.

Полупроводниковые ПЗУ могут быть диодными и транзисторными.

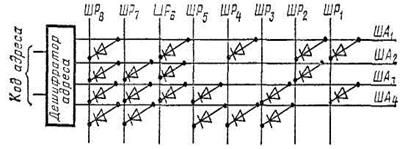

На рис. 2 изображено ПЗУ, состоящее из диодной матрицы и дешифратора адреса. Горизонтальные шины матрицы — адресные; вертикальные — разрядные, с них снимаются восьмиразрядные двоичные числа, записанные в ПЗУ. Если, к примеру, с выхода дешифратора возбуждается адресная шина ША2 то «лог. 1» проходит с нее через диоды на разрядные шины ШР2, ШР6, ШР7, ШР8, сообщая им высокий потенциал,— на выходе устанавливается двоичное число 11100010. Аналогично, при возбуждении других адресных шин на выходах устанавливаются три других двоичных числа.

Заметим, что диодная матрица (рис. 2) является совокупностью элементов ИЛИ. Каждый из них состоит из диодов, подключенных к одной разрядной шине, а входами элемента являются адресные шины.

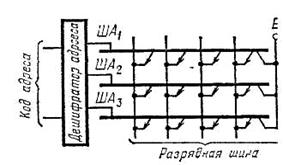

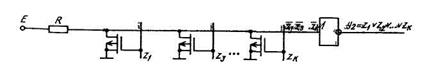

На рис. 3 приведена структура ИС ПЗУ на многоэмиттерном транзисторе. При возбуждении одной из ША отпирается транзистор, база которого присоединена к этой шине. Благодаря этому возбуждаются те разрядные шины, к которым присоединены эмиттеры этого транзистора. В ПЗУ (рис. 3) записаны три четырехразрядных слова (1001, 0011, 1010), каждое устанавливается на разрядных шинах при возбуждении соответствующей адресной шины.

Рассмотрим кратко программируемые ПЗУ. В ИС ПЗУ (см. рис. 3) при изготовлении все эмиттеры соединяются с разрядными шинами через плавкие перемычки. При программировании изготовителем или заказчиком часть их расплавляется импульсами тока, которые пропускают через определенные эмиттеры. В результате нарушаются некоторые связи источника Е с разрядными шинами, что обеспечивает появление логических нулей в определенных разрядах считываемого числа. Занесение новой информации в такие ПЗУ, связанное с необходимостью восстановить нарушенные связи, невозможно.

Рис. 3. Структура ИС ПЗУ на многоэмиттерном транзисторе.

Элементы перепрограммируемых ПЗУ выполняются на основе

МОП-транзисторов определенных структур. Одни из них допускают запись информации при воздействии импульса напряжения и ее стирание при ультрафиолетовом облучении, а другие — запись и стирание под воздействием только напряжений (разной полярности и значения).

Наибольшую емкость при наименьшей потребляемой мощности имеют ПЗУ, построенные на n-канальных МОП-транзисторах. В масочных ПЗУ информация записывается при изготовлении ПЗУ на заводе заменой одного из фотошаблонов слоя коммутации. Этот фотошаблон выполняется в соответствии с пожеланиями заказчика по картам заказа. Перечень возможных вариантов карт заказов приводится в технических условиях на ИС ПЗУ. Такие ПЗУ строятся на основе матриц диодов биполярных или МОП-транзисторов. Диоды включены в схеме ПЗУ в тех пересечениях матрицы, которые соответствуют записи «1», и отсутствуют в тех местах, где должны быть записаны «0».

Внешние цепи управления диодных ПЗУ просты. Так как матрицы представляют собой элементы с гальваническими связями, то на выходе появляются почти такие же постоянные уровни напряжения, как и входные сигналы, поэтому отпадает необходимость в выходном регистре для хранения информации. В масочных ПЗУ, построенных на основе биполярных транзисторов, единицы записываются в те ЗЭ матрицы, где базы транзисторов присоединяются к входной линии. Базы транзисторов, соответствующих ячейкам матрицы, в которых должны храниться нули, не подключаются ко входным шинам.

Аналогичные ЗУ на МОП-транзисторах проще, чем ЗУ на биполярных элементах. Они представляют собой полные матрицы, в которых при записи «1» затвор подключается ко входу, а при записи «0» — не подключается. Масочные ПЗУ отличаются высокой надежностью, но не очень удобны потребителю, поскольку невозможно оперативно изменять информацию в ПЗУ без изготовления новой ИС.

Более удобны электрические программируемые ПЗУ, однако они дают возможность только однократной записи нужной информации у потребителя путем разрушения элементов структуры ПЗУ под действием приложенного электрического напряжения или тока. Разрушаемыми элементами структуры могут быть специальные проводящие перемычки из металлической или поликремневой пленки, а также тонкий слой диэлектрика или p-n-переходы.

ТРЕТИЙ ВОПРОС

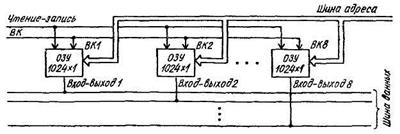

Постоянные и перепрограммируемые ЗУ отличаются друг от друга емкостью, разрядностью и числом входов ВК. ПЗУ имеют обычно словарную организацию. Функциональная схема ПЗУ показана на рис. 4. С помощью сигнала ВК можно отключать буферный регистр от шины данных. В ПЗУ имеется специальный вход «Ввод программы», посредством которого производится программирование ПЗУ.

Рис. 4. Функциональная схема ПЗУ на 512 X 8 разрядных слов.

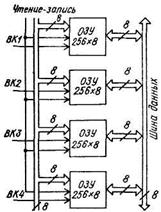

Для получения требуемого объема памяти и увеличения разрядности ее можно наращивать как по «горизонтали», так и по «вертикали».

Рис. 5. Горизонтальное наращивание памяти с целью получить

длину ячеек в8 бит при объеме 1024 слов (1024×8).

Требуемая разрядность памяти достигается путем горизонтального наращивания (рис. 5). При этом фиксируется количество слов памяти. Требуемый объем памяти при фиксированной разрядности слов можно получить наращиванием по «вертикали» (рис. 5).

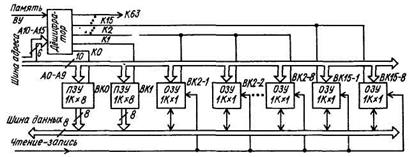

В целях получения требуемой организации памяти обычно используются оба способа ее наращивания. Пример организации памяти микро-ЭВМ, предназначенной для обработки сигналов, показан на рис. 6.

Микро-ЭВМ, работающая с такой памятью, имеет длину слова в 8 разрядов и шестнадцатиразрядную адресную шину. Адресные входы каждой БИС подключены к 10 младшим разрядам шины адреса для обеспечения возможности обращения к каждой из ячеек соответствующей БИС.

Рис.6. Вертикальное наращивание памяти с целью получить

объем ячеек 1024 слов при длине 8 бит (1024×8).

Рис. 7. Функциональная схема устройства памяти микро-ЭВМ.

Шесть старших разрядов необходимы для выделения с помощью дешифратора одного из 64 управляющих сигналов ВК.

В схеме, изображенной на рис. 7, из 64 управляющих сигналов для управления памятью необходимр только 16 (ВКО—ВК15), остальные (с ВК16 по ВК63) могут быть использованы для расширения объема памяти. Увеличение объема ППЗУ в этой схеме реализовано путем наращивания по «вертикали», увеличение разрядности ОЗУ — наращиванием по «горизонтали», а необходимый объем памяти ОЗУ — наращиванием по «вертикали».

Как отмечалось выше, в настоящее время существуют: ПЗУ, программируемые при изготовлении; ПЗУ, программируемые пользователем, и ППЗУ. ПЗУ первого типа программируются на одном из последних технологических этапов их изготовления. Программирование производится за счет металлизации требуемых промежутков в схеме. Фотошаблон, с помощью которого производится металлизация, достаточно дорог в изготовлении. Поэтому программирование этим способом выгодно только при крупносерийном производстве таких ПЗУ.

Пример ПЗУ на МОП-транзисторах показан на рис. 8. Тут операция «ИЛИ—НЕ» реализуется с помощью нормально закрытых МОП-транзисторов. Промежутки находятся в цепи истока каждого транзистора. Если поставить перемычку, то будет логический нуль в данном разряде; если перемычки нет, то будет логическая единица.

Рис. 8. ПЗУ на МОП-транзисторах, программируемое с помощью маски.

В ПЗУ второго типа используются перемычки в виде плавких вставок-предохранителей, которые избирательно пережигаются с помощью тока достаточной силы, который формируется посредством специального устройства, называемого программатором.

Постоянные ЗУ третьего типа можно программировать, стирать и программировать заново; такие ПЗУ называются перепрограммируемыми (ППЗУ). Как отмечалось, в ППЗУ используются схемы, изготовленные по МНОП- и ЛИЗМОП-технологии.

Программирование их производится с помощью специальных программаторов, а стирание информации — ультрафиолетовым излучением достаточной интенсивности.

Література:

1. М.В. Напрасник «Микропроцессоры и микроЭВМ», стр: 62-66.

2. Б.Я. Лихтциндер «Микропроцессоры и вычислительные устройства в радиотехнике», стр: 95-97.

3. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования», стр: 156-159.

4. Э.В. Евреинов «Цифровая и вычислительная техника», стр: 213-216.

ЗАНЯТИЕ 1.3.4 Матричные и трансформаторные типы ПЗУ.

ВОПРОСЫ ЗАНЯТИЯ:

1. Организация памяти на элементах с зарядовой связью.

2. Память на цилиндрических магнитных доменах.

3. Программируемые логические матрицы.

ПЕРВЫЙ ВОПРОС

ПЗС-память состоит из цепочек близко расположенных МОП-емкостей (рис. 1). Бит информации в ПЗС-памяти хранится в виде уровня заряда в элементах. Для сохранения разделенных зарядовых пакетов и передачи их в соседние элементы отдельно подается сигнал многофазной синхронизации.

Рис. 1. Структура ПЗС в режимах хранения (а) и передачи заряда (б).

Рис. 2. Организация ПЗС ЗУ с произвольно выбираемыми параллельными регистрами.

В каждом элементе напряжение на одном электроде отличается от других и поэтому образуется «потенциальная яма», которая захватывает заряд в элементе. Используя многофазную синхронизацию, можно перемещать «потенциальную яму» от одного электрода к следующему, а следовательно, смещать соответствующий захваченный заряд, что приводит к сдвигу информации на один бит при выполнении полного цикла сдвигов.

ПЗС-память можно считать длинным регистром. Частота сдвига таких регистров лежит в пределах от 50 кГц до 5 МГц. ПЗС-регистр аналогичен динамическому ЗУ, так как хранимые заряды в элементе памяти уменьшаются из-за токов утечки и потерь при передаче. Для компенсации этих потерь ПЗС-память организуется в виде нескольких кольцевых регистров сдвига, выход которых для рециркуляции через усилители регенерации подается на вход.

ПЗС-память предназначена для замены дисков с фиксированной головкой, а также используется в качестве быстрой вспомогательной массовой памяти. Здесь центральный процессор выдает в систему ПЗС-памяти начальный адрес и число передаваемых слов. К достоинствам ПЗС-памяти относятся простота элемента ЗУ, малый размер ячейки, небольшая потребляемая мощность. Память на ПЗС-элементах относится к элементам функциональной электроники.

ПЗС-память организуется как система сдвиговых регистров с соответствующими схемами управления. Наиболее быстродействующая ПЗС-память при малой потребляемой мощности и организацией в виде произвольно выбираемых параллельных регистров (рис. 2) имеет емкость 64 Кбит и организована как 16 произвольно выбираемых регистров по 4 Кбит каждый. Дешифратор выбирает один из 16 регистров. Сдвиг осуществляется сразу во всех 16 регистрах. При обращении к одному из регистров во всех остальных рециркулируется и регенерируется информация. Время выборки произвольного бита (время ожидания) на частоте 5 МГц равно 400 мкс. Потребляемая мощность 3,5 мкВт/бит на частоте 5 МГц и 0,6 мкВт/бит в режиме хранения.

ВТОРОЙ ВОПРОС

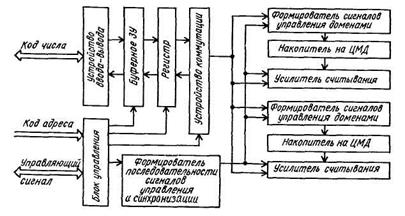

Запоминающие устройства на ЦМД используются в качестве внешних ЗУ. Емкость таких ЗУ в настоящее время достигает более 1 Мбит (К1602РУ2А). ЗУ на ЦМД энергонезависимы и позволяют хранить до 107 бит информации на площади в 1 см2 при малой потребляемой мощности.Для функционирования ЗУ на ЦМД необходимы устройства сопряжения: формирователи импульсов токов точной амплитуды и длительности, управляемые от стандартных ТТЛ-схем; усилитель считывания; блоки управления и синхронизации. ЗУ на ЦМД имеют малые размеры, а следовательно, их можно размещать на плате совместно с МП. Организация памяти одного из вариантов ЗУ на ЦМД показана на рис. 3.

Рис. 3. Организация памяти ЗУ на ЦМД.

ТРЕТИЙ ВОПРОС

Устройство управления ЭВМ имеет большое количество входных переменных (40—50) и выходных функций (50—70). Для разработки такого УУ с применением ПЗУ потребовалось бы ПЗУ с огромным объемом памяти (240×50 бит). Существуют различные способы снижения разрядности памяти ПЗУ. Это — введение узла анализа входных линий для снижения разрядности адреса либо применение ЗУ с адресным доступом, соединенных в несколько последовательных уровней. Однако оба эти способа снижают быстродействие системы

Отмеченных недостатков не имеют УУ на программируемых логических матрицах (ПЛМ). Кроме того, ПЛМ может применяться в качестве ЗУ, преобразователя кодов, генератора логических функций, выполнять произвольные логические операции и т. п.

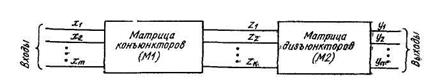

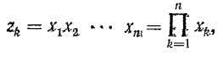

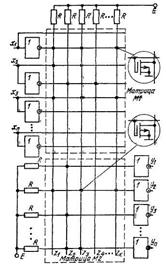

Структурная схема ПЛМ показана на рис. 4. ПЛМ состоит из двух матриц. Матрица M1 формирует k конъюнкций входных переменных, а матрица М2 — п дизъюнкций от конъюнкций M1. Число входов может достигать десятков, а число цепей Zl, Z2, ..., Zk — более ста.

Рис. 4. Структурная схема ПЛМ.

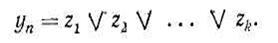

Принципиальная схема ПЛМ изображена на рис. 5. При построении матриц.M1 и М2 на пересечении горизонтальных и вертикальных цепей включаются полупроводниковые биполярные или МОП-элементы. Входные сигналы х1,x2, ..., хп коммутируются через транзисторы с информационными шинами, образуя логические произведения тех входных переменных, соединения с актами которых были произведены.

Прямые и обратные значения входных сигналов х1, х2, ... , хп образуют на выходах z1, z2, ... , zk функции

где xk может принимать значения xk,  или 1(единица будет в случае отсутствия связи, с переменной хк).

или 1(единица будет в случае отсутствия связи, с переменной хк).

Количество функций zk будет зависеть от числа логических элементов, формирующих вертикальные шины. Сформированные аналогично

выходные сигналы уп соответствуют уравнению

Принцип реализации операции конъюнкции применительно к рис. 5 показан на рис. 6, а дизъюнкции — на рис. 7

Рис. 5 Принципиальная схема ПЛМ.

Рис 6. Принцип реализации операцииконъюнкции в ПЛМ по рис 5.

Рис 7. Принцип реализации операции дизъюнкции в ПЛМ по рис. 5.

Отличие ПЗУ отПЛМ состоит в способе адресации информационного поля данных, в распределении информационных полей, возможности одновременного опроса нескольких формируемых функций. Разные адреса могут определять одну и ту же формирующую функцию. Возможны варианты определения более одной переходной функции с помощью одного адреса. Используя два различных адреса, можно адресовать одну и ту же область данных матрицы для обращения к микропрограммам по различным адресам, Это дает возможность перехода к микропрограммам из различных текущих условий без применения специальных микрокоманд перехода.

Структура ПЛМ позволяет анализировать большое количество входных переменных и увеличивать их число без увеличения накопительной матрицы. В зависимости от организации межсоединений шин в матрицах ПЛМ, как и ПЗУ, бывают программируемые в процессе изготовления, программируемые пользователем и перепрограммируемые. Программирование ПЛМ производится аналогично программированию ПЗУ.

Литература:

1. Б.Я. Лихтциндер «Микропроцессоры и вычислительные устройства в радиотехнике», стр: 91-93, 97-99.

ЗАНЯТИЕ 1.3.5 Назначение, классификация внешних запоминающих

устройств (ВЗУ).

ВОПРОСЫ ЗАНЯТИЯ:

1. Назначение и состав ВЗУ.

2. Классификация и основные характеристики ВЗУ.

3. Краткая характеристика основных типов накопителей ВЗУ.

ПЕРВЫЙ ВОПРОС

Внешние запоминающие устройства (ВЗУ) - это устройства большого объема (сотни тысяч байт и более), предназначенные для длительного хранения данных, создания архива данных (в том числе и на съемных носителях) и обмена этими данными с оперативными запоминающими устройствами микропроцессорных систем.

В общем случае ВЗУ состоит из накопителя и контроллера.

Накопителем ВЗУ называется часть внешнего запоминающего устройства, непосредственно принимающая информацию, преобразующая ее (при необходимости) в форму, удобную для хранения (например, в магнитное поле), осуществляющая хранение этой информации и преобразование в электрические сигналы при считывании.

Накопитель ВЗУ состоит из устройства преобразования информации, механизма (при необходимости) и носителя информации.

Устройство преобразования информации включает в себя усилители записи и считывания, магнитные головки (для магнитных ВЗУ) и другие средства, необходимые для прямого и обратного преобразования цифровых кодов в форму, удобную для хранения.

Механизм, иногда называемый приводом, обеспечивает перемещение носителя информации относительно органов записи и считывания.

Носителем информации является изделие, осуществляющее непосредственное хранение информации на основе определенных физических явлений. Носитель может быть магнитным (диск, лента, барабан), оптическим (фотопленка, голограмма, оптический лазерный диск) и т. п. Носитель может быть постоянным, т.е. неотделимым от накопителя, или съемным, что обеспечивает возможность создания архива данных произвольного объема.

Контроллером ВЗУ называется устройство, обеспечивающее управление работой накопителя и сопряжение с интерфейсом микропроцессорной системы.

ВТОРОЙ ВОПРОС

Для эффективной обработки данных необходимо обеспечить при минимальных затратах хранение больших объемов информации и быстрый доступ к ней. Эти требования противоречивы и при современном уровне технологии компромисс между емкостью, быстродействием памяти и затратами на нее достигается за счет создания, как мы ранее отмечали, иерархической структуры, включающей в себя сверхоперативный, основной, внешний и архивный уровни. Информация для центрального процессора(ЦП) непосредственно доступна только из ЗУ сверхоперативного и основного уровней. Каждый последующий уровень в рамках одной ЭВМ характеризуется большей емкостью и меньшим быстродействием ЗУ. Внешний и архивный уровни образуют систему внешней памяти; в ее состав входят разнородные ВЗУ (их часто называют накопителями), контроллеры ВЗУ, а также носители информации и хранилища для них.

Дата добавления: 2015-12-08; просмотров: 5569;