Наиболее распространена оценка схемы по двум параметрам— задержке Т и аппаратурным затратам W.

Значения ряда других важных параметров цифрового блока—потребляемой мощности, частоты отказов, стоимости — при заданной элементной базе и априорно невысокой точности оценок в первом приближении допустимо считать пропорциональными аппаратурным затратам.

В дальнейшем методика оценки качества схем иллюстрируется на примере именно этой пары параметров — Т и W.

При работе на микросхемах задержка Т схемы достаточно объективно оценивается значением среднего времени задержки распространения tзд.р.ср входящих в нее элементов. В рамках одной серии обычно целесообразно полагать, что задержки всех логических элементов россыпи — И-НЕ, И, И-ИЛИ-НЕ, М2 — одинаковы и равны некоторой усредненной для данной серии величине t.

Для серий К155 и К555, например, значение t можно принять равным 20 нc.Задержку более сложных микросхем средней интеграции, целесообразно округлять до значения, кратного целому t или его половине.

Аппаратурные затраты W функционального узла оценивают различными способами. Хорошие результаты дает оценка величины W площадью, занимаемой узлом на плате или кристалле. При использовании микросхем площадь платы при прочих равных условиях приблизительно пропорциональна числу корпусов. Размеры корпусов различны, поэтому их приходится приводить к какому-то единому, принятому за единицу. В качестве масштаба можно использовать отношение площадей корпусов или чисел их выводов. Можно оценивать величину W схемы и непосредственно суммарным числом выводов всех корпусов.

При оценке задержки схем, предназначенных для воплощения на кристалле матричной БИС, следует иметь в виду, что для целого ряда технологий задержка средней межэлементной связи на кристалле соизмерима с задержкой самого логического элемента. Поэтому действительное значение задержки схемы на кристалле становится известным лишь после размещения на нем элементов и трассировки связей. Это приводит к тому, что методика оценки задержки схемы суммированием задержек логических элементов дает при работе на кристалле заметно большую погрешность, чем та же методика при работе на отдельных микросхехмах.

Аппаратурные затраты схем, предназначенных для размещения на матричных БИС, часто можно оценивать числом логических элементов или библиотечных ячеек, содержащих сразу несколько элементов наподобие корпусов микросхем.

Пример:

На логических микросхемах серии К155 построить несколько вариантов схем, реализующих заданную минимальную ДНФ (2.1). Сравнить полученные результаты.

. (2.1)

. (2.1)

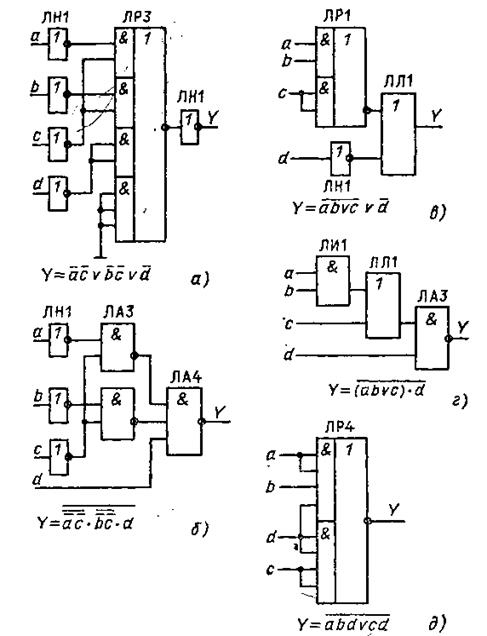

Схемная реализация этой формулы представлена на рис. 2.5, а. Поскольку на основании данных справочника задержки распространения элементов ЛРЗ и ЛН1 серии К155 одинаковы, задержка всей схемы равна Т=3t.

Аппаратурные затраты состоят из пяти инверторов ЛН1, каждый из которых занимает 1/6 корпуса, и элемента И-ИЛИ-НЕ – ЛРЗ, занимающего целый корпус. Итого для схемы по рис. 2.5, а W=5•1/6+1=22/12 корпуса.

Рис. 2.5. Различные варианты схемной реализации

Дата добавления: 2015-08-21; просмотров: 1025;