Микросхема ТМ2

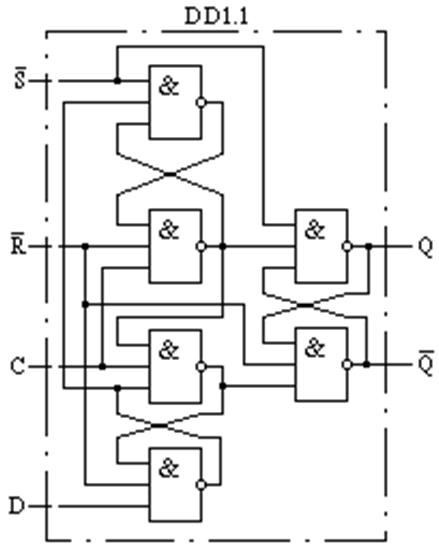

Микросхема ТМ2 содержит два независимых комбинированных D-триггера, имеющих общую цепь питания. У каждого триггера имеется один информационный вход D, вход синхронизации С и два дополнительных входа -S и -R независимой асинхронной установки триггера в единичное и нулевое состояния, а также комплементарные выходы Q и -Q (рис. 2.46).

Входы -S и -R - асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе, активный уровень для них низкий (т. е. инверсные входы -S и -R).

Рис. 2.46. Структура D-триггера микросхемы ТМ2

Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы -S и -R. В это время входы D и С не влияют.

Если на входы -S и -R одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера Q и –Q будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов -S и -R состояние триггера будет неопределенным. Поэтому комбинация -S=-R=0 для этих входов является запрещенной.

Загрузить в триггер микросхемы ТМ2 входные уровни (логическую 1 или 0) можно, если на входы -S и -R подать напряжение высокого уровня: -S=-R=1. Сигнал со входа D передается на выходы триггера при поступлении положительного перепада импульса на вход С (изменение от низкого к высокому 0–>1). Однако, чтобы D-триггер переключался правильно (согласно таблице состояний, табл. 2.24), необходимо уровень на входе D зафиксировать заранее, т. е. до прихода перепада на вход С.

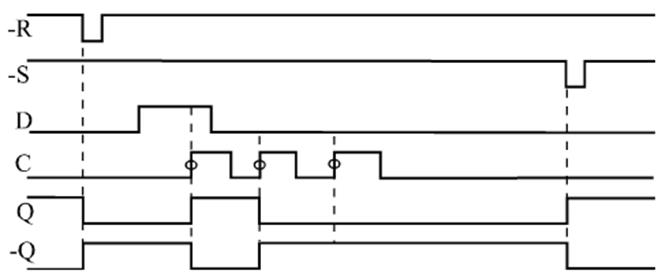

Таблица 2.24. Состояния микросхемы ТМ2

| Режим работы | Входы | Выходы | ||||

| –S | –R | D | C | Q(t+1) | –Q(t+1) | |

| Асинхронная установка | X | X | ||||

| Асинхронный сброс | Х | Х | ||||

| неопределенность | Х | Х | ||||

| Загрузка "1" (установка) | 0–>1 | |||||

| Загрузка "0" (сброс) | 0–>1 | |||||

| Не изменяется | Х | Q(t) | –Q(t) | |||

| Не изменяется | Х | Q(t) | –Q(t) | |||

| Не изменяется | Х | 1–>0 | Q(t) | –Q(t) |

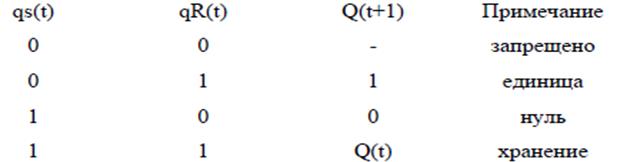

Рис. 7.4. Временная диаграмма работы D-триггера ТМ2

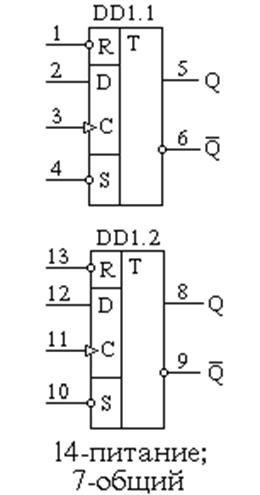

Цоколевка микросхемы ТМ2 приведена на рис. 2.47.

Рис. 2.47. Условное обозначение и цоколевка микросхемы ТМ2

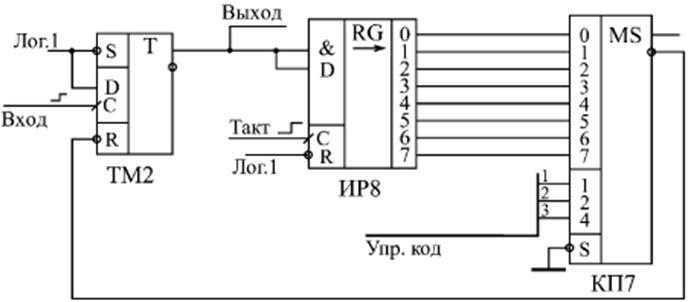

Сдвиговые регистры могут также использоваться для формирования импульсов заданной длительности, причем длительность импульса может задаваться управляющим кодом, то есть быть программно управляемой. На рис. 8.21 приведена возможная схема такого формирователя.

Рис. 8.21. Формирователь импульсов с длительностью, задаваемой управляющим кодом

В исходном состоянии (до прихода положительного фронта входного сигнала) триггер сброшен в нуль и находится в режиме хранения (–R=1, –S=1), на всех выходах регистра сдвига - нули, на инверсном выходе мультиплексора - единица. На мультиплексор подан управляющий код, определяющий длительность выходного сигнала. При поступлении положительного фронта входного сигнала триггер перебрасывается в единицу (–R=1; –S=0) (начинается передача выходного единичного сигнал), и этот единичный сигнал начинает последовательно сдвигаться регистром сдвига по каждому фронту тактового сигнала. При этом микросхема ТМ2 переходит в режим хранения (–R=1; –S=1) с постоянной выдачей единичного сигнала.

Пусть управляющий код равен 5. Тогда в тот момент, когда на выходе 5 сдвигового регистра появится единица, она будет передана на выход мультиплексора КП7 с инверсией. При этом нулевой сигнал на входе –R триггера сбросит триггер в нуль (–R=0; –S=1), то есть выходной сигнал закончится.

Таким образом, длительность выходного сигнала будет определяться управляющим кодом. Погрешность установки этой длительности равна одному периоду тактового сигнала и зависит от временного сдвига между фронтом входного сигнала и фронтом ближайшего к нему тактового импульса.

Сдвиговые регистры могут также использоваться для умножения и деления двоичных чисел на 2n, где n - целое число, большее нуля. Сдвиг двоичного числа вправо (в сторону младших разрядов) на один разряд равносилен делению на 2. Сдвиг двоичного числа влево (в сторону старших разрядов) на один разряд равносилен умножению на 2.Для того чтобы сдвиговый регистр умножал и делил двоичный код, надо всего лишь записать этот код в регистр и сдвинуть его нужное количество раз вправо или влево. Наиболее удобен для этого регистр ИР13. При этом необходимо, чтобы в освободившиеся разряды вдвигались нули, то есть на входы расширения DR и DL регистра надо подать нулевые сигналы.

Ещё одно применение сдвигового регистра - это генератор случайной последовательности сигналов или случайной последовательности кодов. Строго говоря, последовательности будут не полностью случайные, а квазислучайные, то есть будут периодически повторяться, но период этот довольно большой. Случайные последовательности сигналов и кодов широко применяются в тестирующей аппаратуре, в генераторах шума, в логических игровых устройствах.

Задача состоит в том, чтобы выходной сигнал или код менял свое состояние случайно (или почти случайно). Сигнал должен случайно переключаться из 0 в 1 и из 1 в 0, а код должен случайно принимать значения из диапазона от 0 до (2N–1), где N - число разрядов кода (например, от 0 до 255 при 8-разрядном коде). Псевдослучайные последовательности имеют то преимущество перед истинно случайными, что они - предсказуемые и периодические, но в этом же и их недостаток.

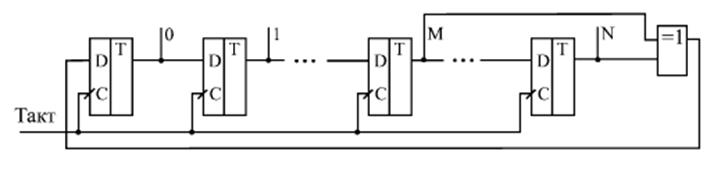

Структура генератора квазислучайной последовательности на сдвиговом регистре представлена на рис. 8.22. Она представляет собой регистр сдвига с параллельными выходами (например, ИР8), несколько (минимум два) выходных сигналов которого объединены с помощью элемента Исключающее ИЛИ, с выхода которого сигнал подается на вход регистра, замыкая схему в кольцо.Схема тактируется сигналом с частотой fT.

Рис. 8.22. Структура генератора псевдослучайной последовательности

Выбор номеров разрядов для подключения обратной связи представляет собой непростую задачу, но существуют справочные таблицы, в которых они приведены. В любом случае одна из точек подключения - выход старшего разряда. В табл. 8.9 приведены точки подключения обратной связи для регистров сдвига с разным количеством разрядов N (номера разрядов считаются от нуля).

Таблица 8.9. Точки подключения обратной связи

N

| ||||||

| Выходы | 6,5 | 7,6, 4,2 | 14,13 | 15,13, 12,10 | 23,22, 21,16 | 30,17 |

Период выходной последовательности генератора составляет (2N-1) тактов, где N - количество разрядов регистра сдвига. За это время каждое из возможных значений выходного кода (кроме одного) встречается один раз.

Выходной код 000  0 представляет собой запрещенное состояние, так как он блокирует работу генератора, воспроизводя сам себя снова и снова. Но в то же время получиться такой нулевой код может только сам из себя, поэтому достаточно обеспечить, чтобы его не было при включении питания схемы.

0 представляет собой запрещенное состояние, так как он блокирует работу генератора, воспроизводя сам себя снова и снова. Но в то же время получиться такой нулевой код может только сам из себя, поэтому достаточно обеспечить, чтобы его не было при включении питания схемы.

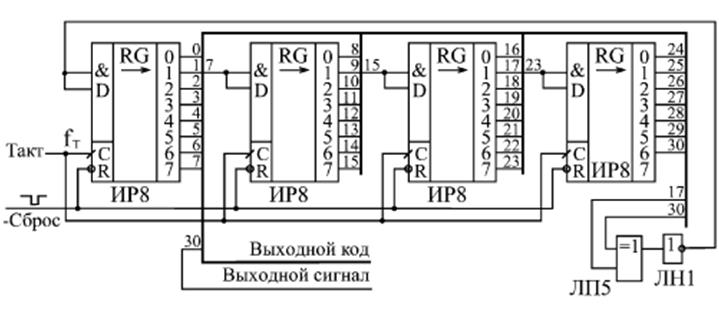

Рис. 8.23. 31-разрядный генератор псевдослучайной последовательности на регистрах сдвига

На рис. 8.23 показана практическая схема генератора псевдослучайной последовательности на 31-разрядном сдвиговом регистре, состоящем из 4 микросхем ИР8. Обратная связь осуществляется с выходов 30 и 17 регистра через двухвходовой элемент Исключающее ИЛИ с инвертором. Из-за применения инвертора запрещенным состоянием генератора является код 1111...1 (а не код 000...0), который в данном случае исключается очень просто - начальным сбросом регистров в нуль при включении питания по сигналу -Сброс. Генератор выдает квазислучайную последовательность 31-разрядных кодов со всех выходов регистра, а также квазислучайную последовательность нулей и единиц на любом из выходов регистра. Такой генератор использовала известная фирма Hewlett–Packard в своем генераторе шума.

Дата добавления: 2015-08-21; просмотров: 6576;