Лекция 18.

Тема 9.3. Сегментация памяти в автоматах с программируемой логикой.

Функциональные схемы автоматов на программируемой логике и сегментацией памяти.

Вопросы оптимизации

Запоминающие устройства, используемые в автоматах с программируемой логикой, имеют достаточно большую емкость, а значит и большую длину адресной части микрокоманды. Большая емкость ЗУ позволяет хранить в нем не одну, а множество микропрограмм, реализующих разные функции, причем каждой из них требуется небольшой объем памяти.

Для того, что бы максимально использовать ЗУ и при этом не увеличивать длину адресной части микрокоманды используют прием, который называется «сегментация ЗУ». Весь объем ЗУ делится на сегменты (страницы), а адрес А, поступающий на адресный вход ЗУ рассматривается как адрес сегмента Ас (обычно старшие разряды адреса) и адрес ячейки в сегменте Ая (обычно младшие разряды адреса). Число сегментов обычно выбирают равным целой степени двойки (2, 4, 8 и т.д. сегментов).

Микропрограммы в ЗУ необходимо размещать так, чтобы было как можно меньше переходов из сегмента в сегмент, а значит лучше всего, что бы первая микрокоманда микропрограммы размещалась в первой ячейке некоторого сегмента. В этом случае в адресной части микрокоманды в качестве адреса перехода будет записываться адрес ячейки Ая и только при необходимости перехода в другой сегмент микрокоманда должна содержать полный адрес: Ас и Ая. Полный адрес необходимо так же записать в регистр адреса при выборе той или иной микропрограммы в ЗУ.

Использование сегментации ЗУ в автоматах с принудительной адресацией и одноадресной микрокомандой рассмотрим на примере автомата, описанного ГСА рис.5 с кодированием групп микрокоманд (как в примере на рис.28).

Пусть ЗУ имеет 8-ми разрядный адрес (емкость ЗУ - 256 слов). Представим ЗУ состоящим из 32-х сегментов, в каждом из которых – 8 ячеек. Таким образом, 5 старших разрядов адреса – это адрес сегмента (Ас), а 3 младших – адрес ячейки (Ая).

Формат микрокоманды практически не отличается от используемого в примере рис.31. Для записи признака перехода из одного сегмента в другой в микрокоманду введем дополнительный разряд (0): значение этого разряда «0» - обычная микрокоманда (как в примере рис.31), если «1» - то все остальные 8 разрядов микрокоманды интерпретируются как полный адрес перехода А = Ас Ая.

Пусть адрес первой микрокоманды микропрограммы А=00000011, т.е. Ас=00000, Ая=011. Микропрограмма с комментариями приведена ниже.( 90 бит )

Первые 3 строки (по смыслу) совпадают с примером рис.31. В нулевом разряде записан «0», в адресной части – Ая сегмента с адресом Ас=00000.

Конструкция «GOTO-S Ас, Ая » в комментариях означает переход по полному адресу А = Ас Ая. Следует обратить внимание на то, что в нулевом разряде этой микрокоманды - «0», а в операционной части – Ас (а не Уi ).

По аналогии с примером (рис.31), в 4-ой строке следовало бы записать конструкцию: «a 3; IF X 2 = 0 THEN GOTO 7», однако Ая = 7 – это адрес последней ячейки сегмента с адресом Ас=0, и при X 2 = 1 адрес Ая = 7 + X 2 = 8. Поскольку под Ая отведено 3 разряда, то после этой операции получим Ая=0. Поэтому в 4-ой строке «GOTO-S 1,0» - переход в сегмент с Ас=00001 в ячейку с Ая=000. 5-ая строка при этом не используется.

В 6-ой строке конструкция «a 3; IF X2 = 0 THEN GOTO 1;» по смыслу совпадает с конструкцией «a 3; IF X 2 = 0 THEN GOTO 4;» (рис.31), причем «GOTO-S 0,3;» в 8-ой строке – переход в начало микропрограммы (где «a 0; IF X3 = 0 THEN GOTO 3;» эквивалентно «a 0; IF X3 = 0 THEN GOTO 0;»(рис.31).

В 7-ой строке «a 4; IF ØX1 = 0 THEN GOTO 3;» и далее «GOTO-S 0,5;» и «GOTO-S 1,0;» эквивалентно одной строке из примера рис.31 «a 4; IF ØX1 = 0 THEN GOTO 2;»

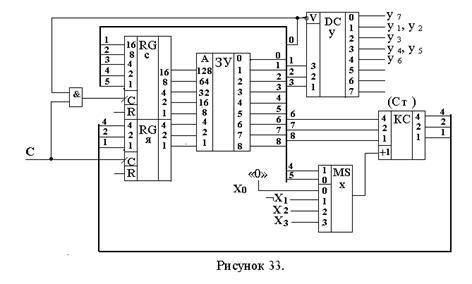

На рис.33 приведена функциональная схема автомата с принудительной адресацией и сегментацией ЗУ. Для упрощения в ней не показаны элементы, обеспечивающие запись в регистр адреса начального адреса микропрограммы.

Регистр адреса состоит из двух независимых регистров:RGс – регистр адреса сегмента и RGя – регистр адреса ячейки. Пока значение нулевого разряда слова равно «0» - разрешается работа дешифратора DСy и разряды слова 1..3 интерпретируются как код группы микрокоманд Уi. В RGя при каждом синхроимпульсе записывается Ая, формируемый КС (как в примере рис.31). Если значение нулевого разряда слова «1», то работа DСy запрещается (на всех выходах DСy – «0»), а импульс синхронизации через элемент «И» подается не только на вход С RGя , но и RGс. Происходит запись полного адреса перехода в оба регистра: А=Ас Ая.

Дата добавления: 2015-08-11; просмотров: 864;