Использование безразмерной величины . 5 страница

§ идентификации блока – способа нахождения блока на примыкающем сверху уровне;

§ замещения блока – выбора блока, заменяемого при промахе с целью освобождения места для нового блока;

§ согласования копий (стратегии записи) - обеспечения согласованности копий одних и тех же блоков, расположенных на разных уровнях, при записи новой информации в копию, находящуюся на более высоком уровне.

Самый быстрый, но и минимальный по емкости тип памяти — это внутренние регистры ЦП, которые иногда объединяют понятием сверхоперативное запоминающее устройство — СОЗУ. Как правило, количество регистров невелико, хотя в архитектурах с сокращенным набором команд их число может доходить до нескольких сотен. Основная память (ОП), значительно большей емкости, располагается несколькими уровнями ниже. Между регистрами ЦП и основной памятью часто размещают кэш-память, которая по емкости ощутимо проигрывает ОП, но существенно превосходит последнюю по быстродействию, уступая в то же время СОЗУ. В большинстве современных ВМ имеется несколько уровней кэш-памяти, которые обозначают буквой L и номером уровня кэш-памяти. На рис. 5.1 показаны два таких уровня. В последних разработках все чаще появляется также третий уровень кэш-памяти (L3), причем разработчики ВМ говорят о целесообразности введения и четвертого уровня — L4. Каждый последующий уровень кэш-памяти имеет большую емкость, но одновременно и меньшее быстродействие по сравнению с предыдущим. Как бы то ни было, по «скорости» любой уровень кэш-памяти превосходит основную память. Все виды внутренней памяти реализуются на основе полупроводниковых технологий и в основном являются энергозависимыми.

Долговременное хранение больших объемов информации (программ и данных) обеспечивается внешними ЗУ, среди которых наиболее распространены запоминающие устройства на базе магнитных и оптических дисков, а также точные ЗУ.

Наконец, еще один уровень иерархии может быть добавлен между основной памятью и дисками. Этот уровень носит название дисковой кэш-памяти и реализуется в виде самостоятельного ЗУ, включаемого в состав магнитного диска. Дисковая кэш-память существенно улучшает производительность при обмене информацией между дисками и основной памятью.

Иерархия может быть дополнена и другими видами памяти. Так, некоторые модели ВМ фирмы IBM включают в себя так называемую расширенную память (expanded storage), выполненную на основе полупроводниковой технологии, но имеющую меньшее быстродействие и стоимость по сравнению с ОП. Строго говоря, этот вид памяти не входит в иерархию, а представляет собой ответвление от нее, поскольку данные могут передаваться только между расширенной и основной памятью, но не допускается обмен между расширенной и внешней памятью.

Основная память

Основная память (ОП) представляет собой единственный вид памяти, к которой ЦП может обращаться непосредственно (исключение составляют лишь регистры центрального процессора). Информация, хранящаяся на внешних ЗУ, становится доступной процессору только после того, как будет переписана в основную память.

Основную память образуют запоминающие устройства с произвольным доступом. Такие ЗУ образованы как массив ячеек, а «произвольный доступ» означает, что обращение к любой ячейке занимает одно и то же время и может производиться в произвольной последовательности. Каждая ячейка содержит фиксированное число запоминающих элементов и имеет уникальный адрес, позволяющий различать ячейки при обращении к ним для выполнения операций записи и считывания.

Следствием огромных успехов в области полупроводниковых технологий стало изменение элементной базы основной памяти. На смену ЗУ на базе ферромагнитных колец пришли полупроводниковые микросхемы, использование которых в наши дни стало повсеместным[7].

Основная память может включать в себя два типа устройств: оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ).

Преимущественную долю основной памяти образует ОЗУ, называемое оперативным, потому что оно допускает как запись, так и считывание информации, причем обе операции выполняются однотипно, практически с одной и той же скоростью, и производятся с помощью электрических сигналов. В англоязычной литературе ОЗУ соответствует аббревиатура RAM — Random Access Memory, то есть «память с произвольным доступом», что не совсем корректно, поскольку памятью с произвольным доступом являются также ПЗУ и регистры процессора. Для большинства типов полупроводниковых ОЗУ характерна энергозависимость — даже при кратковременном прерывании питания хранимая информация теряется. Микросхема ОЗУ должна быть постоянно подключена к источнику питания и поэтому может использоваться только как временная память.

Вторую группу полупроводниковых ЗУ основной памяти образуют энергонезависимые микросхемы ПЗУ (ROM - Read-Only Memory). ПЗУ обеспечивает считывание информации, но не допускает ее изменения (в ряде случаев информация в ПЗУ может быть изменена, но этот процесс сильно отличается от считывания и требует значительно большего времени).

Блочная организация основной памяти

Емкость основной памяти современных ВМ слишком велика, чтобы ее можно было реализовать на базе единственной интегральной микросхемы (ИМС). Необходимость объединения нескольких ИМС ЗУ возникает также, когда разрядность ячеек в микросхеме ЗУ меньше разрядности слов ВМ.

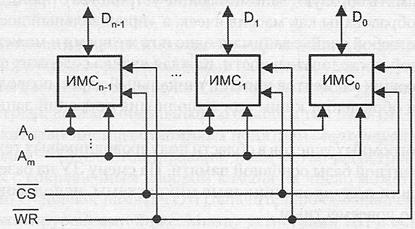

Увеличение разрядности ЗУ реализуется за счет объединения адресных входов объединяемых ИМС ЗУ. Информационные входы и выходы микросхем являются входами и выходами модуля ЗУ увеличенной разрядности (рис. 5.2). Полученную совокупность микросхем называют модулем памяти. Модулем можно считать и единственную микросхему, если она уже имеет нужную разрядность. Один или несколько модулей образуют банк памяти.

Рис. 5.2. Увеличение разрядности памяти

Для получения требуемой емкости ЗУ нужно определенным образом объединить несколько банков памяти меньшей емкости. В общем случае основная память ВМ практически всегда имеет блочную структуру, то есть содержит несколько банков.

При использовании блочной памяти, состоящей из В банков, адрес ячейки А преобразуется в пару (b, w), где b - номер банка, w - адрес ячейки внутри банка. Известны три схемы распределения разрядов адреса А между b и w.

§ блочная (номер банка b определяет старшие разряды адреса);

§ циклическая (b =А mod В; w =А div В);

§ блочно-циклическая (комбинация двух предыдущих схем).

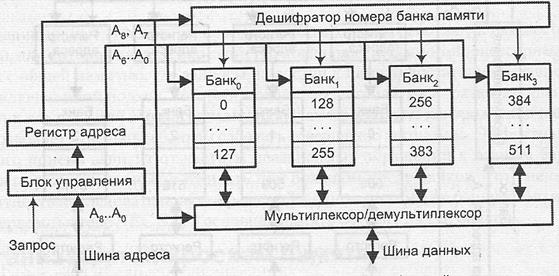

Рассмотрение основных структур блочной ОП будем проводить на примере памяти емкостью 512 слов (29), построенной из четырех банков по 128 слов в каждом. Типовая структура памяти, организованная в соответствии с блочной структурой, показана на рис. 5.3.

Рис. 5.3. Структура основной памяти на основе блочной схемы

Адресное пространство памяти разбито на группы последовательных и каждая такая группа обеспечивается отдельным банком памяти. Для обращения к ОП используется 9-разрядный адрес, семь младших разрядов которого (А6 - А0) поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку. Два старших разряда адреса (А8, А0) содержат номер банка. Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти, либо путем мультиплексирования информации (на рис. 5.3 показаны оба варианта). В функциональном отношении такая ОП может рассматриваться как единое ЗУ, емкость которого равна суммарной емкости составляющих, а быстродействие — быстродействию отдельного банка.

Расслоение памяти

Помимо податливости к наращиванию емкости, блочное построение памяти обладает еще одним достоинством — позволяет сократить время доступа к информации. Это возможно благодаря потенциальному параллелизму, присущему блочной организации. Большей скорости доступа можно достичь за счет одновременного доступа ко многим банкам памяти. Одна из используемых для этого методик называется расслоением памяти. В ее основе лежит так называемое чередование адресов (address interleaving), заключающееся в изменении системы распределения адресов между банками памяти.

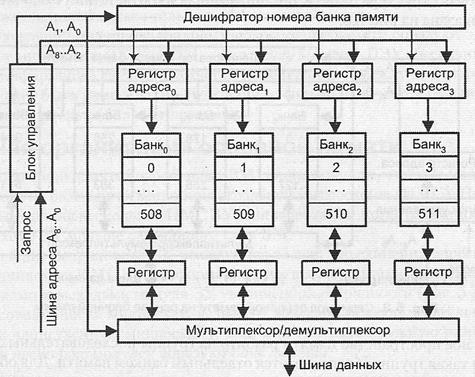

Прием чередования адресов базируется на ранее рассмотренном свойстве локальности по обращению, согласно которому последовательный доступ в память обычно производится к ячейкам, имеющим смежные адреса. Иными словами, если в данный момент выполняется обращение к ячейке с адресом 5, то следующее обращение, вероятнее всего, будет к ячейке с адресом 6, затем 7 и т. д. Чередование адресов обеспечивается за счет циклического разбиения адреса. В нашем примере (рис. 5.4) для выбора банка используются два младших разряда адреса (А1, А0), а для выбора ячейки в банке - 7 старших разрядов (А8 – А2).

Рис. 5.4. Блочная память с чередованием адресов по циклической схеме

Поскольку в каждом такте на шине адреса может присутствовать адрес только одной ячейки, параллельное обращение к нескольким банкам невозможно, однако оно может быть организовано со сдвигом на один такт. Адрес ячейки запоминается в индивидуальном регистре адреса, и дальнейшие операции по доступу к ячейке в каждом банке протекают независимо. При большом количестве банков среднее время доступа к ОП сокращается почти в В раз (В — количество банков), но при условии, что ячейки, к которым производится последовательное обращение, относятся к разным банкам. Если же запросы к одному и тому же банку следуют друг за другом, каждый следующий запрос должен ожидать завершения обслуживания предыдущего. Такая ситуация называется конфликтом по доступу. При частом возникновении конфликтов по доступу метод становится неэффективным.

В блочно-циклической схеме расслоения памяти каждый банк состоит из нескольких модулей, адресуемых по круговой схеме. Адреса между банками распределены по блочной схеме. Таким образом, адрес ячейки разбивается на три части. Старшие биты определяют номер банка, следующая группа разрядов адреса указывает на ячейку в модуле, а младшие биты адреса выбирают модуль в банке. Схему иллюстрирует рис. 5.5.

Рис. 5.5. Блочно-циклическая схема расслоения памяти

Традиционные способы расслоения памяти хорошо работают в рамках одной задачи, для которой характерно свойство локальности. В многопроцессорных системах с общей памятью, где запросы на доступ к памяти достаточно независимы, не исключен иной подход, который можно рассматривать как развитие идеи расслоения памяти. Для этого в систему включают несколько контроллеров памяти, что позволяет отдельным банкам работать совершенно автономно. Эффективность данного приема зависит от частоты независимых обращений к разным банкам. Лучшего результата можно ожидать при большом числе банков, что уменьшает вероятность последовательных обращений к одному и тому же банку памяти. Так, в суперкомпьютере NEC SX/3 основная память состоит из 128 банков.

Организация микросхем памяти

Интегральные микросхемы (ИМС) памяти организованы в виде матрицы ячеек, каждая из которых, в зависимости от разрядности ИМС, состоит из одного или более запоминающих элементов (ЗЭ) и имеет свой адрес. Каждый ЗЭ способен хранить один бит информации. Для ЗЭ любой полупроводниковой памяти характерны следующие свойства:

§ два стабильных состояния, представляющие двоичные 0 и 1;

§ в ЗЭ (хотя бы однажды) может быть произведена запись информации, посредством перевода его в одно из двух возможных состояний;

§ для определения текущего состояния ЗЭ его содержимое может быть считано.

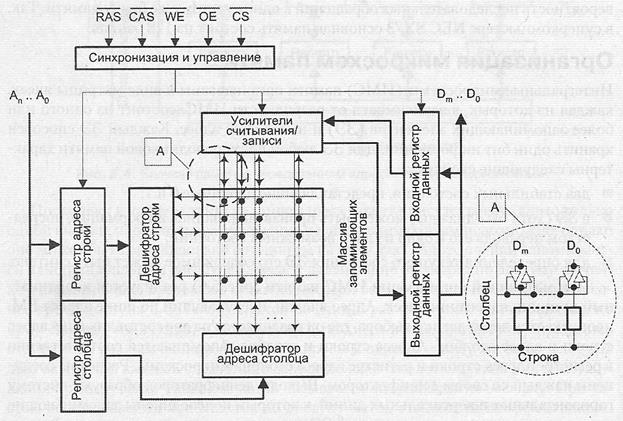

При матричной организации ИМС памяти (рис. 5.6) реализуется координатный принцип адресации ячеек. Адрес ячейки, поступающий по шине адреса ВМ, пропускается через логику выбора, где он разделяется на две составляющие: адрес строки и адрес столбца. Адреса строки и столбца запоминаются соответственно в регистре адреса строки и регистре адреса столбца микросхемы. Регистры соединены каждый со своим дешифратором. Выходы дешифраторов образуют систему

горизонтальных и вертикальных линий, к которым подсоединены запоминающие элементы матрицы, при этом каждый ЗЭ расположен на пересечении одной горизонтальной и одной вертикальной линии.

ЗЭ, объединенные общим «горизонтальным» проводом, принято называть строкой (row). Запоминающие элементы, подключенные к общему «вертикальному» проводу, называют столбцом (column). Фактически «вертикальных» проводов в микросхеме должно быть, по крайней мере, вдвое больше, чем это требуется для адресации, поскольку к каждому ЗЭ необходимо подключить линию, по которой будет передаваться считанная и записываемая информация.

Совокупность запоминающих элементов и логических схем, связанных с выбором строк и столбцов, называют ядром микросхемы памяти. Помимо ядра в ИМС имеется еще интерфейсная логика, обеспечивающая взаимодействие ядра с внешним миром. В ее задачи, в частности, входят коммутация нужного столбца на выход при считывании и на вход — при записи.

На физическую организацию ядра, как матрицы однобитовых ЗЭ, накладывается логическая организация памяти, под которой понимается разрядность микросхемы, то есть количество линий ввода/вывода. Разрядность микросхемы определяет количество ЗЭ, имеющих один и тот же адрес (такая совокупность запоминающих элементов называется ячейкой), то есть каждый столбец содержит столько разрядов, сколько есть линий ввода/вывода данных.

Для уменьшения числа контактов ИМС адреса строки и столбца в большинстве микросхем подаются в микросхему через одни и те же контакты последовательно во времени (мультиплексируются) и запоминаются соответственно в регистре адреса строки и регистре адреса столбца микросхемы. Мультиплексирование обычно реализуется внешней по отношению к ИМС схемой.

Рис. 5.6. Структура микросхемы памяти

Для синхронизации процессов фиксации и обработки адресной информации внутри ИМ С адрес строки (RA) сопровождается сигналом RAS (Row Address Strobe - строб строки), а адрес столбца (СА) - сигналом С AS (Column Address Strobe — строб столбца). Вторую букву в аббревиатурах RAS и CAS иногда расшифровывают как Access - «доступ», то есть имеется строб доступа к строке и строб доступа к столбцу. Чтобы стробирование было надежным, эти сигналы подаются с задержкой, достаточной для завершения переходных процессов на шине адреса и в адресных цепях микросхемы.

Сигнал выбора микросхемы CS (Crystal Select) разрешает работу ИМС и используется для выбора определенной микросхемы в системах, состоящих из нескольких ИМС. Вход WE (Write Enable — разрешение записи) определяет вид выполняемой операции (считывание или запись).

Записываемая информация, поступающая по шине данных, первоначально заносится во входной регистр данных, а затем — в выбранную ячейку. При выполнении операции чтения информация из ячейки до ее выдачи на шину данных буферизируется в выходном регистре данных. Обычно роль входного и выходного выполняет один и тот же регистр. Усилители считывания/записи (УСЗ) служат для электрического согласования сигналов на линиях данных и внутренних сигналов ИМС. Обычно число УСЗ равно числу запоминающих элементов в строке матрицы, и все они при обращении к памяти подключаются к выбранной горизонтальной линии. Каждая группа УСЗ, образующая ячейку, подключена к одному из столбцов матрицы, то есть выбор нужной ячейки в строке обеспечивается активизацией одной из вертикальных линий. На все время пока ИМС памяти не использует шину данных, информационные выходы микросхемы переводятся в третье состояние. Управление переключением в третье состояние обеспечивается сигналом ОЕ (Output Enable — разрешение выдачи выходных сигналов). Этот сигнал активизируется при выполнении операции чтения.

Для большинства перечисленных выше управляющих сигналов активным обычно считается их низкий уровень, что и показано на рис. 5.6.

Управление операциями с основной памятью осуществляется контроллером памяти. Обычно этот контроллер входит в состав центрального процессора либо реализуется в виде внешнего по отношению к памяти устройства. В последних типах ИМС памяти часть функций контроллера возлагается на микросхему памяти. Хотя работа ИМС памяти может быть организована как по синхронной, так и по асинхронной схеме, контроллер памяти — устройство синхронное, то есть срабатывающее исключительно по тактовым импульсам. По этой причине операции с памятью принято описывать с привязкой к тактам. В общем случае на каждую такую операцию требуется как минимум пять тактов, которые используются следующим образом:

1. Указание типа операции (чтение или запись) и установка адреса строки.

2. Формирование сигнала RAS.

3. Установка адреса столбца.

4. Формирование сигнала CAS.

5. Возврат сигналов RAS и CAS в неактивное состояние.

Данный перечень учитывает далеко не все необходимые действия, например регенерацию содержимого памяти в динамических ОЗУ.

Типовую процедуру доступа к памяти рассмотрим на примере чтения из ИМС с мультиплексированием адресов строк и столбцов. Сначала на входе WE устанавливается уровень, соответствующий операции чтения, а на адресные контакты ИМС подается адрес строки, сопровождаемый сигналом RAS. По заднему фронту этого сигнала адрес запоминается в регистре адреса строки микросхемы, после чего дешифрируется. После стабилизации процессов, вызванных сигналом RAS, выбранная строка подключается к УСЗ. Далее на вход ИМС подается адрес столбца, который по заднему фронту сигнала CAS заносится в регистр адреса столбца. Одновременно подготавливается выходной регистр данных, куда после стабилизации сигнала CAS загружается информация с выбранных УСЗ.

Разработчики микросхем памяти тратят значительные усилия на повышение быстродействия ИМС, которое принято характеризовать четырьмя параметрами (численные значения приводятся для типовой микросхемы динамической памяти емкостью 4 Мбит):

§ tRAS минимальное время от перепада сигнала RAS с высокого уровня к низкому до момента появления и стабилизации считанных данных на выходе ИМС. Среди приводившихся в начале главы характеристик быстродействия это соответствует времени доступа TД (tRAS = 60 нс);

§ tRС минимальное время от начала доступа к одной строке микросхемы памяти до начала доступа к следующей строке. Этот параметр также упоминался в начале главы как длительность цикла памяти TЦ (tRC = 110 нс при tRAS = 60 нс);

§ tCAS — минимальное время от перепада сигнала CAS с высокого уровня к низкому до момента появления и стабилизации считанных данных на выходе ИМС (tCAS = 15 не при tRAS = 60 нc);

§ ТPC — минимальное время от начала доступа к одному столбцу микросхемы памяти до начала доступа к следующему столбцу (tPC = 35 не при tRAS = 60 нc);

Возможности «ускорения» ядра микросхемы ЗУ весьма ограничены и связаны в основном с миниатюризацией запоминающих элементов. Наибольшие успехи достигнуты в интерфейсной части ИМС, касаются они, главным образом, операции чтения, то есть способов доставки содержимого ячейки на шину данных. Наибольшее распространение получили следующие шесть фундаментальных подходов:

§ последовательный;

§ конвейерный;

§ регистровый;

§ страничный;

§ пакетный;

§ удвоенной скорости.

Последовательный режим

При использовании последовательного режима (Flow through Mode) адрес и управляющие сигналы подаются на микросхему до поступления синхроимпульса. В момент прихода синхроимпульса вся входная информация запоминается во внутренних регистрах — по его переднему фронту, и начинается цикл чтения. Через некоторое время, но в пределах того же цикла данные появляются па внешней шине, причем момент этот определяется только моментом прихода синхронизирующего импульса и скоростью внутренних цепей микросхемы.

Конвейерный режим

Конвейерный режим (pipelined mode) - это такой метод доступа к данным, при котором можно продолжать операцию чтения по предыдущему адресу в процессе запроса по следующему.

При чтении из памяти время, требуемое для извлечения данных из ячейки, можно условно разбить на два интервала. Первый из них — непосредственно доступ к массиву запоминающих элементов и извлечение данных из ячейки. Второй — передача данных на выход (при этом происходит детектирование состояния ячейки, усиление сигнала и другие операции, необходимые для считывания информации). В отличие от последовательного режима, где следующий цикл чтения начинается только по окончании предыдущего, в конвейерном режиме процесс разбивается два этапа. Пока данные из предыдущего цикла чтения передаются на внешнюю шину, происходит запрос на следующую операцию чтения. Таким образом, два цикла чтения перекрываются во времени. Из-за усложнения схемы передачи данных на внешнюю шину время считывания увеличивается на один такт, и данные поступают на выход только в следующем такте, но такое запаздывание наблюдается лишь при первом чтении в последовательности операций считывания из памяти. Все последующие данные поступают на выход друг за другом, хотя и с запаздыванием на один такт относительно запроса на чтение. Так как циклы чтения перекрываются, микросхемы с конвейерным режимом могут использоваться при частотах тины, вдвое превышающих допустимую для ИМС с последовательным режимом чтения.

Регистровый режим

Регистровый режим (Register to Latch) используется относительно редко и отличается наличием регистра па выходе микросхемы. Адрес и управляющие сигналы выдаются на шину до поступления синхронизированного импульса. С приходом положительного фронта синхроимпульса адрес записывается во внутренний регистр микросхемы, и начинается цикл чтения. Считанные данные заносятся в промежуточный выходной регистр и хранятся там до появления отрицательного фронта (спада) синхроимпульса, а с его поступлением передаются па шину. Метод однозначно момент появления данных на выходе ИМС, причем изменяя ширину импульса можно время появления данных на шине. Данное свойство часто оказывается весьма полезным при проектировании специализированных ВМ. По быстродействию микросхемы с регистровым режимом идентичны ИМС с последовательным режимом.

Страничный режим

В основе идеи лежит тот факт, что при доступе к ячейкам со смежными адресами (согласно принципу локальности такая ситуация наиболее вероятна), причем к таким, где все ЗЭ расположены в одной строке матрицы, доступ ко второй и последующим ячейкам можно производить существенно быстрее. Действительно, если адрес строки при очередном обращении остался прежним, то все временные затраты, связанные с повторным занесением адреса строки в регистр ИМС, дешифровкой, зарядом паразитной емкости горизонтальной линии и т. п., можно исключить. Для доступа к очередной ячейке достаточно подавать на ИМС лишь адрес нового столбца, сопровождая его сигналом CAS. Отметим, что обращение к первой ячейке в последовательности производится стандартным образом — поочередным адреса строки и адреса столбца, то есть здесь время доступа уменьшить практически невозможно. Рассмотренный режим называется режимом страничного доступа или просто страничным режимом (Page Mode). Под страницей понимается строка матрицы ЗЭ. Микросхемы, где реализуется страничный режим и его модификации, принято характеризовать формулой х-у-у-у. Первое число х представляет количество тактов системной шины, необходимое для доступа к первой ячейке последовательности, а у — к каждой из последующих ячеек. Так, выражение 7-3-3-3 означает, Что для обработки первого слова необходимо 7 тактовых периодов системной шины (в течение шести из которых шина простаивает в ожидании), а для обработки последующих слов — по три периода, из которых два системная шина также простаивает.

Режим быстрого страничного доступа

Режим быстрого страничного доступа (FPM — Fast Page Mode) представляет собой модификацию стандартного страничного режима. Основное отличие заключается в способе занесения новой информации в регистр адреса столбца. Полный адрес (строки и столбца) передается только при первом обращении к строке. Активизация буферного регистра адреса столбца производится не по сигналу CAS, а по заднему фронту сигнала RAS. Сигнал RAS остается активным на протяжении всего страничного цикла и позволяет заносить в регистр адреса столбца новую информацию не по спадающему фронту CAS, а как только адрес на входе ИМС стабилизируется, то есть практически по переднему фронту сигнала CAS. В целом же потери времени сокращаются на два такта, которые ранее требовались для передачи адреса каждой строки и сигнала RAS. Реальный выигрыш, однако, наблюдается лишь при передаче блоков данных, хранящихся в одной и той же строке микросхемы. Если же программа часто обращается к разным областям памяти, переходя с одной строки ИМС на другую, преимущества метода теряются. Режим нашел широкое применение в микросхемах ОЗУ, особенно динамического типа.

Пакетный режим

Пакетный режим (Burst Mode) — режим, при котором на запрос по конкретному адресу память возвращает пакет данных, хранящихся не только по этому адресу, но и но нескольким последующим адресам.

Разрядность ячейки памяти современных ВМ обычно равна одному байту, в то время как ширина шины данных, как правило, составляет четыре байта. Следовательно, одно обращение к памяти требует последовательного доступа к четырем смежным

[1] Две первые цитаты взяты из различных толковых словарей, а третья — из постановления о таможенном тарифе.

[2] Гордой Мур — один из основателей компании Inlel, в 1965 году сделал знаменательное наблюдение, позже получившее название закона Мура. Он заметил, что плотность транзисторов па кремниевой подложке удваивается каждые 18-24 месяца, соответственно в два раза растет их производительность и в два раза падает их рыночная стоимость

[3] Термины «остроконечники» и «тупоконечники» заимствованы из книги «Путешествия Гулливера» Дж. Свифта, где упоминается религиозная война между двумя группами, представители одной из которых разбивали яйцо с острого (little) конца, а их антагонисты — с тупого (big).

[4] О — одинарный формат; Д — двойной формат.

[5] Согласно терминологии Intel. В другом варианте (DEC) естественный размер слова — 2 байта, двойного или длинного слова (longword) — 4 байта и упоминавшегося выше квадрослова (quadword) — 8 байт.

[6] В англоязычной литературе систему записи числа, начиная со старшего байта, обозначают термином «big endian», а с младшего байта — термином «little endian». Оба названия происходят от названия племен («тупоконечники» и «остроконечники»), упоминаемых в книге Джонатана Свифта «Путешествия Гулливера». Там описывается религиозная война между этими племенами, но причине разногласий в вопросе, с какого конца следует разбивать яйцо — тупого или острого.

[7] В полупроводниковых ЗУ применяются запоминающие элементы на основе: биполярных транзисторов; приборов со структурой «металл-окисел-полупроводник» (МОП-трапзисторов); приборов со структурой «металл-нитрид-окисел-полупроводник» (МНОП); приборов с зарядовой связью (ПЗС); МОП-транзисторов с изолированным затвором и др.

Дата добавления: 2019-04-03; просмотров: 354;