Становление и эволюция цифровой вычислительной техники 10 страница

Языки микропрограммирования

Для детализированного задания микропрограмм используют языки микропрограммирования. Языки микропрограммирования (ЯМП) обеспечивают описание функционирования ВМ в терминах микроопераций.

Если средства языка ориентированы на запись микропрограммы без привязки к конкретным структурам для реализации этой микропрограммы, то такой ЯМП называют языком функционального микропрограммирования, а соответствующие микропрограммы — функциональными микропрограммами [21]. Функциональная микропрограмма используется как исходная форма для описания функционирования ВМ.

В случае когда средства языка нацелены на описание микропрограмм, привязанных к конкретной реализующей их структуре, ЯМП называют языком структурно-функционального микропрограммирования.

В последующих разделах для описания функционирования ВМ будет использоваться именно язык микропрограммирования, а конкретно вариант ЯМП, предложенный в [25]. Ниже рассматриваются основные средства языка.

Описание слов, шин, регистров

Основным элементом данных, с которым оперирует микропрограмма, является слово.

Описание слова состоит из названия (идентификатора) и разрядного указателя. Идентификатором может быть произвольная последовательность букв и цифр, начинающаяся с буквы. Разрядный указатель состоит из номеров старшего и младшего разрядов слова, разделенных горизонтальной чертой (дефис). Номер старшего разряда записывается слева от черты, а номер младшего — справа. Указатель заключается в круглые скобки. Так, описание слова, представляющего 32-разрядный адрес  , записывается в виде АИСП(31-0). Разрядный указатель может опускаться, если это не вызывает недоразумений (например, если слово уже было описано раньше).

, записывается в виде АИСП(31-0). Разрядный указатель может опускаться, если это не вызывает недоразумений (например, если слово уже было описано раньше).

В структуре вычислительной машины важную роль играют шины. Шиной называется совокупность цепей, используемых для передачи слов. Одна цепь обеспечивает передачу бита информации. Описание шины, как и слова, состоит из идентификатора и разрядного указателя. Например, описание 32-разрядной шины адреса имеет вид ША(31-0).

Описание регистра также включает в себя названия регистра и разрядного указателя. Приведем примеры. Так, пусть команда имеет длину 32 бита и состоит из 8-разрядного кода операции, 4-разрядного поля способа адресации и 20-разрядного поля адреса. Тогда описание регистра команды выглядит следующим образом: РК(31-0), а описания его отдельных элементов и соответственно полей команды имеют вид: РК(31-24), РК(23-20), РК(19-0). Вместо номеров разрядов в разрядном указателе можно записывать наименование поля слова. Тогда два первых поля регистра команды могут быть представлены так: РК(КОП), РК(СА).

Описание 32-разрядного регистра РПЗ для хранения чисел с плавающей запятой, где число состоит из трех полей: s (поле знака мантиссы, бит 31), р (поле порядка, биты 30-23) и m (поле мантиссы, биты 22-0), задается в виде РПЗ(31 • 30-23 • 22-0) или РПЗ(s • р • m). Здесь точка обозначает операцию составления целого слова из его частей.

Описание памяти, слова памяти

В самом общем виде описание памяти емкостью 1000 16-разрядных слов имеет вид: ПАМ [000:999] (15-0). Здесь ПАМ — стандартное название памяти. Мы в дальнейшем будем использовать следующие идентификаторы памяти: ОП (основная память), ОЗУ (модуль оперативного запоминающего устройства), ПЗУ (модуль постоянного запоминающего устройства). В квадратных скобках записывается адресный указатель (слева от двоеточия адрес первого, а справа — адрес последнего слова памяти). Наконец, в круглые скобки заключается разрядный указатель слова (все слова памяти имеют одинаковую разрядность).

Примеры.

Описания модулей ОЗУ, содержащих по 1 Кбайт (1024 байта):

ОЗУ1[0000:1023](7-0); ОЗУ2[1024:2047](7-0).

Описания модулей ПЗУ, содержащих по 8192 32-разрядных слова:

ПЗУ1[000016:0FFF16](0-31); ПЗУ2[100016:1FFF16](0-31).

Здесь адреса слов указаны в шестнадцатеричном коде, в каждом слове старший разряд имеет номер 0, а младший — 31.

Описание слова памяти поделено на две части: идентификатор области памяти и адресный указатель слова (в квадратных скобках). Допускается символическая запись адреса, а также косвенное указание адреса слова.

Примеры описаний слов памяти: ОЗУ1[211], или 03У1[Аисп], или 03У1[(РАП)], где Аисп — символический адрес, (РАП) — косвенный адрес, значение которого содержится в регистре РАП.

Описание микроопераций

Здесь под микрооперацией понимается элементарная функциональная операция, выполняемая над словами под воздействием одного сигнала управления, который вырабатывается устройством управления ВМ. В зависимости от количества преобразуемых слов (операндов) различают одноместные, двухместные и трехместные микрооперации.

Описание микрооперации складывается из двух частей, разделяемых двоеточием

МЕТКА: МИКРООПЕРАТОР.

Метка — это обозначение сигнала управления, вызывающего выполнение микрооперации. Метка принимает два значения: 1 — микрооперация выполняется, 0 — не выполняется.

Микрооператор определяет содержимое производимого элементарного действия (микрооперации).

Например, микрооператор записи в регистр С результата сложения слов из регистров А и В имеет вид:

РгС(15-0) := РгА(15-0) + РгВ(15-0),

а полное описание микрооперации принимает форму

у15: РгС(15-0) := РгА(15-0) + РгВ(15-0).

Здесь указано, что микрооперация инициируется сигналом управления у15.

Для повышения наглядности записей желательно, чтобы метка сигнала управления несла смысловую нагрузку. Например, для микроопераций выдачи информации идентификатор метки сигнала можно начинать с буквы «В», а для приема — с буквы «П»; метку для микрооперации пересылки из регистра РА в регистр РВ можно записать в виде РАРВ.

Микрооператор по форме записи представляет собой оператор присваивания. Выражение справа от знака присваивания (:=) называется формулой микрооператора. Формула определяет вид преобразования, производимого микрооперацией, и местоположение преобразуемых операндов. Слева от знака присваивания в микрооператоре указывается приемник результата реализации формулы.

В соответствии с формулой микрооператора будем различать следующие классы микроопераций.

Микрооперация установки — присваивание слову значения константы.

Например, ПРгХ: PrX(s • m) := 0; ПРгС:С(7-0) := 3110.

Микрооперации передачи — присваивание слову значения другого слова, в том числе с инверсией передаваемого слова.

Примером простого присваивания может служить микрооперация БпУп: СК := РА. Здесь микрооператор описывает занесение в счетчик команд содержимого регистра адреса (адресного поля регистра команды), то есть реализацию перехода в командах безусловного и условного перехода, что и отражает идентификатор сигнала управления.

Другие примеры микроопераций пересылки:

PXPY: PrY(15-0) := РгХ(15-0); РевХУ: PrY(15-0):- РгХ(0-15).

Первый микрооператор описывает пересылку 16-разрядного слова из регистра РгХ в регистр PrY с сохранением расположения разрядов, а второй — с «разворотом» исходного слова.

Микрооперации передачи числа с плавающей запятой, имеющего поля знака s, порядка р и мантиссы m, а также передачи знака с инвертированием, имеют вид:

Микрооперации передачи числа с плавающей запятой, имеющего поля знака s, порядка р и мантиссы m, а также передачи знака с инвертированием, имеют вид:

Пз1Пз2: РПз2(s • р • m) := РПз1 (s • р • m); ПИЗ: PrX(s) := PrY(s).

Если регистры связаны между собой не непосредственно, а через шину, которая используется многими источниками и приемниками данных, то передача слова между ними возможна при одновременном выполнении двух микроопераций, и описание принимает вид:

ВРгВ: ША := РгВ, ПРгА: РгА := ША

или

ПРгА, ВРгВ: РгА := ША := РгВ.

Здесь метки одновременно формируемых сигналов управления перечисляются через запятую и образуют микрокоманду.

Микрооперации составления слова — обеспечивают получение целого слова большой разрядности из нескольких малоразрядных слов.

Пусть в 16-разрядный регистр А нужно передать слово, старшие разряды которого содержатся в 8-разрядном регистре В, а младшие — в 8-разрядном регистре С. Соответствующую микрооперацию можно описать так:

ПРгА: РгА(15-0) := РгВ(7-0) • РгС(7-0),

где точка (•) — знак присоединения.

Операция присоединения предназначена для присоединения значения слова, указанного справа от знака операции, к значению слова, расположенного слева от знака операции.

Микрооперации сдвига служат для изменения положения разрядов слова. Положение разрядов изменяется путем перемещения каждого разряда на несколько позиций влево или вправо.

Микрооперации сдвига слова в аккумуляторе, например, могут быть описаны в следующих формах:

§ R2AK: АК(15-0) := РС(1-0) • АК(15-2) — сдвиг на два разряда вправо с введением в два старших освобождающихся разряда содержимого двух младших разрядов регистра PC;

§ L1AK: АК(15-0) := АК(14-0) • 0 — сдвиг на один разряд влево с занесением в освобождающийся разряд нуля;

§ R2AK(15-0): РС(15-0) := АК(15) • АК(15) • АК(15-2) - арифметический сдвиг слова вправо на два разряда с загрузкой в старшие освобождающиеся разряды знака.

Для сокращения записи микрооперации сдвига используются две процедуры:

§ Rn(A) — удаление n младших правых разрядов из слова А, то есть сдвиг значения на n разрядов вправо;

§ Ln(A) — удаление n старших левых разрядов из слова А, то есть сдвиг значения на n разрядов влево.

Использование этих процедур приводит к представлению ранее рассмотренных микрооператоров в форме:

§ АК(15-0) := R2(PC(l-0) • АК);

§ АК(15-0) := Ll(AK-O);

§ PC (15-0) := R2(AK(s) • AK(s) • АК).

Микрооперация счета — обеспечивает изменение значения слова на единицу: +1СК: СК := СК + 1.

Микрооперация сложения — служит для присваивания слову суммы слагаемых: СлАд: РАП :=ИР + РА.

Логические микрооперации — присваивают слову значение, полученное поразрядным применением функций И (  ), ИЛИ (

), ИЛИ (  ), исключающее ИЛИ (

), исключающее ИЛИ (  ) к парам соответствующих разрядов операндов:

) к парам соответствующих разрядов операндов:

И: АК := РгХ л PrY; М2: АК := РгХ 0 PrY.

Микрооперация двоичного декодирования — состоит в преобразовании n-разрядного двоичного позиционного кода А в 2n-разрядный унитарный код В. В унитарном коде только один разряд принимает единичное значение, а все остальные равны нулю. Номер разряда К, который принимает значение 1, определяется значением кода A = an-1, an-2, ...,а0:

Принято следующее условное обозначение: В := decod (А).

Комментарии к микрооперациям

Микрооперации могут снабжаться произвольными комментариями. Комментарии записываются справа от микрооперации и заключаются в угловые скобки. Например,

+1СК := СК := СК + 1 <Увеличение содержимого СК на единицу>.

Совместимость микроопераций

Совместимостью называется свойство совокупности микроопераций, гарантирующее возможность их параллельного выполнения [21]. Различают функциональную и структурную совместимости. Пусть S1, S2, S3, S4 — подмножества слов из множества S. Тогда микрооперации S1:= φ1(S2) и S3:= φ2(S4) называются функционально совместимыми, если S1 ∩ S2 = Ш, то есть если микрооперации присваивают значения разным словам. В функциональных микропрограммах, описывающих алгоритмы выполнения операций без учета структуры вычислительной машины, одновременно могут выполняться только функционально совместимые микрооперации.

Структура ВМ может внести дополнительные ограничения на возможность параллельного выполнения микроопераций. Микрооперации называются структурно несовместимыми, если из-за ограничений, обусловленных структурой ВМ, они не могут выполняться параллельно. Обычно структурная несовместимость связана с использованием микрооперациями одного и того же оборудования.

Цикл команды

Программа в фон-неймановской ЭВМ реализуется центральным процессором (ЦП) посредством последовательного исполнения образующих эту программу команд. Действия, требуемые для выборки (извлечения из основной памяти) и выполнения команды, называют циклом команды. В общем случае цикл команды включает в себя несколько составляющих (этапов):

§ выборку команды;

§ формирование адреса следующей команды;

§ декодирование команды;

§ вычисление адресов операндов;

§ выборку операндов;

§ исполнение операции;

§ запись результата.

Перечисленные этапы выполнения команды в дальнейшем будем называть стандартным циклом команды. Отметим, что не все из этапов присутствуют при выполнении любой команды (зависит от типа команды), тем не менее этапы выборки, декодирования, формирования адреса следующей команды и исполнения имеют место всегда.

В определенных ситуациях возможны еще два этапа:

§ косвенная адресация;

§ реакция на прерывание.

Стандартный цикл команды

Кратко охарактеризуем каждый из вышеперечисленных этапов стандартного цикла команды. При изучении данного материала следует учитывать, что приводимое описание имеет целью лишь дать представление о сущности каждого из этапов. В то же время распределение функций по разным этапам цикла команды и последовательность выполнения некоторых из них в реальных ВМ могут отличаться от излагаемых.

Этап выборки команды

Цикл любой команды начинается с того, что центральный процессор извлекает команду из памяти, используя адрес, хранящийся в счетчике команд (СК). Двоичный код команды помещается в регистр команды (РК) и с этого момента становится «видимым» для процессора. Без учета промежуточных пересылок и сигналов управления это можно описать следующим образом: РК := 0П[(СК)].

Приведенная запись охватывает весь этап выборки, если длина команды совпадает с разрядностью ячейки памяти. В то же время система команд многих ВМ предполагает несколько форматов команд, причем в разных форматах команда может занимать 1, 2 или более ячеек, а этап выборки команды можно считать завершенным лишь после того, как в РК будет помещен полный код команды. Информация о фактической длине команды содержится в полях кода операции и способа адресации. Обычно эти поля располагают в первом слове кода команды, и для выяснения необходимости продолжения процесса выборки необходимо предварительное декодирование их содержимого. Такое декодирование может быть произведено после того, как первое слово кода команды окажется в РК. В случае многословного формата команды процесс выборки продолжается вплоть до занесения в РК всех слов команды. Например, для 16-разрядной команды, занимающей две 8-разрядные ячейки памяти, выборку можно описать так:

ПСтРК: РК(15-8) :=0П[(СК)];

+1СК: СК :=СК + 1;

ПМлРК: РК(7-0) :=0П[(СК)].

Этап формирования адреса следующей команды

Для фон-неймановских машин характерно размещение соседних команд программы в смежных ячейках памяти. Если извлеченная команда не нарушает естественного порядка выполнения программы, для вычисления адреса следующей выполняемой команды достаточно увеличить содержимое счетчика команд на длину текущей команды, представленную количеством занимаемых кодом команды ячеек памяти. Для однословной команды это описывается микрооперацией: +1СК: СК := СК + 1.

Длина команды, а также то, способна ли она изменить естественный порядок выполнения команд программы, выясняются в ходе ранее упоминавшегося предварительного декодирования. Если извлеченная команда способна изменить последовательность выполнения программы (команда условного или безусловного перехода, вызова процедуры и т. п.), процесс формирования адреса следующей команды переносится на этап исполнения операции. В силу сказанного, в ряде ВМ рассматриваемый этап цикла команды следует не за выборкой команды, а находится в конце цикла.

Этап декодирования команды

После выборки команды она должна быть декодирована, для чего ЦП расшифровывает находящийся в РК код команды. В результате декодирования выясняются следующие моменты:

§ находится ли в РК полный код команды или требуется дозагрузка остальных слов команды;

§ какие последующие действия нужны для выполнения данной команды;

§ если команда использует операнды, то откуда они должны быть взяты (номер регистра или адрес ячейки основной памяти);

§ если команда формирует результат, то куда этот результат должен быть направлен.

Ответы па два первых вопроса дает расшифровка кода операции, результатом которой может быть унитарный код, где каждый разряд соответствует одной из команд, что можно описать в виде УнитК := decod(Koп). На практике вместо унитарного кода могут встретиться самые разнообразные формы представления результатов декодирования, например адрес ячейки специальной управляющей памяти, где хранится первая микрокоманда микропрограммы для реализации указанной в команде операции.

Полное выяснение всех аспектов команды, помимо расшифровки кода операции, требует также анализа адресной части команды, включая поле способа адресации.

По результатам декодирования производится подготовка электронных схем ВМ к выполнению предписанных командой действий.

Этап вычисления адресов операндов

Этап имеет место, если в процессе декодирования команды выясняется, что команда использует операнды. Если операнды размещаются в основной памяти, осуществляется вычисление их исполнительных адресов, с учетом указанного в команде способа адресации. Так, в случае индексной адресации для получения исполнительного адреса производится суммирование содержимого адресной части команды и содержимого индексного регистра.

Этап выборки операндов

Вычисленные на предыдущем этапе исполнительные адреса используются для считывания операндов из памяти и занесения в определенные регистры процессора. Например, в случае арифметической команды операнд после извлечения из памяти может быть загружен во входной регистр АЛУ. Однако чаще операнды предварительно заносятся в специальные вспомогательные регистры процессора, а их пересылка на вход АЛУ происходит на этапе исполнения операции.

Этап исполнения операции

На этом этапе реализуется указанная в команде операция. В силу различия сущности каждой из команд ВМ, содержание этого этапа также сугубо индивидуально. Этапы исполнения некоторых команд будут рассмотрены ниже на примере выполнения учебной программы для приведенной на рис. 3.1 гипотетической вычислительной машины.

Этап записи результата

Этап записи результата присутствует в цикле тех команд, которые предполагают занесение результата в регистр или ячейку основной памяти. Фактически его можно считать частью этапа исполнения, особенно для тех команд, которые помещают результат сразу в несколько мест.

Описание стандартных циклов команды для гипотетической машины

Для анализа содержания стандартных циклов команды обратимся к гипотетической ВМ (см. рис. 3.1), для которой составим программу сложения двух чисел и вывода суммы на устройство вывода, если эта сумма не равна 0.

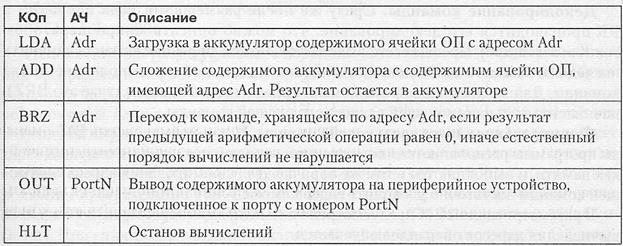

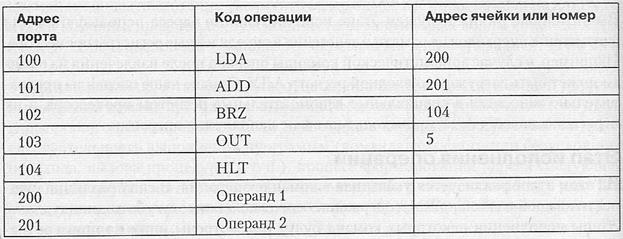

Список необходимых команд приведен в табл. 3.1, а сама программа — в табл. 3.2. Предполагается, что команды программы будут размещаться в основной памяти, начиная с адреса 100, а операнды — с адреса 200. Для вывода результата назначим порт с номером 5.

Таблица 3.2. Программа к рассматриваемому примеру

Таблица 3.2. Программа к рассматриваемому примеру

Перед запуском программы необходимо занести в СК адрес ячейки основной памяти, содержащей первую выполняемую команду программы, то есть 100.

Поскольку выборка и декодирование, а также формирование адреса следующей команды для всех команд выполняются по идентичной схеме, опишем их однократно, детализируя в дальнейшем лишь остальные этапы основного цикла команды. Кроме того, напомним, что все сигналы управления и управляющие коды формируются микропрограммным автоматом, поэтому в дальнейшем ссылки на МПА будут опущены.

Выборка команды. Сначала остановимся на содержании этапа выборки, идентичного для всех команд программы. На этом этапе происходит извлечение двоичного кода команды из ячейки основной памяти и его занесение в регистр команды:

СКРАП: РАП := СК, ЧтЗУ: РДП := 0П[(СК)];

РДПКОп, РДПРА: РК := РДП <РК0п := РДП(КОп), РА := РДП(АЧ)>.

В первом такте вырабатывается сигнал управления СКРАП, инициирующий пересылку содержимого счетчика команд в регистр адреса памяти. По сигналу ЧтЗУ содержимое ячейки, выбранной дешифратором адреса памяти (код команды), переписывается в регистр данных памяти. В следующем такте формируются сигналы РДПКОп и РДПРА, по которым содержимое РДП передается в РК, при этом поле РКОп заполняется кодом операции, а поле РА — адресной частью команды.

Декодирование команды. Сразу же после размещения кода операции в РК производится его декодирование, что можно описать микрооператором УнитК := decod(Koп). Прежде всего выясняется, может ли данная команда изменить последовательность вычислений, что влияет на дальнейшее выполнение цикла команды. Для всех команд, кроме команд управления (в нашем случае это BRZ), начинается этап формирования адреса следующей команды.

Формирование адреса следующей команды. В фон-неймановских ВМ команды программы располагаются в естественном порядке следования, в соседних ячейках памяти, и выполняются в том же порядке. Для формирования адреса следующей команды достаточно увеличить содержимое СК на единицу: +1СК: СК := СК + 1.

В рассматриваемой ВМ предусмотрена только прямая адресация, поэтому этап вычисления адресов операндов опускается.

В анализируемой программе этап выборки операндов предполагается только в командах загрузки аккумулятора и сложения. Для простоты изложения будем расценивать выборку операндов как часть этапа исполнения соответствующих операций. В свою очередь, этапы исполнения специфичны для каждой команды и рассматриваются применительно к каждой команде нашей программы.

Исполнение операции загрузки аккумулятора. Команда LDА 200 обеспечивает занесение в аккумулятор содержимого ячейки ОП с адресом 200, то есть первого операнда, и реализуется следующим образом:

§ МПА вырабатывает сигнал РАРАП, передающий содержимое РА (адресную часть команды) в РАП;

§ по сигналу ЧтЗУ содержимое ячейки 200 заносится в РДП;

§ по сигналу РДПАкк первый операнд из РДП помещается в аккумулятор.

На языке микроопераций это выглядит так:

РАРАП: РАП := РК(РА); ЧтЗУ:РДП := 0П[200];

РДПАкк: Акк := РДП.

Исполнение операции сложения. Команда ADD 201 обеспечивает суммирование текущего содержимого аккумулятора с содержимым ячейки 201 (вторым операндом). Результат сложения остается в аккумуляторе. Одновременно с этим в АЛУ формируются признаки результата:

§ МПА вырабатывает сигнал РАРАП, и содержимое РА поступает в РАП;

§ по сигналу ЧтЗУ содержимое ячейки 201 заносится в РДП;

§ сигнал управления РДПРХ вызывает пересылку операнда 2 из РДП в регистр РХ АЛУ; одновременно с этим МПА вырабатывает сигнал AkkPY, по которому в PY переписывается содержимое аккумулятора, то есть хранящийся там первый операнд; операционный блок выполняет над данными, расположенными в РХ и PY, операцию, заданную в коде операции команды (в нашем случае — сложение);

§ по сигналу ОПБАкк информация с выхода OПБ загружается в аккумулятор.

Сказанное может быть описано в виде:

РАРАП: РАП := РК(РА), ЧтЗУ:РДП := 0П[201];

РДПРХ: РХ := РДП, AkkPY: PY:= Акк, ОПБ := РХ+ PY;0ПБАкк1: Акк:=0ПБ.

Исполнение операции условного перехода. Для изменения порядка выполнения программы используются команды безусловного (БП) и условного (УП) переходов, в нашем случае — команда BRZ 104. Адрес перехода хранится в адресном поле команды. Команда анализирует хранящийся в РПрз признак (флаг) нулевого результата, выработанный в АЛУ на предыдущем этапе вычислений, и формирует адрес следующей команды в зависимости от состояния этого признака. При нулевом значении флага (условие перехода не выполнено) естественный порядок выполнения программы не нарушается, и адрес следующей команды формируется обычным образом, путем увеличения содержимого СК на единицу (+1СК: СК := СК + 1). При единичном значении флага (условие перехода выполнено) в СК заносится содержимое РА. Напомним, что в РА находится адресная часть извлеченной из ОП команды перехода, то есть адрес точки перехода. Сказанное можно записать в виде БПУП: СК := РК(РА). Поскольку для команд перехода формирование адреса следующей команды по сути является и исполнением их операций, описанные микрооперации для них обычно относят к этапу исполнения.

Исполнение операции вывода. Команда OUT 5 обеспечивает вывод содержимого аккумулятора на периферийное устройство (ПУ), подключенное к порту вывода с номером 5. МПА вырабатывает управляющий сигнал РАДВВ, по которому адресная часть команды — номер порта вывода — из РА поступает на вход дешифратора номера порта ввода/вывода. В следующем такте по сигналу Выв содержимое аккумулятора через выбранный дешифратором порт вывода передается на подключенное к этому порту ПУ:

РАДВВ: ДВВ := РК(РА);

Выв: Порт вывода 5 := Акк.

Исполнение операции останова. Команда HLT приводит к завершению вычислений. При этом вырабатывается сигнал Ост, нужный для того, чтобы известить операционную систему о завершений текущей программы.

Машинный цикл с косвенной адресацией

Многие команды предполагают чтение операндов из памяти или запись в память. В простейшем случае в адресном поле таких команд явно указывается исполнительный адрес соответствующей ячейки ОП. Однако часто используется и другой способ указания адреса, когда адрес операнда хранится в какой-то ячейке памяти, а в команде указывается адрес ячейки, содержащей адрес операнда. Как уже отмечалось ранее, подобный прием называется косвенной адресацией. Чтобы прочитать или записать операнд, сначала нужно извлечь из памяти его адрес и только после этого произвести нужное действие (чтение или запись операнда), иными словами, требуется выполнить два обращения к памяти. Это, естественно, отражается и на цикле команды, в котором появляется косвенная адресация. Этап косвенной адресации можно отнести к этапу вычисления адресов операндов, поскольку его сущность сводится к определению исполнительного адреса операнда.

Применительно к вычислительной машине, приведенной на рис. 3.1, при косвенной адресации имеют место следующие микрооперации:

РАРАП: РАП := РК(РА), ЧтЗУ: РДП := 0П[(РА)]; РДПРА: РК(РА) := РДП.

Иными словами, содержимое адресного поля команды в регистре команд используется для обращения к ячейке ОП, в которой хранится адрес операнда, после чего извлеченный из памяти исполнительный адрес операнда помещается в адресное поле регистра команды на место косвенного адреса. Дальнейшее выполнение команды протекает стандартным образом.

Машинный цикл с прерыванием

Практически во всех ВМ предусмотрены средства, благодаря которым модули ввода/вывода (и не только они) могут прервать выполнение текущей программы для внеочередного выполнения другой программы, с последующим возвратом к прерванной.

Первоначально прерывания были введены для повышения эффективности вычислений при работе с медленными ПУ. Положим, что процессор пересылает данные на принтер, используя стандартный цикл команды. После каждой операции записи ЦП будет вынужден сделать паузу, в ожидании подтверждения от принтера об обработке символа. Длительность этой паузы может составлять сотни и тысячи циклов команды. Ясно, что такое использование ЦП очень неэффективно. В случае прерываний, пока протекает операция ввода/вывода, ЦП способен выполнять другие команды.

В упрощенном виде процедуру прерывания можно описать следующим образом. Объект, требующий внеочередного обслуживания, выставляет на соответствующем входе ЦП сигнал запроса прерывания. Перед переходом к очередному циклу команды процессор проверяет этот вход на наличие запроса. Обнаружив запрос, ЦП запоминает информацию, необходимую для продолжения нормальной работы после возврата из прерывания, и переходит к выполнению программы обработки прерывания (обработчика прерывания). По завершении обработки прерывания ЦП восстанавливает состояние прерванного процесса, используя запомненную информацию, и продолжает вычисления. Описанный процесс иллюстрирует рис. 3.5.

Дата добавления: 2019-04-03; просмотров: 377;