Расширение внутренних ресурсов ВЕ48

Если размещенных на кристалле МК ресурсов оказывается недостаточно для реализации конкретной прикладной системы, они могут быть расширены внешними по отношению к МК средствами. Такое расширение легко выполняется за счет ввода в действие еще не использованных возможностей базовой архитектуры МК. Так, прямо адресуемая программная память может быть доведена до 4К байт, резервом дополнительной памяти данных служит поддерживаемое архитектурой пространство внешнего ОЗУ. На 16 линий может быть увеличена система ВВ. Кроме того, применяя различные способы расширения физических адресов, можно довести объемы внешних физических пространств до требуемого размера сверх норм, предусмотренных базовой архитектурой, без каких-либо ограничений сверху. Эффективная реализация специальных функций возможна с помощью стандартных периферийных БИС семейства ВМ80/ВМ85А.

Организация МК ВЕ48 поддерживает два способа прямого расширения своих вычислительных ресурсов. Первый способ—использование интерфейса расширения памяти, совместимого с системной магистралью ВМ85А. Второй способ предполагает активизацию интерфейса расширения ВВ.

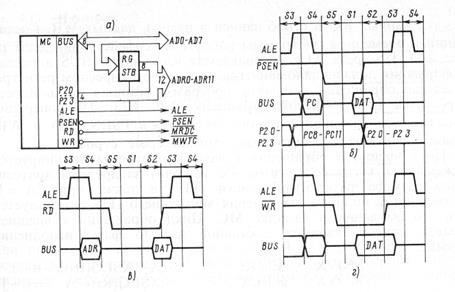

В состав интерфейса расширения памяти входят двунаправленная 8-разрядная мультиплексированная шина адреса/данных BUS, шина старшей части адреса Р20—Р23, строб разрешения фиксации адреса ALE, строб чтения памяти программ  , строб чтения памяти данных

, строб чтения памяти данных  и строб записи в память данных

и строб записи в память данных  . Состав линий и временные диаграммы работы интерфейса приведены на рис. 4.14. По срезу ALE передаваемая через шину BUS адресная информация должна запоминаться во внешнем адресном регистре. В случае обращения к памяти программ старшая часть адреса передается через 4-разрядную шину Р20—Р23. Тип операции определяется активацией одного из стробов

. Состав линий и временные диаграммы работы интерфейса приведены на рис. 4.14. По срезу ALE передаваемая через шину BUS адресная информация должна запоминаться во внешнем адресном регистре. В случае обращения к памяти программ старшая часть адреса передается через 4-разрядную шину Р20—Р23. Тип операции определяется активацией одного из стробов  ,

,  и

и  . Данные считаются действительными на срезе стробов.

. Данные считаются действительными на срезе стробов.

Рис. 4.14. Интерфейс расширения памяти:

а—состав; б—чтение памяти программ; в—чтение памяти данных; г—запись в память данных

Цикл внешнего обращения к памяти программ инициируется каждый раз, когда содержимое PC выходит за пределы допустимого размера резидентной части ПЗУ, а также при ЕА = 1. Возможность полного отключения внутреннего ПЗУ используется при его эмуляции и отладке МС. Цикл обращения к внешней памяти данных является составной частью фазы исполнения команд:

MOVX A, @Ri ;AXSEG(Ri), i = 0—1

MOVX @Ri, A ;XSEG(Ri)A, i = 0—1

В операции внешнего расширения задействованы порты BUS и Р2. Из временных диаграмм на рис. 4.14 видно, что состояние порта BUS при этом разрушается, а его выход после выполнения операции переходит в высокоимпедансное состояние. Это обстоятельство может быть учтено при организации двунаправленного обмена через шину BUS. Действительно, по команде

OUTL BUS, A ;BUSA

шина BUS активизируется. Для перевода ее в z-состояние применяется команда типа MOVX, освобождающая шину для ввода информации. В отличие от порта BUS порт Р2 также используется в операциях внешнего обращения к памяти программ, восстанавливая свое состояние после каждого цикла обращения.

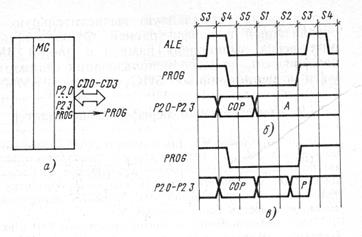

Интерфейс расширения ВВ содержит 4-разрядную информационную шину команд/данных Р20—Р23 и линию управления PROG. Интерфейс активизируется по командам

MOVD А, Рр ;А0—3Рр, А4—70, p = 4—7

MOVD Рр, А ;РрА0—3, р = 4—7

ORLD Pp, A ;РрРр OR A0—3, р = 4—7

ANLD Pp, A ;PpPp AND A0—3, р = 4—7

Протокол интерфейса состоит в передаче через 4-разрядный канал Р20—Р23 кода операции и данных обмена, которые однозначно связаны с четырьмя вышеуказанными командами. Состав линии, временные диаграммы протокола и способ кодирования информации приведены на рис. 4.15 и в табл. 4.7. Управление обменом осуществляется с помощью сигнала PROG, срез которого синхронизирует передачу кода операции обмена, а фронт—данных обмена.

Рис. 4.15. Интерфейс расширения ВВ:

а—состав; б—вывод данных; в—ввод данных

Таблица 4.7

| Код СОР | Описание | Код СОР | Описание |

| 3 2 1 0 | 3 2 1 0 | ||

| 0 0 Р Р 0 1 Р Р | MOVD A, Pp MOVD Pp, A | 1 0 Р Р 1 1 Р Р | ORLD Рр, А ANLD Рр, А |

В операциях участвует младшая тетрада аккумулятора. При чтении портов старшая тетрада А сбрасывается. Система команд предусматривает выполнение периферийной операции логического AND и OR содержимого порта с состоянием младшей тетрады аккумулятора. Пользователь может по своему усмотрению интерпретировать эти команды и команды пересылки, внося новый смысл в их содержание.

В отличие от цикла обращения к внешней памяти программ состояние младшей части порта Р2 после операций обмена с внешней системой ВВ не восстанавливается. После чтения Р20—Р23 будут находиться в режиме ввода, после записи Р20—Р23 содержат данные, переданные в канал.

Дальнейшее расширение 4-разрядного пространства ВВ, как и областей памяти или данных, легко выполняется с помощью переключения банков. В этом случае ряд резидентных линий, например Р24—Р27, выполняют функции дополнительной адресной шины, указывающей на один из банков управляющей памяти, памяти данных или портов ВВ. Возможны различные отображения и наложения внешних областей пространств друг на друга, формирующие прикладную вычислительную среду с требуемой организацией и конфигурацией. Функциональная совместимость интерфейса расширения памяти с шиной ВМ85А обеспечивает возможность прямого использования стандартных устройств памяти и периферийных БИС семейства ВМ80/ВМ85А.

Дата добавления: 2019-02-07; просмотров: 447;