Универсальный периферийный адаптер

Однокристальные МК представляют собой специальный класс функционально законченных МС, все ресурсы которых расположены на одном кристалле. Эти автономные устройства образуют стандартные системные ядра для построения компактных и недорогих средств цифровой обработки. Важнейшей областью применения однокристальных МК являются периферийные контроллеры ВВ, входящие в состав более мощных МС.

После промышленного освоения 8-разрядных МП и их улучшенных вариантов быстрыми темпами стала развиваться техника ВВ. Появилось множество однокристальных программируемых адаптеров и контроллеров ПУ, освобождающих главный процессор МС от ряда функций управления ВВ. Было достигнуто значительное повышение производительности МС и снижение сложности ее ПО.

Интеллектуальный интерфейс ВВ не только упрощает задачу программирования (так как многие функции нижнего уровня он выполняет своими собственными средствами), но и обеспечивает дополнительную гибкость системы. Такой интерфейс содержит программно-доступные регистры, управляющие его работой в различных режимах. Несмотря на программируемость все эти устройства спроектированы для выполнения узкоспециализированных задач ВВ. Архитектура однокристальных МК является идеальной средой проектирования действительно универсальных интеллектуальных интерфейсов различного типа.

К недостаткам МК относится отсутствие встроенного системного интерфейса, с помощью которого главный ЦП имел бы возможность взаимодействовать с МК. Системный интерфейс (СА) может быть реализован внешними средствами. Его размещение непосредственно на кристалле МК приводит к новому типу программируемых периферийных микроконтроллеров, подчиненных главному ЦП, к системной магистрали которого они подключены.

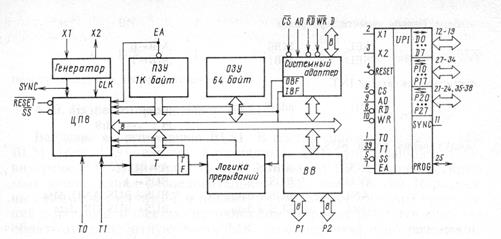

Типичным представителем приборов данного класса является универсальный периферийный адаптер (УПА, UPI—Universal Peripheral Interface) 8041 фирмы Intel (рис. 4.16). Прибор заключен в стандартный 40-выводный корпус (рис. 4.17), для его работы требуется один источник питания +5 В.

| Рис. 4.16. Структурная схема универсального периферийного адаптера | Рис. 4.17. Условное графическое обозначение универсального периферийного адаптера |

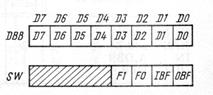

Устройство имеет организацию типа ВЕ48, которая расширена встроенным СА, удовлетворяющим требованиям шины Microbus на периферийные БИС второго поколения. В состав адаптера входят двунаправленный 8-разрядный буферный регистр слова данных DBB и 4-разрядный регистр слова состояния SW (рис. 4.18). По отношению к центральному процессору УПА является обычным ПУ, связь с которым осуществляется через названные регистры. Операции доступа к ним со стороны шипы Microbus приведены в табл. 4.8.

Рис. 4.18. Пространство связи с универсальным периферийным адаптером

Таблица 4.8

| А0 |

|

|

| Операция |

| DDB, OBF0 | ||||

| DSW | ||||

| DBBD, F10, IBF1 BF«-1 | ||||

| DBBD, F11, IBF1 ОГ7 1 | ||||

| X X | X X | X X | Нет операции To же | |

| X | X | X | То же |

Ввод-вывод данных сопровождается автоматическим сбросом/установкой флажков готовности OBF/IBF, обеспечивающих операцию условного обмена. Установка IBF в 1 вызывает генерацию запроса на прерывание со стартовым адресом 3 (внешнее прерывание INT для ВЕ48). Ввод информации осуществляется как при А0 = 0, так и при А0 = 1, при этом состояние А0 фиксируется флажком F1. Ввод информации по адресу А0 = 0 резервируется для передачи непосредственно данных, по адресу А0 = 1—для передачи управляющих слов. Флажок F0 доступен только для чтения в SW и носит общий характер.

Для УПА буфер DBB представляет собой порт, заменяющий BUS в ВЕ48. Все флажки SW при этом программно-доступны. Если флажки F0, F1 представляют собой одноименные флажки пользователя ВЕ48, то IBF и OBF—два новых флажка, которые отсутствуют в ВЕ48.

Набор команд УПА совместим с системой ВЕ48 на уровне объектного кода. Однако в наборе отсутствуют команды:

обращения к внешней памяти данных

MOVX A, @Ri ;AXSEG(Ri), i = 0—1

MOVX @Ri, A ;XSEG(Ri)A, i = 0—1

выбора банков памяти программ

SEL MB0 ;MB0

SEL MB1 ;MB1

тестирования входа

JNI addr8 ;Если  = 1, то РС0—7addr8

= 1, то РС0—7addr8

обслуживания порта BUS

INS A, BUS ;ABUS

OUTL BUS, A ;BUSA

ANL BUS, #data ;BUSBUS AND data

ORL BUS, #data ;BUSBUS OR data

и команда

ENT0 CLK ;Разрешение выдачи CLK на Т0

что связано с соответствующими изменениями в организации УПА. Введены также четыре новые команды, представленные в табл. 4.9.

Таблица 4.9

| Мнемоника | Число байтов | Число циклов | Код | CY | Описание |

| JNIBF addr8 JOBF addr8 IN A, DBB OUT DBB, A | D6 | ― ― ― — | Если IBF = 0, то РС0—7addr8 Если OBF = 1, то PC0—7addr8 ADBB, IBF0 DBBA, OBF1 |

Набор команд условного перехода внутри текущей страницы расширен двумя новыми:

JNIBF addr8 ;Если IBF = 0, то PC0—7addr8

JOBF addr8 ;Если OBF = 1, то PC0—7addr8

которые позволяют организовать программное тестирование флажков IBF и OBF состояния буфера шины данных DBB. Такая проверка необходима при построении процедур программно-управляемого ВВ данных. Две другие команды

IN A, DBB ;ADBB, IBF0

OUT DBB, A ;DBBA, OBF1

связывают буфер ДВВ с аккумулятором, обеспечивая программный доступ к данным, переданным через шину данных. Команды обеспечивают согласованное управление флажками IBF и OBF, указывающими на состояние буфера DBB. При чтении буфера флажок IBF устанавливается в 0, а при записи в буфер флажок OBF устанавливается в 1. Так как запрос на внешнее прерывание  микроконтроллера ВЕ48 в УПА используется для принятия запросов по флагу IBF, то команды

микроконтроллера ВЕ48 в УПА используется для принятия запросов по флагу IBF, то команды

EN I ;Разрешение прерываний по

DIS I ;Запрет прерываний по

получают другую интерпретацию.

Дата добавления: 2019-02-07; просмотров: 522;