Физический интерфейс ВЕ48

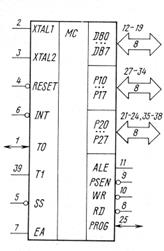

Условное графическое обозначение МК ВЕ48 приведено на рис. 4.10. Приборы размещаются в стандартных 40-выводных корпусах типа 2123.40 с двухрядным расположением выводов.

Рис. 4.10. Условное графическое обозначение ВЕ48

Приведем состав физического интерфейса ВЕ48:

VSS

VDD

VCC

PROG

P10—P17

P20—P27

DB0—DB7

ALE

EA

EA

XTAL1,

XTAL2

T0

T1

XTAL1,

XTAL2

T0

T1

| 27—34 21—24, 35—38 12—19 2, | Общий

Напряжение питания +5 В или +21 В в режиме программного УСППЗУ

Напряжение питания +5 В

Выходной строб для расширителя ВВ или программирующий импульс +18 В в режиме программирования УСППЗУ

Псевдодвунапрвленный 8-раазрядный порт ВВ

Псевдодвунаправленный 8-разрядный порт ВВ, младшая тетрада которого Р20—Р23 используется для вывода старшей части адреса при обращении к внешней памяти программ и как канал связи с расширителем ВВ

Двунаправленный 8-разрядный канал ВВ данных либо синхронно со стробами  , ,  , либо асинхронно. При обращении внешней памяти программ используется для выдачи младшего байта адреса синхронно с ALE и приема очередного байта программной последовательности синхронно с , либо асинхронно. При обращении внешней памяти программ используется для выдачи младшего байта адреса синхронно с ALE и приема очередного байта программной последовательности синхронно с  . При обращении к внешней памяти данных служит для выдачи младшего байта адреса памяти синхронно с ALE и передачи данных в соответствии со стробами . При обращении к внешней памяти данных служит для выдачи младшего байта адреса памяти синхронно с ALE и передачи данных в соответствии со стробами  , ,  Строб приема адреса. Генерируется в начале каждого машинного цикла и может быть применен для синхронизации внешних цепей

Строб чтения данных. Генерируется в циклах чтения шины BUS. Используется как строб чтения внешней памяти данных

Строб выдачи данных. Генерируется в циклах вывода информации через шину BUS. Применяется как строб записи данных во внешнюю память

Вход начальной установки. Используется в режимах программирования УСППЗУ Строб чтения внешней памяти программ

Разрешение доступа к внешней памяти. Применяется для запрета внутреннего ПЗУ в режимах эмуляции и отладки. Подача на вход напряжения +18 В переводит прибор в режим программирования УСППЗУ

Пошаговый режим. Используется совместно с ALE для организации пошагового исполнения команд

Вход и выход для подключения кварцевого резонатора, а также вход для внешнего ГТИ

Тестовый вход или выход для выдачи импульсов CLK, формируемых внутри МК

Тестовый вход, а также вход для приема импульсов счета

Тестовый вход, а также вход для приема внешнего запроса на прерывание с низким уровнем активности

Строб приема адреса. Генерируется в начале каждого машинного цикла и может быть применен для синхронизации внешних цепей

Строб чтения данных. Генерируется в циклах чтения шины BUS. Используется как строб чтения внешней памяти данных

Строб выдачи данных. Генерируется в циклах вывода информации через шину BUS. Применяется как строб записи данных во внешнюю память

Вход начальной установки. Используется в режимах программирования УСППЗУ Строб чтения внешней памяти программ

Разрешение доступа к внешней памяти. Применяется для запрета внутреннего ПЗУ в режимах эмуляции и отладки. Подача на вход напряжения +18 В переводит прибор в режим программирования УСППЗУ

Пошаговый режим. Используется совместно с ALE для организации пошагового исполнения команд

Вход и выход для подключения кварцевого резонатора, а также вход для внешнего ГТИ

Тестовый вход или выход для выдачи импульсов CLK, формируемых внутри МК

Тестовый вход, а также вход для приема импульсов счета

Тестовый вход, а также вход для приема внешнего запроса на прерывание с низким уровнем активности

|

Встроенный в ВЕ48 генератор работает в диапазоне частот 1—11 МГц. Вывод XTAL1 служит входом, a XTAL2—выходом каскада усиления. Внешний кварцевый резонатор или RC-цепочка подключаются к XTAL1, XTAL2, обеспечивая необходимую для генерации внешнюю связь и сдвиг фаз.

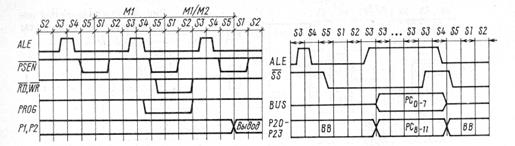

В результате деления частоты OSC на 3 получается основная тактовая частота CLK, определяющая работу внутренних узлов МК. Синхросигнал машинных циклов ALE формируется путем дополнительного деления CLK на 5 и постоянно присутствует на одноименном выходе МК.

Каждый машинный цикл состоит из пяти тактов CLK, именуемых S1—S5. Для выполнения команды требуется один или два машинных цикла. Прием команды всегда осуществляется в первом такте S1 первого машинного цикла M1. Во втором такте S2 принятая команда декодируется, a PC получает приращение. Такты S3—S5 отводятся для внутреннего исполнения команды. В случае двухбайтовой или одноцикловой команды одновременно с этим память программ предъявляет новое значение PC. Новый элемент программной последовательности считывается в такте S1 следующего машинного цикла. Для одноцикловой команды S1—начало нового командного цикла.

Во втором машинном цикле двухбайтовая команда считывает второй байт программной последовательности, представляющий либо непосредственные данные, либо младшую часть адреса. Функциональное распределение тактов S1—S5 аналогично М1.

Однобайтовая двухцикловая команда с обращением к управляющей памяти во втором машинном цикле выполняется по аналогии с двухбайтовой. Все другие двухцикловые команды в такте S2 второго машинного цикла считывают данные либо из внешнего ОЗУ, либо из портов. В этом случае необходимая адресная информация передается в тактах S3—S5 первого машинного цикла. Обобщенная временная диаграмма тактирования командных циклов представлена на рис. 4.11.

| Рис. 4.11. Временные диаграммы командного цикла ВЕ48 | Рис. 4.12. Временные диаграммы пошагового режима работы |

Входные сигналы всех портов совместимы с ТТЛ, а на выходах может быть подключена стандартная ТТЛ-нагрузка. Вывод данных через порты P1, P2 осуществляется в такте S5 второго машинного цикла. При работе с портом BUS операции ВВ сопровождаются генерацией импульсов  ,

,  , которые могут быть использованы для организации синхронного ВВ. Данные действительны на срезе стробов.

, которые могут быть использованы для организации синхронного ВВ. Данные действительны на срезе стробов.

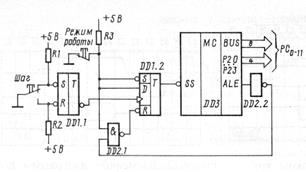

В МК ВЕ48 предусмотрена возможность организации пошагового режима работы, что очень важно для отладки и проверки содержимого памяти программ. В этом случае программа исполняется по шагам, каждый шаг—это один машинный цикл. Управление началом следующего шага осуществляется с помощью сигнала на входе  , как показано на рис. 4.12. При работе в пошаговом режиме содержимое порта BUS теряется, но может быть сохранено дополнительными внешними средствами, буферизирующими его состояние по срезу

, как показано на рис. 4.12. При работе в пошаговом режиме содержимое порта BUS теряется, но может быть сохранено дополнительными внешними средствами, буферизирующими его состояние по срезу

ALE.

Появление напряжения низкого уровня на входе  вынуждает МК приостановить свою работу на этапе выборки следующего элемента командной последовательности. Микроконтроллер подтверждает состояние останова высоким уровнем напряжения выходного сигнала ALE и выводом на шину BUS и младшую половину порта Р2 адреса следующей команды. Это состояние может продолжаться сколь угодно долго до момента перехода сигнала

вынуждает МК приостановить свою работу на этапе выборки следующего элемента командной последовательности. Микроконтроллер подтверждает состояние останова высоким уровнем напряжения выходного сигнала ALE и выводом на шину BUS и младшую половину порта Р2 адреса следующей команды. Это состояние может продолжаться сколь угодно долго до момента перехода сигнала  из 0 в 1, который выводит МК из режима останова, позволяя ему продолжать свою работу. Чтобы остановить МК на следующем шаге сигнал SS должен быть вновь активизирован сразу же после среза ALE. Простейшая схема организации пошаговой работы приведена на рис. 4.13.

из 0 в 1, который выводит МК из режима останова, позволяя ему продолжать свою работу. Чтобы остановить МК на следующем шаге сигнал SS должен быть вновь активизирован сразу же после среза ALE. Простейшая схема организации пошаговой работы приведена на рис. 4.13.

Рис. 4.13. Организация пошагового режима работы

При активации сигнала RESET выполняется общий сброс системы. Входная цепь встроенного в МК триггера Шмитта состоит из подключенного к источнику питания +5 В резистора и внешнего конденсатора емкостью 1 мкФ, что обеспечивает при включении питания формирование импульса системного сброса достаточной длительности. Длительность импульса, формируемого извне, должна быть не менее 50 мс при номинальном напряжении питания. Для стабилизации генератора требуется 5 машинных циклов. При АЕ = 1 во время импульса сброса ALE = 1 и PSEN = 1. При сбросе МК переходит в следующее исходное состояние:

РС0

SP0

BS0

MB0

ВUSz-состояние, кроме ситуации EA = 1

P1, P20FFH

DIS I, DIS TCNT

STOP TCNT

TF0

F0, F10

Запрет вывода CLK на Т0

Дата добавления: 2019-02-07; просмотров: 583;