Логічне моделювання

При логічному моделюванні можуть вирішуватися досить різноманітні задачі: перевірка логіки роботи схем, аналіз перехідних процесів, визначення надійності роботи схем у залежності від розкиду параметрів комплектуючих елементів, генерація тестів і т.п. У залежності від поставленої задачі вибирається метод моделювання. Основними відмітними рисами методів є: спосіб обліку часу поширення сигналу в схемі, спосіб кодування сигналів, спосіб реалізації програми, черговість моделювання елементів (рис. 4.3).

|

| |||||||||||||||||

|

| ||||||||||||||||

|

| ||||||||||||||||

|  | ||||||||||||||||

|  | ||||||||||||||||

Синхронні Двійкові Інтерпретації Наскрізні

Синхронні Двійкові Інтерпретації Наскрізні

Асинхронні Багатозначні Компіляції Подійні

Асинхронні Багатозначні Компіляції Подійні

Рисунок 4.3 - Класифікація методів логічного моделювання

У залежності від способу обліку часу поширення сигналу методи поділяються на синхронний (без урахування затримок в елементах схеми) і асинхронний (з урахуванням затримок); у залежності від способу представлення сигналів — на двійковий і багатозначний (трійковий, п'ятизначний і т.д.), по способі організації роботи програми моделювання — на метод компіляції і метод інтерпретації; по організації черговості моделювання наскрізний і подійний (рис. 4.15).

Синхронне логічне моделювання. При синхронному моделюванні моделі елементів представляються їхніми логічними функціями без урахування затримок сигналів, а сигнали — значеннями 0 і 1. Синхронне моделювання застосовується для оцінки правильності логічного функціонування дискретних пристроїв без урахування перехідних процесів. Моделювання роботи схеми зводиться до обчислення значень сигналів на виходах логічних елементів схеми по заданих вхідних сигналах. Моделювання проводиться для кожної зміни сигналів на входах. Звичайно ці зміни зв'язані із синхросигналами, тому ізначення сигналів на виходах елементів обчислюються для кожного синхросигнала. Передбачається, що в проміжку між синхросигналами вхідні сигнали не міняються, а перехідний процес у схемі завершується протягом якогось Dt, меншого періоду повторення тактуючих сигналів.

Найбільш зручне використання синхронного моделювання для аналізу роботи комбінаційних схем у сталому режимі. У цьому випадку результат моделювання точно відповідає реальній схемі.

Кожний з елементів схеми описується логічним рівнянням Y=f(x1, x2 ..., xп), де Y — вихідний, х1, x2, ... x3 — вхідні сигнали елемента. У результаті вся схема описується системою таких рівнянь. Синхронне моделювання зводиться до їхнього рішення послідовно одне за іншим. Під рішенням логічного рівняння розуміється обчислення логічного значення Y по відомих логічних значеннях х1, х2, ..., xn.

Особливістю синхронного моделювання є рішення логічних рівнянь у визначеному порядку, що відповідає послідовності проходження сигналів через елементи схеми. Для визначення цього порядку схему попередньо потрібно ранжувати, щоб до моменту рішення кожного рівняння Y=f(x1, x2 ..., xп) значення всіх x1, .... xn були відомі. При ранжуванні приймається, що вхідні сигнали схеми до моменту початку її моделювання відомі і їм привласнюється ранг r=0.

Для виконання ранжування схем розроблені відповідні формальні алгоритми, задача звичайно вирішується автоматично в самій системі моделювання.

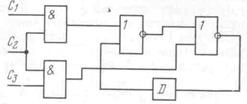

Трохи складніше моделюються логічні схеми зі зворотними зв'язками (рис. 4.4). Для розгляду принципів моделювання таких схем зручно в коло зворотного зв'язку ввести елемент затримки (у схемі на рис. 4.4 — елемент D). У реальних схемах затримка D як фізичний елемент відсутній, а затримка відбувається через кінцевий час спрацьовування комбінаційних схем.

Рисунок - 4.4 Логічна схема зі зворотними зв'язками

При моделюванні логічних схем зі зворотними зв'язками схема ранжується і моделюється як звичайна комбінаційна схема в припущенні, що в місці включення елемента затримки коло зворотного зв'язку тимчасово розмикається і колам зворотного зв'язку, підключеним до входів елементів, привласнюється ранг 0, такий же як і вхідним колам. При цьому вважається, що по колам зворотного зв'язку на входи елементів подаються сигнали, що відповідають раніше заданим станам 0 або 1. Схема моделюється і нові обчислені значення сигналів зворотного зв'язку подаються на входи елементів через деякий час Dt, рівний часу затримки кола зворотного зв'язку.

Для синхронних схем, у яких період синхроімпульсів дорівнює часу затримки D у колах зворотного зв'язку, на цьому моделювання закінчується. Для асинхронних схем, що не тактуються, цикл моделювання повторюється з новими значеннями сигналів зворотного зв'язку до появи сталого стану або до виявлення генерації — чергування 0 і 1 від циклу до циклу.

Результатом синхронного моделювання є часова діаграма, представлена у вигляді послідовності 0 і 1. На діаграмі для кожного такту моделювання приводяться значення вхідних сигналів і значення сигналів на виходах елементів схеми. По ній аналізується правильність роботи пристрою. Звичайно моделювання пристрою проводиться для деякої сукупності тестових сигналів, для яких відома еталонна реакція схеми. Зіставляючи в конкретному випадку результати з необхідною еталонною реакцією, визначають правильність роботи пристрою. У випадку виявлення невідповідності більш детальний аналіз часової діаграми дозволяє локалізувати помилки в схемі.

Синхронне моделювання з двійковим представленням сигналів є найпростішим способом моделювання. Його важлива перевага полягає у швидкості, однак синхронне моделювання не дозволяє аналізувати перехідні процеси в схемах і виявляти помилки, що можуть виникнути через затримку сигналів в елементах схеми.

Асинхронне моделювання. Аналіз перехідних процесів у логічних схемах ведеться асинхронним методом моделювання, у якому враховується час поширення сигналів в елементах і колах схеми.

Спрацьовування логічного елемента відбувається з деяким запізненням стосовно вхідних сигналів, що враховується затримкою в моделях елементів. Кожен елемент характеризується деякою середньою затримкою, значення якої може змінюватись в залежності від режиму роботи елемента, комбінації вхідних сигналів, температури, відхилення в технології виготовлення елемента і т.д. У залежності від необхідного ступеня адекватності моделювання облік затримок відбувається з тим чи іншим ступенем деталізації. Затримки в лініях зв'язку досить малі і звичайно не враховуються, однак при моделюванні пристроїв з дуже високою швидкодією враховуються і вони.

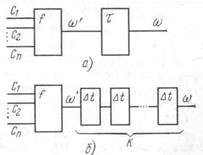

Модель логічного елемента для асинхронного моделювання представляється у виді послідовного з'єднання безінерційного логічного елемента, що реалізує зазначену функцію, і елемента затримки (рис. 4.5а).

Асинхронне моделювання полягає в обчисленні сигналів на виходах логічних елементів схеми відповідно до розглянутої моделі. При асинхронному моделюванні потрібно визначити не тільки стан на виході елемента (0 або 1), але і момент часу, коли відбулися зміни.

У найпростішому випадку при асинхронному наскрізному моделюванні багаторазово прораховуються стани елементів схеми через деякий інтервал часу Dt, що вибирається як найбільший загальний дільник часів затримок елементів, використовуваних у пристрої, що моделюється. Так, якщо в пристрої використовуються елементи, що мають затримки 15, 27, 21 і 30 нс, то Dt =3 нс.

Рисунок 4.5 - Асинхронна модель логічного елемента (а) і асинхронна модель з дискретними затримками (б)

Таким чином, кожен елемент має затримку t = KDt, де K=1,2,3,..., а модель елемента може бути представлена у вигляді ланцюжка (рис. 4.5б), у якому перший компонент реалізує логічну функцію, а інші К елементів — елементарні лінії затримки на Dt. За кожен цикл моделювання сигнали в схемі змінюється на час, рівний Dt. Якщо схема тактуюча, то час її такту Т розбивається на послідовність мікротактів тривалістю Dt і моделювання зводиться до багаторазового рішення рівнянь, що описують схему. Закінчення моделювання одного такту роботи схеми відбувається або після закінчення часу T, або по закінченні перехідного процесу в схемі.

При асинхронному моделюванні ранжування схеми не відбувається.

У порівнянні із синхронним асинхронне наскрізне моделювання вимагає виконання істотно більшої кількості обчислень. Обсяг програм також зростає через необхідність моделювання елементів затримок.

Асинхронне подійне моделювання. Аналіз роботи дискретних пристроїв показує, що одночасно знаходяться в активному стані лише 1...2,5% всіх елементів схеми. Звідси випливає, що істотне зменшення часу моделювання може бути досягнуто, якщо кожен раз моделювати тільки ті елементи, у яких змінилися вхідні сигнали. У цьому і полягає принцип подійного моделювання. Подія в системах подійного моделювання — це зміна стану якого-небудь елемента і зв'язаних з ним з'єднань. У системах асинхронного подійного моделювання час моделювання змінюється не поступово з заздалегідь заданим кроком Dt, а в моменти виникнення подій. Моменти ж виникнення подій визначаються затримками логічних елементів, що у загальному випадку різні.

У програмах асинхронного подійного моделювання важливу роль грають два масиви — масив стану кіл схеми, що моделюється, і черга майбутніх подій. Масив стану кіл зберігає поточні стани всіх кіл схеми, що моделюється у вигляді логічних 0 і 1. У чергу майбутніх подій (ЧМП) у процесі моделювання записуються події, що повинні відбутися в схемі, яка моделюється. Кожен елемент ЧМП містить номер кола, у якому повинно відбутися зміна стану (тобто відбудеться подія), і момент часу виникнення події. В ЧМП події записані в порядку зростання часу, і на вершині черги знаходиться подія, що відбудеться раніш усіх.

Асинхронне подійне моделювання виконується в такий спосіб. Перед початком моделювання встановлюється вихідний стан схеми шляхом запису значень у масив стану кіл. Тестові вхідні впливи, подавані в схему, заносяться в ЧМП відповідно до часу їхньої появи. Далі починається моделювання, що складається з наступних дій.

1. З ЧМП вибирається верхній елемент. Час, зазначений у ньому, заноситься в лічильник модельного часу, а в масив стану кіл по номеру, зазначеному в елементі, замість старого, заноситься запис нового стану кола, зазначеного в ЧМП.

2. Знаходяться логічні елементи, для яких даний коло є вхідним, і обчислюються значення сигналів на виходах цих елементів (тобто визначаються нові стани кіл) і їхні затримки.

3. Для кожного з кіл значення сигналу порівнюється зі значенням, що зберігається в масиві стану кіл, і, якщо вони не збігаються, то відбувається зміна стану кола, і подія заноситься в ЧМП. Якщо значення збігаються, то запис в ЧМП не відбувається.

Далі операції повторюються, починаючи з п. 1.

Процес моделювання закінчується при вичерпанні всіх елементів ЧМП або заданого часу моделювання.

Результати асинхронного моделювання представляються у виді часових діаграм, за яких і аналізується робота пристроїв, зокрема, виявляються критичні змагання, статичні і динамічні ризики збоїв. Найбільш повно поведінка пристрою, що моделюється, розкривається при формуванні затримок елементів з урахуванням їхнього випадкового характеру.

Недоліком асинхронного моделювання є істотно більший в порівнянні з синхронним час моделювання.

Значно швидше ризики збоїв і критичних змагань можуть бути виявлені моделюванням логічних схем з використанням багатозначного представлення сигналів.

Дата добавления: 2015-11-28; просмотров: 3213;