I. Краткое описание характеристик дешифратора

Дешифраторявляется логической интегральной схемой (ИС), содержащей n входов и 2n выходов. На входы дешифратора подается двоичное число, в результате чего один из его выходов изменяет состояние. Обычно при подаче на вход дешифратора какого-либо двоичного числа (например, число 310 = 0112) изменяет состояние его соответствующий (третий по порядку) выход Y3. Промышленность выпускает ИС дешифраторов с 2, 3 или с 4 входами. На рис. 1 приведен дешифратор с тремя входами С, В, А и соответственно с 8 выходами Y0, Y1, Y2, Y3, Y4, Y5, Y6 и Y7.

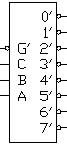

Рис 1. Дешифратор 3 х 8 (вход – 3 разряда, выходов – 8).

Во многих сериях микросхем активным состоянием выхода является низкий уровень – состояние логического "0". Таким образом при подаче на вход дешифратора (см. рис. 1) какого-либо двоичного числа (например, 011) соответствующий (третий по порядку) выход – 2’ будет находиться в состоянии лог. "0" (низкий уровень напряжения) а остальные выходы – в состоянии лог. "1" (высокий уровень напряжения).

ИС дешифратора обычно имеет дополнительный вход управления G (прямой или инверсный), который называется входом выбора микросхемы. Только при подаче сигнала на этот вход (при выборе данной ИС) дешифратор будет работать. У дешифраторов с инверсным входом управления активным уровнем является уровень логического нуля, а с прямым входом управления - уровень логической единицы. Часто ИС дешифратора имеет несколько управляющих входов. Тогда его можно использовать в качестве демультиплексора, логической схемы, подключающей сигнал ("1" или "0") с сигнального входа (второго входа управления) к одному из выходов Y0, Y1, Y2, Y3, Y4, Y5, Y6 и Y7.

Дата добавления: 2015-09-25; просмотров: 3539;