Исследование схемы каскадирования дешифраторов

Для увеличения разрядности дешифратора применяется каскадирование. Для этого входное двоичное число (код) на входе делится на части, при этом разрядность младших разрядов соответствует разрядности имеющейся ИС дешифратора. Оставшиеся старшие разряды входного числа поступают на комбинационную схему, выбирающую один из дешифраторов. Для этого подается сигнал выбора на вход G соответствующей ИС.

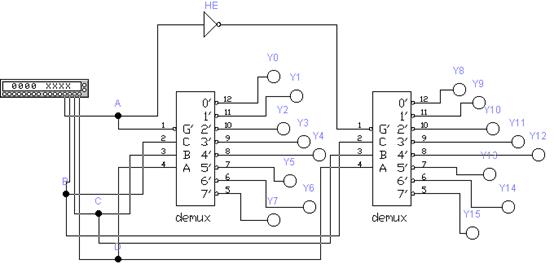

На рис. 3 изображена схема исследования каскадирования двух дешифраторов типа 3 х 8.

Рис. 3

Входной четырехразрядный код, формируемый генератором слов делится на две части: три младших разряда D, C, B подаются на входы двух дешифраторов параллельно. Старший разряд A подается на вход выбора G первого дешифратор и через инвертор – на вход G второго. В результате, если A = 0, то работает первый дешифратор, а если A = 1, то выбирается второй. В результате получаем дешифратор 4 х 16. Например, при подаче на вход схемы числа 1110 = 10112 выходной сигнал появится на выходе Y11 второго дешифратора.

Дата добавления: 2015-09-25; просмотров: 1493;