Организация памяти микроконтроллера

Микроконтроллеры семейства Intel 8051 имеют несколько адресных пространств. Функционально и логически они разделены за счет реализации различных алгоритмов адресации и формирования различных сигналов управления. К ним относятся: внешняя память программ (ВПП), резидентная память программ (РПП), внешняя память данных (ВПД), резидентная память данных (РПД).

Память программ предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных переменных и т.п.

Адресация ячеек памяти программ может осуществляться с использованием программного счетчика PC или регистра-указателя данных DPTR.

Резидентная память программ адресуется с использованием счетчика команд PC. Младшие адреса резидентной памяти программ отведены под обработку внешних прерываний, прерываний от таймеров/счетчиков, последовательного порта и дополнительных устройств.

Рисунок 3 – Организация памяти программ

В случае возникновения какого-либо из указанных прерываний происходит обращение к соответствующей ячейке резидентной памяти программ (например, при возникновении прерывания от таймера Т0 в PC записывается адрес вектора прерываний 000Вh).

При обращении к внешней памяти программ микроконтроллеры семейства Intel 8051 всегда используют полный 16-разрядный адрес, что обеспечивает доступ к 64 Кбайт внешней памяти программ ВПП. Обращение к внешней памяти программ сопровождается сигналом чтения внешней памяти программPSEN(Program Store Enable) и возможно в двух случаях:

1. Когда сигнал ЕАактивен, т.е. имеет уровень логического нуля, микроконтроллер выполняет программу с нулевого адреса внешней памяти программ.

2. Когда программный счетчик РС содержит число больше 0FFFh (последний адрес РППпри объеме 4 Кбайт) – микроконтроллер, выбрав команды из внутренней памяти, продолжает выполнять программу из внешней памяти программ.

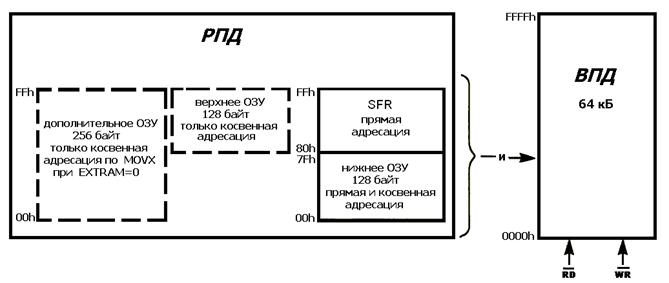

Объем внешней памяти данных может достигать 64 Кбайт. Для обращения к внешней памяти данных используется только косвенная адресация с помощью регистров R0 и R1 или с помощью 16-разрядного регистра-указателя DPTR. Обращение к внешней памяти данных сопровождается стробирующими сигналами чтения RD^ и записиWR^.

Если при обращении к внешней памяти данных используется восьмибитный адрес, то на выводах порта Р2остается та же информация, которая там была до начала обращения к внешней памяти. Это позволяет организовать постраничную адресацию внешней памяти данных. Выводимый в цикле записи байт данных заносится в P0 непосредственно перед активацией сигнала WR^ и остается неизменным до окончания этого сигнала. В цикле чтения данные на выводах P0 для достоверного считывания должны установиться к моменту окончания сигнала RD^.

Рисунок 4 – Организация памяти данных

Резидентная память данных РПД предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт (адреса с 00H по 7FH). В РПД выделяют несколько специализированных областей (табл. 1).

Таблица 1 - Структура резидентной памяти данных

| Адреса RDM | Абсолютный битовый адрес | |||||||

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | |

| 30-7FH | Неспециализированная область памяти | |||||||

| 20-2FH | Побитно адресуемая область памяти | |||||||

| 2FH | 7A | 7B | 7C | 7D | 7E | 7F | ||

| 2EH | ||||||||

| 2DH | 6A | 6B | 6C | 6D | 6E | 6F | ||

| 2CH | ||||||||

| 2BH | 5A | 5B | 5C | 5D | 5E | 5F | ||

| 2AH | ||||||||

| 29H | 4A | 4B | 4C | 4D | 4E | 4F | ||

| 28H | ||||||||

| 27H | 3A | 3B | 3C | 3D | 3E | 3F | ||

| 26H | ||||||||

| 25H | 2A | 2B | 2C | 2D | 2E | 2F | ||

| 24H | ||||||||

| 23H | 1A | 1B | 1C | 1D | 1E | 1F | ||

| 22H | ||||||||

| 21H | 0A | 0B | 0C | 0D | 0E | 0F | ||

| 20H | ||||||||

| 18-1FH | Банк 3 | |||||||

| 10-17H | Банк 2 | |||||||

| 08-0FH | Банк 1 | |||||||

| 00-07H | Банк 0 |

Первые 32 байта памяти данных с 00h по 1Fh организованы в четыре банка регистров общего назначения, обозначаемых соответственно Банк 0 - Банк 3. Каждый из них состоит из восьми регистров R0 - R7.

В любой момент программе доступен только один банк регистров, выбор которого производится в регистре слова состояния программы PSW.

Следующие 16 байт памяти данных с 20h по 2Fh представляют собой так называемую побитно адресуемую область. Она предоставляет возможность при помощи специальных команд обратиться к каждому из 128 бит ячеек памяти.

При адресации бит, может быть указан либо абсолютный битовый адрес, либо символический адрес в формате <АдресБайта>. <Разряд>.

Например, выражение 2A.4 означает четвертый бит ячейки памяти с адресом 2Ah, абсолютным битовым адресом которого является 54h.

С адресным пространством резидентной памяти данных граничит адресное пространство блока регистров специальных функций SFR(Special Function Register) c80h по FFh.

Отметим, что не занятые ячейки блока SFR физически отсутствуют. При обращении к ним на кристаллах микроконтроллеров семейства Intel 8051 можно прочитать лишь код команды возврата.

Дата добавления: 2015-05-21; просмотров: 2862;