Оперативное запоминающее устройство: назначение, реализация триггерной схемы.

Триггерная схема

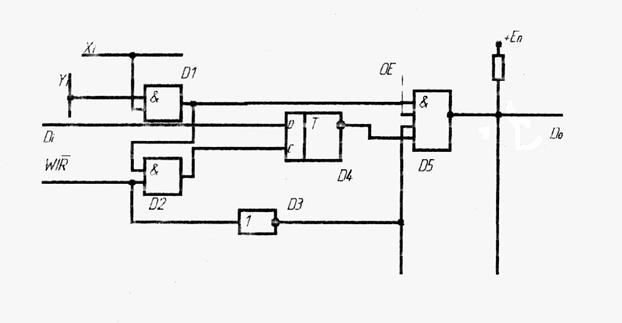

В качестве элементарной ячейки памяти может выступать обычный D-триггер.

Xi и Yi – пересечение строк и столбцов матричного дешифратора.

Определение ячейки памяти осуществляется дешифратором, в частности матричный дешифратор формирует уникальную комбинацию, приводящую к появлению 1 на выходе конъюнктора D1, который открывает конъюнктор D2 и выходной конъюнктор D5.

Если при этом  =1, то D5 закрывается через инвертор D3. На вход С триггера поступает активный уровень, при этом информация, присутствующая на входе D1 записывается в определенную ранее ячейку памяти.

=1, то D5 закрывается через инвертор D3. На вход С триггера поступает активный уровень, при этом информация, присутствующая на входе D1 записывается в определенную ранее ячейку памяти.

Если  =0, сигнал С на входе триггера не активен, запись информации не осуществляется, одновременно с этим открывается выходной конъюнктор D5 и состояние выхода

=0, сигнал С на входе триггера не активен, запись информации не осуществляется, одновременно с этим открывается выходной конъюнктор D5 и состояние выхода  передается на выход системы с инверсией. Выходной конъюнктор выполнен по схеме с открытым коллектором, что дает возможность организовать схему монтажного «ИЛИ», объединяя выводы сколь угодно большого числа ячеек памяти.

передается на выход системы с инверсией. Выходной конъюнктор выполнен по схеме с открытым коллектором, что дает возможность организовать схему монтажного «ИЛИ», объединяя выводы сколь угодно большого числа ячеек памяти.

Как правило, по одному адресу располагают не одну ячейку памяти, а 8 (16, 32, и т.д.), делая возможным одновременно записывать (считывать) байт (слово) информации.

Поскольку запись и считывание – процессы принципиально различные и, как правило, не выполняющиеся одновременно. Вход DI объединяют с DO, получая линию ввода-вывода.

Ао – Аn - адрес, CS – выбор кристалла, ОЕ – вывод запрещен.

Дата добавления: 2016-02-16; просмотров: 1288;