Лекция №5. Структура и принцип действия типового однокристального микропроцессора

Содержание лекции: состав, структура и принцип действия 8-разрядного однокристального микропроцессора, назначение основных узлов.

Цели лекции:изучить основной состав типового микропроцессора, его структуру и принцип действия, освоить назначение основных узлов.

Развитие микроэлектронной технологии привело к появлению микросхем большой и сверхбольшой степени интеграции (БИС и СБИС), которые стали основой для создания микропроцессоров (МП). МП – это программно-управляемое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, реализованное в виде одной (однокристальный МП) или нескольких БИС или СБИС (модульный МП). Под обработкой цифровой информации понимается выполнение некоторых арифметических и логических операций. Исходя из определения, данному МП, он должен состоять из арифметико-логического устройства (АЛУ) и устройства управления процессором (УУП). Кроме того, ему необходима внутренняя память, реализованная на регистрах общего назначения (РОН), для хранения кодов и адресов команд и операндов (двоичные слова, участвующие в операциях). На рисунке 15 представлен основной состав МП и внешнее оборудование, необходимое для его нормального функционирования.

|

Рисунок 15 – Упрощенная схема типовой микропроцессорной системы

Как видно из рисунка 15, в качестве внешнего оборудования используются:

а) память (ОЗУ и ПЗУ) для хранения программ и данных;

б) внешние запоминающие устройства (ВЗУ) для увеличения объема памяти (накопители на магнитных лентах, дисках);

в) специальные устройства, предназначенные для ввода в МП или вывода из него информации (УВВ);

г) блок управления для координации управления всех вышеперечисленных узлов.

Функционирование процессора происходит в следующем порядке:

1) выборка из памяти команды;

2) анализ кода операции и определение ее типа, количества операндов;

3) вычисление адресов и выборка из памяти операндов;

4) выполнение команды;

5) переход к адресу следующей команды и повторение цикла.

Для изучения основных принципов работы МП выберем наиболее простую его модель фирмы Intel i8080А (аналог - К580ВМ80А) или i8085 (аналог – К1821ВМ85А). Несмотря на свой многолетний возраст, эти МП до сих пор встречаются в каталогах фирм и применяются в системах управления различной аппаратурой, где возможностей микропроцессора хватает.

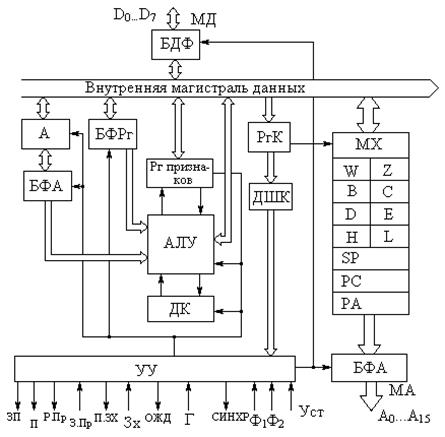

На рисунке 16 представлена структурная схема однокристального восьмиразрядного МП i8080A, из которой видно, что МП связан с внешним оборудованием через магистральную систему шин: однонаправленной 16-разрядной магистралью адреса (МА), двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления по шине управления (6 входных и 6 выходных).

Данный МП рассчитан на выполнение логических и арифметических операций с 8-разрядными числами в двоичной и двоично-десятичной системах счисления, а также операций с двойной разрядностью.

Функциональное назначение внешних выводов МП следующее:

А0...А15 - адресная магистраль, обеспечивающая адресацию любой из 216 8-разрядных ячеек памяти или внешнего устройства (ВУ);

Д0...Д7 - двунаправленная магистраль данных, используемая для обмена информацией с памятью или ВУ;

СИНХР (SYNC) - выход сигнала СИНХРОНИЗАЦИЯ появляется в начале каждого машинного цикла для временного согласования МП с ВУ;

П (DBIN) – выход сигнала ПРИЕМ указывает на готовность к приему данных, выданных из памяти или ВУ;

ОЖД – выход сигнала ОЖИДАНИЕ указывает на то, что МП находится в режиме ожидания готовности ВУ к работе;

ЗП (WR) - выход сигнала ЗАПИСЬ указывает, что данные выданы МП и установлены на МД, т.е. могут быть записаны в память или переданы в ВУ;

Зх (HOLD) - вход сигнала ЗАХВАТ указывает на запрос ВУ на управление МА и МД;

П.ЗХ.(HLDA) - выход сигнала ПОДТВЕРЖДЕНИЕ ЗАХВАТА указывает на перевод МД и MA в состояние высокого сопротивления, используется при режиме прямого доступа к памяти;

З.Пр.(INT) - вход сигнала ЗАПРОС ПРЕРЫВАНИЯ, поступает от внешнего устройства с требованием прерывания основной программы и перехода на выполнение подпрограммы обслуживания прерывания;

Р.Пр.(INTE) - выход сигнала РАЗРЕШЕНИЕ ПРЕРЫВАНИЯ указывает на состояние внутреннего триггера разрешения прерывания МП;

Г (READY) - сигнал ГОТОВ информирует о готовности ВУк обмену информацией с МП. При Г = 0 МП будет находиться в состоянии ОЖД;

УСТ (RESET) – вход СБРОС, для сбрасывания в 0 счетчика команд и передачи в регистр адреса нулевого адреса первой команды;

Ф1 и Ф2 - входы для подачи тактовых противофазных сигналов Ф1 и Ф2 , которые определяют тактовую частоту работы МП (2,08; 2,63; 3,125).

|

Рисунок 16 - Структурная схема однокристального МП i8080A

Микропроцессор i8080A состоит из следующих функциональных блоков:

1) блока регистров общего назначения PОH;

2) арифметико-логического блока АЛБ;

3) регистра команд РгК;

4) устройства управления УУ;

5) буферов магистрали данных - БФД и магистрали адреса - БФА.

Блок PОH включает в себя шесть программно-доступных регистров: В, С, D, Е, Н, L. Их можно использовать как отдельные 8-разрядные регистры или как три 16-разрядных регистра ВС, DЕ, HL. Регистры W и Z не доступны программисту и используются для выполнения команд внутри МП.

Программный счетчик PC содержит текущий адрес памяти. Содержимое PC автоматически изменяется в течение каждого цикла команды. Указатель стека SP содержит адрес последней записанной в стек информации. PA - регистр для хранения адреса памяти. MX - двунаправленный мультиплексор для связи РОН с магистралью данных.

АЛБ включает в себя 8-разрядное АЛУ, схему десятичной коррекции ДК, 5-разрядный регистр признаков, аккумулятор А, буфер аккумулятора БФА и буферный регистр БФРг. АЛБ осуществляет арифметические операции сложения и вычитания, логические операции И, ИЛИ, ИСКЛЮЧАЮЩИЕ ИЛИ и сдвиги. При проведении операций одно число всегда берется из БФА, а другое - из БФРг.

По результату выполнения арифметическо-логических операции АЛБ устанавливает в регистре признаков один из пяти разрядов:

1) бит переноса C устанавливается в состояние логической 1 при переносе из старшего разряда числа при выполнении арифметических операций, а при операциях сдвига – в состояние, соответствующее содержимому выдвигаемого из аккумулятора разряда;

2) дополнительный признак переноса (при обработке двоично-десятичных чисел) хранит при выполнении операции перенос из 4-го разряда;

3) бит знака устанавливается в состояние, соответствующее значению старшего разряда операции АЛУ;

4) бит нулевого признака устанавливается в состояние логической 1, если результат операции АЛУ равен нулю;

5) разряд признака четности устанавливается в состояние логической 1, если число единиц в разрядах результата четное.

Регистр команд РгК и дешифратор команд ДШК используются в МП для получения и дешифрации кода команды.

Устройство управления совместно с дешифратором формирует управляющие сигналы для всех внутренних блоков микропроцессора, а также его выходные сигналы управления и состояния.

Буферы МД и МА обеспечивают хранение соответственно данных и адресов на время, необходимое для их обработки.

Выполнение каждой команды производится МП в строгой последовательности, определяемой кодом команды, и синхронизируется во времени сигналами Ф1 и Ф2 тактового генератора. Период синхросигналов Ф1 и Ф2 называется машинным тактом. Машинный цикл - время, требуемое для извлечения одного байта информации из памяти или выполнения команды, определяемой одним машинным словом. Машинный цикл может состоять из 3...5 машинных тактов. Время выполнения команды - время получения, декодирования и выполнения команды. В зависимости от вида команды оно может состоять из I...5 машинных циклов.

Дата добавления: 2015-12-01; просмотров: 3171;