ОСОБЕННОСТИ ПОДКЛЮЧЕНИЯ ТРИГГЕРОВ

Если входы триггеров R, S, J, К, D, вход синхроимпульсов и

установочные входы не подключены, то сигналы на них будут

восприниматься как единичные.

Заземление входа предустановки переводит триггер в состояние 1, а входа очистки переводит триггер в состояние 0.

На входах R и S должны быть всегда противоположными сигналы.

Выходы J и К, если на оба поданы сигналы высокого уровня (1), нуждаются в синхронизации для работы триггера в синхронном режиме.

Основные типы триггеров срабатывают по фронту синхроимпульса. Двухтактные триггеры из-за передачи информации от первого ко второму триггеру вырабатывают выходной сигнал по спаду синхроимпульса.

Т.е. входы, которые переключают триггер нулевым сигналом (предустановки, очистки, синхроимпульса для двухтактных триггеров), обозначаются на структурных схемах с горизонтальной чертой сверху.

ОСНОВНЫЕ ФУНКЦИОНАЛЬНЫЕ УЗЛЫ

Различные блоки и устройства ЭВМ можно построить из типовых элементов ограниченной номенклатуры: триггеров, схем И, ИЛИ и инверторов. При помощи комбинации этих базовых логических схем можно построить регистры для хранения и сдвига информации, счетчики, сумматоры, селекторы, дешифраторы, блоки памяти и т.д.

РЕГИСТР

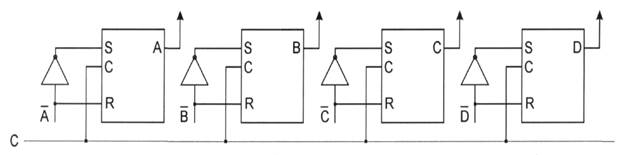

Триггер можно использовать для хранения одного бита информации. Двоичные числа в общем случае содержат n бит, поэтому необходимо устройство, обеспечивающее хранение n бит. Его можно построить, объединив n RS триггеров. Такая схема называется n – битовым или n – разрядным регистром.

Входы R и S используются для параллельного ввода n –битовой информации. Так как входы R и S должны поступать противоположные сигналы, то на входе каждого триггера используется вспомогательный инвертор. Регистры можно построить используя отдельные триггеры, либо стандартные блоки в интегральном исполнении. Например, четырехбитовый регистр с параллельными входами и выходами.

|

A B C D

A B C D

C

A B C D

СДВИГОВЫЙ РЕГИСТР

Сдвиг числа по разрядам является одной из основных операций в ЭВМ. Сдвиговый регистр - это схема, которая способна сдвигать свое содержимое без изменения последовательности битов. Можно обеспечить сдвиг вправо, влево и сдвиг на 1, 2 или любое число разрядов.

Рассмотрим четырехбитовый сдвиговый регистр,

|  |  |  |

A B C D

A B C D

C

| |||||||||||

|  |  |  | ||||||||

| |||||||||||

|  |  |  |

параллельный выход

|

последовательный

последовательный

|

вход очистка

параллельный вход

в котором выполняется сдвиг вправо на один разряд. Сдвиговый регистр состоит из двухтактных RS - триггеров. Двоичное число вводится в сдвиговый регистр через входы предустановки. Каждый синхроимпульс сдвигает число на один разряд право. Например, число 1101 через 1,2,3,4 тактов сдвига. После первого сдвига самый правый (крайний справа) бит первоначальной информации сдвигается из регистра и теряется. Крайний левый бит станет равным нулю, т.к. на его вход не подается никакой информации. Операция сдвига на один разряд проходит следующие стадии:

|

A 0 0 0 0

1 1

B 0 0 0

0 0 0

C 1 1

D 1 1 1

0 0

|

- фронт синхроимпульса, опрашивает входы А и А, и записывает

информацию в триггере В. Таким же образом будут происходить сдвиги из В в С, из С в D.

- спад синхроимпульса передает информацию на выходы двухтактных триггеров, подготавливая ее для выполнения следующего сдвига.

Сдвиговые регистры можно построить, используя отдельные триггеры, либо используя стандартные интегральные схемы.

ДВОИЧНЫЙ СЧЕТЧИК

|

|

|

|

Вход

|  |  |  | ||||||||||||

|  |  |  |

Очистка

|

R

R

A B C D

Вход Очистка

Общая шина очистки может использоваться для установки счетчика в исходное нулевое положение. Если К импульсов поступают на вход счетчика, то состояния 4-разрядов счетчика будет представлять двоичное число К.

|

0 1 0 1 0

A

0 0 0

B 1 1

C 0 0 0 0 1

0 0 0 0 0

D

Спад первого импульса установит триггер А в состояние 1. На выходе счетчика после первого импульса образуется число 0001.

Спад второго импульса переведет триггер А в состояние 0. Отрицательный перепад напряжения на выходе А установит триггер В в состояние 1. На выходе счетчика после второго импульса образуется число 0010 и т.д.

ДЕСЯТИЧНЫЙ СЧЕТЧИК

Другим стандартным интегральным блоком является десятичный (декадный) счетчик. Он имеет счетный вход, вход установки в ноль, и четырехбитовый выход. Этот счетчик выдает результат в двоично-десятичной форме. Это достигается благодаря наличию обратных связей между двоичными триггерами. Двоичная и двоично-десятичная последовательности сигналов одинаковы для счетчика от 0 до 9.

A B C D

|

Вход Очистка

Вход Очистка

| Счетный импульс | Выход двоичного счетчика | Выход двоично-десятичного счетчика | ||||||

| D | C | B | А | D | C | B | А | |

После 9 импульсов двоичная последовательность продолжается, в то время как двоично-десятичная прекращается. Таким образом на выходе двоично-десятичного счетчика каждая десятичная цифра представляется четырьмя двоичными разрядами.

ПОЛНЫЙ СУММАТОР

Суммирование несколько сложнее из-за необходимости учитывать перенос. Сложение для (n+1)-го разряда осуществляется над цифрами слагаемых А(n+1) и B(n+1) с учетом переноса Сn справа. Результатом является цифра суммы в разряде n и возможная единица, которую необходимо перенести влево ( перенос C(n+1)).

Однобитовый сумматор имеет входы для (n+1)-го разряда числа А и (n+1)-го разряда числа В и переноса Сn. Он обеспечивает выходы на суммы I (прямой) и Z (инверсный) и переноса C(n+1) для последующего бита слева.

Четырехбитовый сумматор имеет входы А1, А2, А3, А4, В1, В2, В3, В4 и входа переноса из предыдущего разряда Сn. Он обеспечивает выходы Z1, Z2, Z3, Z4 и перенос в следующий разряд Сn+4.

|

An+1 Σ однобитовый

An+1 Σ однобитовый

Bn+1 Σ сумматор

Bn+1 Σ сумматор

Cn Cn+1

Cn Cn+1

|

|

| ||||||

четырехбитовый

полный сумматор

Дата добавления: 2015-12-01; просмотров: 929;