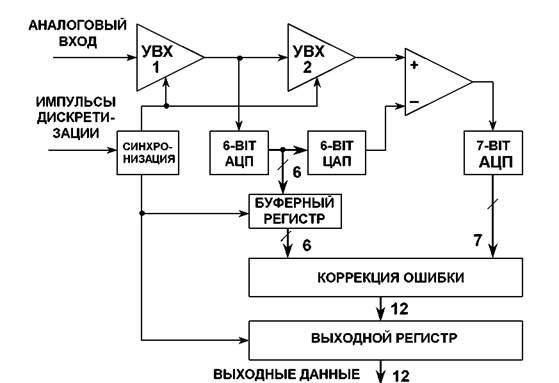

АРХИТЕКТУРА 12-РАЗРЯДНОГО ДВУХСТУПЕНЧАТОГО

КОНВЕЙЕРНОГО АЦП

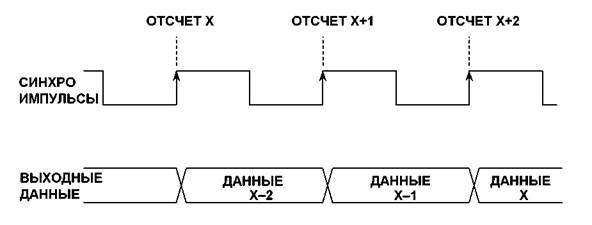

Рис. 3.7 ВРЕМЕННАЯ ДИАГРАММА РАБОТЫ КОНВЕЙЕРНОГО АЦП

ПОКАЗАНА РАБОТА С ЗАДЕРЖКОЙ НА 2 ТАКТОВЫХ ЦИКЛА

Рис. 3.8

Конвейерные АЦП могут иметь более двух тактов задержки в зависимости от специфики своей архитектуры. Например, возможно выполнение преобразования за три, четыре или, возможно, даже большее количество конвейерных ступеней, что вызывает дополнительную задержку выходных данных.

Поэтому, если АЦП используется в событийно-управляемом (event-triggered ) (или однократном single-shot) режиме, требующем однозначного соответствия времени между каждым отсчетом и соответствующими данными, то конвейерная задержка может привести к нежелательному результату, и в этом случае более предпочтительна архитектура АЦП последовательного приближения. Конвейерная задержка или ожидание могут также создать проблемы в высокоскоростных системах управления с обратной связью или в приложениях с мультиплексированием данных. Кроме того, некоторые конвейерные преобразователи рассчитаны на определенную минимально допустимую скорость преобразования и должны непрерывно поддерживаться в рабочем состоянии для предотвращения насыщения внутренних узлов.

АЦП последовательного приближения с коммутируемыми конденсаторами имеет небуферированные входные цепи, подобные схеме, показанной на рис.3.9 для АЦП AD7858/59. За время сбора данных аналоговый входной сигнал должен зарядить эквивалентную входную емкость 20 пФ до необходимой величины. Если входной сигнал является сигналом постоянного тока, то сопротивление источника RS, включенное последовательно с внутренним сопротивлением выключателя 125 Ом, создает задержку с некоторой постоянной времени. Для достижения 12-разрядной точности необходимо предусмотреть интервал ожидания, соответствующий приблизительно промежутку в 9 постоянных времени для стабилизации сигнала на входе. Это определяет минимальное допустимое время выборки (достижение 14-разрядной точности требует приблизительно 10 постоянных времени, а 16- разрядная точность требует приблизительно 11 постоянных времени).

tACQ > 9 Ч (RS + 125) Ом × 20 пФ.

Например, если RS = 50 Ом, то время выборки в этой формуле должно быть, по крайней мере, 310 нс.

В приложениях переменного тока, чтобы предотвратить искажения из-за нелинейности входной цепи АЦП, должны использоваться источники сигнала с низким выходным сопротивлением. В случае приложения с однополярным питанием должен использоваться полнодиапазонный (rail-to-rail) операционный усилитель типа AD820 с малым временем установки выходного сигнала. Малое время установки позволяет операционному усилителю быстро устранять возникающие на его входе токи переходного режима, вызванные внутренними переключениями АЦП. На рис.3.9 AD820 управляет ФНЧ, состоящим из резистора 50 Ом и конденсатора 10 нФ (частота среза приблизительно 320 КГц). Этот фильтр удаляет высокочастотные компоненты, которые могут приводить к эффекту наложения и уменьшают шум.

Использование в этом приложении операционного усилителя с однополярным питанием требует специального рассмотрения уровней сигнала. AD820 включен в инвертирующем режиме и имеет коэффициент усиления сигнала -1. На неинвертирующий вход усилителя с делителя 10,7 К/10К подается синфазное напряжение смещения +1,3 В, создавая выходное напряжение +2,6 В для VIN = 0 В, и +0,1 В для VIN = +2,5 В. Это смещение необходимо потому, что выход AD820 не может быть полностью заземлен, т.к. это ограничивается напряжением VCESAT n-p-n-транзистора выходного каскада, которое при этих условиях нагрузки приблизительно равно 50 мВ. Диапазон изменения входных

сигналов АЦП также смещен на +100 мВ, благодаря подаче от делителя 412 Ом/10 кОм смещения +100 мВ на вход AIN.

Дата добавления: 2016-01-07; просмотров: 1582;