Методы Изоляции элементов друг от друга в микросхемах

При отсутствии изоляции элементов биполярных микросхем все они окажутся электрически связанными между собой через подложку. Изоляцию осуществляют с использованием нескольких конструктивно–технологических вариантов.

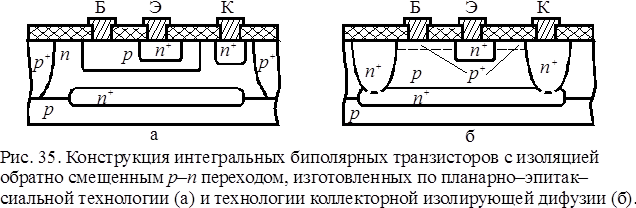

Изоляция обратно–смещенными p–n переходами (см. рис. 1). Этот способ, будучи исторически первым, распространен и по сей день, так как обладает высокой технологичностью, операции создания изолирующей области (дополнительно одна операция фотолитографии и одна операция диффузии) естественным образом вливаются в технологический маршрут, не требуют ни дополнительного оборудования, ни использования новых материалов. Конструкция транзистора изолированного от других элементов микросхемы p–n переходом, показана на рис. 35, а. Недостатком этой конструкции является то, что площадь изолирующей области сравнима с площадью, отводимой под транзистор, и даже превышает ее. Попытка устранить хотя бы частично этот недостаток без изменения способа изоляции привела к созданию транзистора, изображенного на рис. 35, б, в котором изолирующая область сформирована диффузией примеси n–типа на всю глубину эпитаксиального слоя до соприкосновения со скрытым n+–слоем и используется в качестве коллекторной области транзистора.

|

Изоляция элементов полупроводниковых микросхем с помощью обратно смещенного p–n перехода кроме указанного имеет и другие принципиально неустранимые недостатки. К ним относятся: большая паразитная емкость изолирующих p–n переходов и появление дополнительных паразитных элементов в структуре микросхемы; необходимость подачи на изолирующий p–n переход определенного по величине и знаку напряжения смещения; наличие четырехслойных структур n–p–n и p–n–p типа, которые обладают положительной обратной связью по току, вследствие чего при воздействии на них ионизирующих факторов увеличение тока через эти структуры будет приводить к еще большему его возрастанию.

Указанные недостатки не позволяют добиться существенных успехов в росте быстродействия микросхем, увеличения степени их интеграции, радиационной стойкости и стабильности в интервале температур.

|

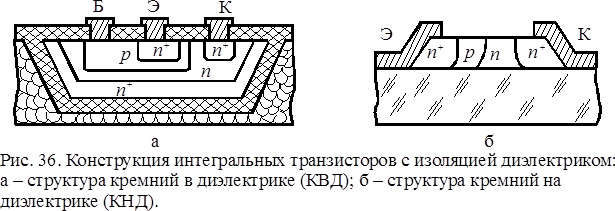

Изоляция диэлектриком. Конструкция интегрального транзистора, изолированного от соседних элементов микросхемы с помощью диэлектрика, показана на рис. 36. Пленка диэлектрика (SiO2) и непроводящая подложка устраняют кардинальным обрезом недостатки, присущие изоляции p–n переходами. Но для осуществления такого способа изоляции необходим довольно сложный технологический процесс, включающий в себя операции по размещению в диэлектрическом материале островков монокристаллического кремния и операции по формированию p–n переходов в этих островках (рис. 36, а). Труден подбор материала диэлектрической положки для этой конструкции, поскольку коэффициенты термического расширения подложки и монокристаллического кремния должны совпадать, иначе проведение операций, связанных с нагревом, станет невозможным из–за коробления структур и появления дефектов в кристаллической решетке кремния.

Структура, изображенная на рис. 36, а, носит название кремний в диэлектрике (КВД), а структура на рис. 36, б — кремний на диэлектрике (КНД).

Основными недостатками конструкций с диэлектрической изоляцией элементов являются: сложный технологический процесс и малый выход годных микросхем; плохой отвод тепла от элементов микросхемы в подложку, поскольку тепловое сопротивление диэлектрических материалов в десятки раз больше теплового сопротивления монокристаллического кремния; трудность создания разводки из–за сравнительно большого перепада высот рельефа поверхности в структурах КНД; высокая плотность дефектов структуры в изолированных островках кремния и низкая воспроизводимость параметров элементов микросхем.

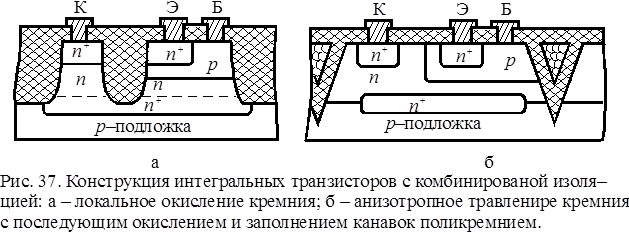

Комбинированная изоляция сочетает технологичность изоляции p–n переходом и высокие качества диэлектрической изоляции: элементы микросхемы со стороны подложки изолированы обратно–смещенными p–n переходами, а с боковых сторон – диэлектриком (окислом, стеклом, керамикой, поликремнием и т.д.). Таким образом, изоляция p–n переходами заменяется изоляцией диэлектриком в наиболее уязвимом приповерхностном слое и с боковых сторон.

|

Наибольшее распространение сегодня получили такие варианты комбинированной изоляции, как локальное окисление (изопланарная технология) (рис. 37, а) и вертикальное анизотропное травление с последующем заполнением канавок поликристаллическим кремнием (полипланарная технология) (рис. 37, б).

В основе технологических процессов лежит локальное сквозное “прокисление” или протравление тонкого (2…3 мкм) эпитаксиального слоя кремния n–типа, в результате этот слой оказывается разделенным на островки, в которых формируются элементы микросхем.

Комбинированная изоляция позволяет уменьшить паразитные емкости изолированных областей на подложку за счет устранения боковых участков p–n переходов (см. рис. 35), устранить токи утечки в области выхода p–n переходов на поверхность и на боковых участках p–n переходов (см. рис. 35). В то же время при методе комбинированной изоляции удается обеспечить хорошие условия теплоотвода и увеличить степень интеграции элементов в микросхеме за счет сокращения площади, отводимой под изоляцию.

Дата добавления: 2016-01-07; просмотров: 6268;