Организация памяти и способы адресации

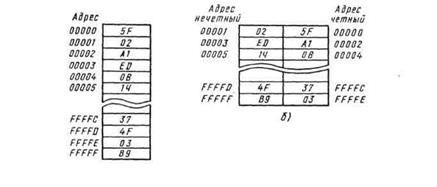

Важным моментом в изучении способов адресации является понятие логической и физической памяти. Как показано на рис. 1.5, память логически организуется в виде последовательности смежных байтов, которые образуют двухбайтовые слова, причем младшим байтам слов соответствуют меньшие значения адресов. Если многобайтовое слово записывается, как обычно, слева направо, то в память байты записываются в обратном порядке. Память с таким порядком размещения информации в словах называют памятью с «перевернутыми словами».

В ВМ на базе Intel 8086 первые байты слов могут иметь как четные, так и нечетные адреса в памяти. Если слово начинается с четного адреса, обращение к нему произойдет в одном цикле, в то время как обращение к слову с нечетным адресом младшего байта займет два цикла. Поэтому для сокращения времени выполнения программ целесообразно располагать слова в памяти так, чтобы их младшие байты имели четные адреса.

a)

Рис. 1.5. Логическая (а) и физическая (б) организация памяти

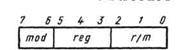

В зависимости от типа команды операнд может представлять собой байт или слово и храниться в РОН или памяти. В большинстве команд для адресации операндов используется специальный байт, который называется

постбайтом и размещается вслед за первым байтом, содержащим код операции.

|

Рис. 1.6. Структура постбайта

Постбайт, структура которого представлена на рис. 1.6, указывает способ адресации одного или двух операндов и состоит из трех полей. Поля mod и r/т задают местоположение одного операнда следующим образом: если mod=11, то операндом является содержимое регистра, двоичный код (номер) которого задается в 3-разрядном поле r/т в соответствии с табл. 1.1а.

Если тod=11, то в полях mod и r/т содержится информация, согласно которой устанавливается один из способов адресации - прямая, косвенная регистровая, по базе, индексная и по базе с индексированием. Если для реализации выбранного способа адресации требуется дополнительная адресная информация, то она указывается в одном или двух байтах в виде смещения disp, которое следует непосредственно за постбайтом. Наличие или отсутствие смещения и его размерность определяются полем mod следующим образом:

· если mod = 00, то disp отсутствует;

· если mod=01, то disp размерностью 1 байт указывается за постбайтом, причем перед использованием этого смещения при формировании исполнительного адреса ЕА оно расширяется со знаком до 16 разрядов (расширение со знаком подразумевает заполнение старшего байта значением знакового разряда, указанного в disp);

· если mod=10, то за постбайтом следует 16-разрядное смещение disp, рассматриваемое как число со знаком.

| Код в поле r/m | Значение исполнительного адреса ЕА |

| (BX+SI)+disp | |

| (BX+DI)+disp | |

| (BP+SI)+disp | |

| (BP+DI)+disp | |

| (SI)+disp | |

| (DI)+disp | |

| (BP)+disp | |

| (BX)+disp |

Таблица 1.1б

Таблица 1.1а

| Код регистра | Регистр | |

| 16-разрядный | 8-разрядный | |

| AX | AL | |

| CX | CL | |

| DX | DL | |

| BX | BL | |

| SP | AH | |

| BP | CH | |

| SI | DH | |

| DI | BH |

Для каждой комбинации значений поля mod 00, 01 или 10 формирование исполнительного адреса ЕА определяется полем r/т в соответствии с табл. 1.1б. Исключение из описанных способов кодирования полей mod и r/т составляет случай mod=00, r/т=110, соответствующий EA = disp, причем disp- есть 16-разрядное смещение. Таким образом, при обращении к памяти имеется 24 варианта вычисления адреса ЕА, используемого в качестве смещения в сегменте при вычислении физического адреса.

|

|

|

|

|

|

Рис. 1.7. Форматы команд центрального процессора

Поле reg постбайта используется для адресации тогда, когда в команде задаются два операнда. В этом случае второй операнд всегда находится в регистре, код которого указывается в поле постбайта в соответствии с табл. 1.1. В командах, где требуется только один операнд, поле reg постбайта используется совместно с байтом кода операции (КОП) для увеличения вариантов кодирования операций. Всего в ЦП используются восемь способов адресации, из которых пять реализуются с помощью постбайта. На рис. 1.7 представлены форматы команд, иллюстрирующие задание различных способов адресации.

Поле reg постбайта используется для адресации тогда, когда в команде задаются два операнда. В этом случае второй операнд всегда находится в регистре, код которого указывается в поле постбайта в соответствии с табл. 1.1. В командах, где требуется только один операнд, поле reg постбайта используется совместно с байтом кода операции (КОП) для увеличения вариантов кодирования операций. Всего в ЦП используются восемь способов адресации, из которых пять реализуются с помощью постбайта. На рис. 1.7 представлены форматы команд, иллюстрирующие задание различных способов адресации.

Регистровая адресация.Операнд находится в одном из РОН, код которого указывается в байте КОП (рис. 1.7, а) или в постбайте при mod= 11 (рис. 1.7, б, в, д).

В командах с двумя операндами может быть использовано два регистра, причем код второго задается полем reg постбайта в соответствии с табл. 1.1. В командах, оперирующих словами, байт КОП содержит w=1и код регистра определяет один из восьми 16-разрядных регистров АХ-DI. В командах, операндами которых являются байты (w = = 0), код регистра определяет один из восьми 8-разрядных регистров AL-ВН в соответствии с табл. 1.1.

Непосредственная адресация.Операнд содержится в формате команды ввиде одно- или двухбайтовой константы (рис 1.7, а, б). Этот способ задается особой комбинацией значений разрядов в поле КОП и может быть использован в большинстве команд с двумя операндами. Такие команды имеют постбайт, что делает возможным выполнение операций над константой и операндом, расположенным в памяти или регистре. Способ непосредственной адресации неприменим в командах загрузки сегментных регистров и в команде занесения данных в стек. В этих случаях используется промежуточная загрузка константы в один из регистров, указанных в табл. 1.1.

В командах с однобайтовыми операндами (w = 0) операнд имеет длину 1 байт и располагается в конце команды (рис. 1.7, а, б) в поле данных. В командах с операндами-словами (w = 1) операнд обычно занимает поле данных длиной 2 байт (рис. 1.7, а). Однако некоторые команды с операндами-словами могут иметь однобайтовый операнд, что указывается с помощью присвоения 1-разрядному полю s значения 1 (рис. 1.7, б). Если 5 = 1, то однобайтовое поле данных, содержащееся непосредственно в команде, перед использованием в операции расширяется со знаком до 16-разрядного слова. Расширение со знаком позволяет использовать 16-разрядные операнды в диапазоне значений от -128 до +127, которые в команде записываются однобайтовым операндом вместо двухбайтового. Двухбайтовый операнд используется в случаях, когда значение требуемого операнда (константы) выходит за пределы указанного диапазона.

Прямая адресация.Исполнительный адрес операнда задается с помощью двух байтов, которые следуют за первым байтом (рис. 1.7, г) или за постбайтом (рис. 1.7,д). Младший байт адреса идет по порядку первым. Прямая адресация позволяет обращаться к операндам в пределах одного сегмента памяти емкостью 64К байт.

Возможна также длинная прямая адресация, при которой команда содержит 16-разрядный базовый адрес сегмента, а также 16-разрядное смещение в сегменте (исполнительный адрес), что позволяет при программировании осуществить обращение к операнду, находящемуся в произвольном (не текущем) сегменте, т. е. в пределах всей памяти емкостью в 1М байт. Однако такой способ прямой адресации применим только в командах переходов и командах вызова подпрограмм, в которых он позволяет осуществлять межсегментные переходы. Невозможность применения этого способа адресации в командах, задающих операции над данными, представляет определенное неудобство.

Косвенная регистровая адресация.Исполнительный адрес операнда содержится в одном из регистров ВХ, SI или DI, код которого задается в постбайте (рис. 1.7, б, в, д).

Адресация по базе.Реализуется сиспользованием постбайта, в котором указывается один из регистров ВХ, ВР или DI, содержащий 16-разрядный базовый адрес. Исполнительный адрес операнда формируется путем сложения этого базового адреса и 8- или 16-разрядного смещения, указанного в команде непосредственно за постбайтом (рис. 1.7,6); 8-разрядное смещение рассматривается как число со знаком, т. е. его значение лежит в диапазоне от -128 до +127. Использование адресации по базе позволяет осуществить доступ к элементам упорядоченных структур данных, когда смещение конкретного элемента данных известно, а базовый адрес структуры вычисляется по программе.

Адресация с индексированием. В формате команды непосредственно за постбайтом задается 16-разрядный базовый адрес, а в постбайте указывается один из регистров ВХ, ВР, SI или DI, в котором хранится индекс (рис. 1.7, д). Адресация с индексированием логически эквивалентна адресации по базе с 16-разрядным смещением. Различие заключается в том, что 16-разрядное смещение интерпретируется как базовый адрес, а регистр хранит индекс. Однако поскольку любой из указанных четырех регистров может применяться как при адресации по базе, так и • при адресации с индексированием, указанное различие является несущественным.

Адресация по базе с индексированием. Если в предыдущих способах адресации либо базы, либо смещения были фиксированы при выполнении команды и задавались в формате команды непосредственно, то адресация по базе с индексированием позволяет задавать оба этих параметра в регистрах (рис. 1.7,б,в). Это дает возможность вычислить во время выполнения программы как базовый адрес структуры данных, так и смещение одного из ее элементов.

Поскольку любой из регистров ВХ и ВР может использоваться в качестве базового, а любой из регистров SI и DI может служить индексным, имеется четыре различные комбинации регистров, которые могут реализовать адресацию по базе с индексированием. Кроме того, адресация по базе с индексированием может быть дополнена 8- или 16-разрядным смещением, которое является третьим слагаемым при вычислении исполнительного адреса ЕА; 8-разрядное смещение, как и ранее, рассматривается как число со знаком, находящемся в диапазоне от -128 до +127.

Относительная адресация. Исполнительный адрес вычисляется как сумма содержимого указателя команд IP и 8- или 16-разрядного смещения со знаком, заданного непосредственно в команде (рис. 1.7, е). Следует подчеркнуть, что в момент вычисления исполнительного адреса значение указателя команд IP равно адресу первого байта следующей команды. Способ относительной адресации так же, как и прямая адресация, имеет ограниченное применение и используется только в командах переходов, вызова подпрограмм и управления циклами.

В завершение рассмотрения различных способов адресации отметим, что исполнительные адреса ЕА, получаемые описанными выше способами, являются в действительности 16-разрядными смещениями в сегменте. Как было показано на рис. 1.3, 20-разрядный физический адрес получается путем сложения смещения в сегменте с предварительно сдвинутым на четыре разряда влево базовым адресом сегмента. Поскольку имеется четыре сегментных регистра CS, DS, SS и ES, для выполнения каждого преобразования логического адреса в физический должен быть выбран определенный регистр, содержащий базовый адрес соответствующего сегмента. Это осуществляют аппаратные средства микропроцессора, которые автоматически выбирают сегментный регистр согласно цели каждого обращения к памяти, как показано в табл. 1.2. В таблице указан также источник логического адреса, определяющий смещение в сегменте.

В ряде случаев для эффективной передачи данных между сегментами удобно извлекать операнды, находящиеся в стековом сегменте, не прибегая к операциям со стеком. Это относится, например, к извлечению параметров подпрограмм, которые находятся глубоко в стеке. Для подобных целей существует специальный вид обращения к памяти с использованием базового регистра ВР. Данные, для доступа к которым используется регистр ВР, выбираются из стекового сегмента, причем содержимое регистра SS служит в этом случае базовым адресом, а смещение задается исполнительным адресом ЕА, в формировании которого участвует содержимое регистра ВР.

Таблица 1.2

| Вид обращения к памяти | Сегментный регистр | Логический адрес |

| Выборка команды Операции со стеком Обращение к исходной строке Обращение к строке - результату ВР- базовый регистр Прочие обращения к переменной | CS SS DS* ES SS* DS* | IP SP SI DI EA EA |

Примечание. Знаком * отмечены регистры, которые могут быть заменены на любые сегментные регистры при смене сегмента памяти с помощью префикса замены.

При выполнении команд обработки данных может появиться необходимость адресовать операнды, находящиеся вне текущего сегмента, выбираемого процессором автоматически. Для этих целей, как уже отмечалось, применяется префикс замены сегмента, имеющий размерность 1 байт. Префикс помещается непосредственно перед байтом кода операции и содержит код сегментного регистра, используемого в качестве замены.

Одной из особенностей Intel 8086 является наличие двух режимов - максимального и минимального, существенно отличающихся по функциональным возможностям. Для минимального режима ЦП характерно использование только тех управляющих сигналов, которые вырабатываются непосредственно на выводах микросхемы.

Режим ЦП устанавливается путем соответствующего подключения вывода MN/MX к уровню «1» для минимального режима и к уровню «0» для максимального. В зависимости от выбранного режима изменяется назначение некоторых выводов ЦП. На рис. 1.8 приведены обозначения выводов микропроцессора, соответствующие минимальному режиму (MN/MX=1), а в табл. 1.3 указаны назначения выводов.

Режим ЦП устанавливается путем соответствующего подключения вывода MN/MX к уровню «1» для минимального режима и к уровню «0» для максимального. В зависимости от выбранного режима изменяется назначение некоторых выводов ЦП. На рис. 1.8 приведены обозначения выводов микропроцессора, соответствующие минимальному режиму (MN/MX=1), а в табл. 1.3 указаны назначения выводов.

|

Рис. 1.8. Условно-графическое обозначение микросхемы ЦП Intel 8086

Наиболее широко функциональные возможности обеспечиваются при использовании ЦП в максимальном режиме работы, который характеризуется тем, что вырабатываются дополнительные управляющие сигналы, обеспечивающие совместную работу центрального процессора с другими центральными процессорами или с сопроцессорами. Сопроцессоры берут на себя выполнение арифметических действий и реализацию обмена данными с внешними устройствами. Тем самым достигается существенное повышение производительности по сравнению с минимальным режимом.

Область применения ЦП в максимальном режиме и построенных на его основе ВМ определяется их способностью с большой скоростью выполнять сложные и высокоточные вычисления. При установке максимального режима изменяется назначение восьми выводов микропроцессора, что отражается в изменении их обозначений (рис. 1.8). На выходах s0, s1, s2 присутствует код состояния микропроцессора, характеризующий текущий цикл работы и определяющий способ использования ША/Д. Использование информации о состоянии ЦП позволяет в дальнейшем выработать все сигналы, необходимые для управления внешними устройствами ВМ.

Выводы RQ/GT0 и RQ/GT1 являются двунаправленными линиями, предназначенными для организации захвата системной шины другими устройствами. Вход запроса захвата RQ/GT0 имеет более высокий приоритет, а в остальном эти входы функционально эквивалентны. Захват начинается с поступления на один из входов RQ/GT запроса захвата шин длительностью в один такт от внешнего устройства (если запрос поступит одновременно на оба входа RQ/GT0 и RQ/GT1, то будет обслуживаться запрос по RQ/GT0). Во время очередного такта на этот вывод микропроцессор подает выходной сигнал, который информирует запросившее устройство о разрешении захвата. В следующем такте ЦП входит в режим захвата и устанавливает соответствующие выводы в высокоимпедансное состояние. По окончании использования системных шин ВУ информирует об этом ЦП сигналом освобождения шин, который также подается на вывод RQ/GT микропроцессора и имеет длительность 1 такт. Получив этот сигнал, ЦП возобновляет работу.

Таблица 1.3

| Обозначение вывода | Вход/выход | Назначение вывода |

| AD15-ADO | Вход/выход | Мультиплексированная ША/Д |

| AI6/S3-A19/S6 | Выход | Линии адреса или состояния |

| BHE/S7 | Выход | Разрешение старшего байта шины |

| RD | Выход | Управление чтением |

| WR | Выход | Управление записью |

| M/IO | Выход | Выбор памяти или ВУ |

| ALE | Выход | Разрешение фиксации адреса |

| DT/R | Выход | Управление пересылкой данных |

| DEN | Выход | Разрешение пересылки данных |

| MN/MX | Вход | Установка режима |

| TEST | Вход | Сигнал окончания режима ожидания |

| HOLD | Вход | Запрос захвата шин |

| HLDA | Выход | Подтверждение захвата |

| INTR | Вход | Запрос прерывания |

| NMI | Вход | Запрос немаскируемого прерывания |

| INTA | Выход | Подтверждение прерывания |

| READY | Вход | Готовность памяти или ВУ |

| RESET | Вход | Сброс (начальная установка) |

| CLK | Вход | Такты ГТИ |

| GND, +5 в | Вход | Общий (земля), питание |

Вывод LOCK, так же как и рассмотренные выводы RQ/GT0 и RQ/GT1, служит для организации взаимодействия ЦП с внешними устройствами. Активный сигнал LOCK=0 вырабатывается с помощью специальной команды и позволяет в случае необходимости запретить захват шин ЦП внешними устройствами. Выводы QS0 и QS1 несут информацию о состоянии очереди из байтов команд. Для декодирования сигналов состояния микропроцессора s0, s1, s2 в систему (при использовании ЦП в максимальном режиме) включается системный контроллер Intel 8288, позволяющий осуществить полную развязку управляющей, адресной и информационной шин, а также различение ВУ и ЗУ при обращении к этим устройствам. Это позволяет полностью реализовать возможности адресации, предусмотренные в ЦП, т. е. возможности обращения к 1М байт памяти и 64К байт портов ввода-вывода.

Дата добавления: 2015-12-22; просмотров: 1263;